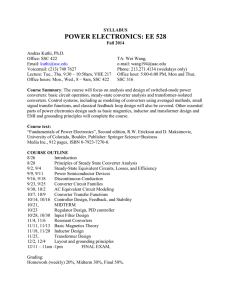

Electrical and Electronics Engineering

advertisement

1 IMPLEMENTATION OF A POSITIVE OUTPUT SUPERLIFT CONVERTER By Balaji Vasan Eshwar Nilakantan. C A thesis submitted to the FACULTY OF ELECTRICAL ENGINEERING In partial fulfillment of the requirements for the award of the degree of BACHELOR OF ENGINEERING In ELECTRICAL AND ELECTRONICS ENGINEERING COLLEGE OF ENGINEERING, GUINDY ANNA UNIVERSITY CHENNAI 600 025 APRIL 2006 2 BONAFIDE CERTIFICATE Certified that this thesis “DESIGN OF A POSITIVE OUTPUT SUPER-LIFT CONVERTER” is the bonafide work of Balaji Vasan (20021814) and Eshwar Nilakankan C (20021823) who carried out the project under my guidance. Certified further, that to the best of my knowledge the work reported herein does not form the part of any other thesis or dissertation on the basis of which a degree or award was conferred on an earlier occasion on this or any other candidates. Dr. R. ARUMUGAM Mr. C. Pugazhendi Sugumaran HOD Lecturer Department of Electrical and Department of Electrical and Electronics Engineering Electronics Engineering College of Engineering, Guindy College of Engineering, Guindy Anna University Anna University Chennai 600 025 Chennai 600 025 3 ABSTRACT Voltage lift technique is a popular method wildly used in electronic circuit design. It has been successfully employed dc-dc converter application in recent years and opened a way to design high voltage converters. However the voltage increases stage by stage along arithmetic progression. But with a super-lift converter, the output increases stage by stage along a geometric progression. Thus it effectively enhances the transfer gain in power series. Our main objective is to design a positive output super-lift converter, which is fired by pulses fed from TMS 320 LF 2407A DSP. The DSP Processor is used because of its high processing speed and other useful peripherals such as ADC units, PWM generation units and a flexible instruction set. This provides avenues for future enhancement of the project for a closed loop voltage control. The output of the converter is fed back to the processor through the ADC channels. The ADC output is compared with a pre-defined value and thus an error is generated. The duty cycle of the driving PWM signal is changed accordingly and fed to the MOSFETs. 4 ACKNOWLEDGEMENT We wish to express our sincere thanks to Mr. K. Pugazhendi Sugumaran, Lecturer, Department of Electrical and Electronics Engineering for his guidance, support and motivation offered to us throughout the course of the project work. We express our sincere thanks and deepest sense of gratitude to Mrs. K. Latha, Senior Lecturer, Department of Electrical and Electronics Engineering for her valuable guidance in helping us conceive the basic idea of this project We wish to thank Dr.R.Arumugam, Director, Department of Electrical and Electrical Engineering for providing us the necessary facilities to carry out the project work. Our heartfelt thanks to Mr. Senthil Kumar, Lecturer, AC Tech for assisting us with the use of processor. We would like to thank Mr. R.Giridharan, Mr. Samikannu and Mr.Balraj for providing us the necessary assistance from the laboratories Finally we would like to thank all others who in one way or the other helped us in the completion of this project. 5 CHAPTER 1 Overview 2.1 Introduction DC to DC converters are important in portable electronic devices such as cellular phones and laptop computers, which are supplied with power from batteries. Such electronic devices often contain several subcircuits which each require unique voltage levels different than supplied by the battery (sometimes higher or lower than the battery voltage, or even negative voltage). Additionally, the battery voltage declines as its stored power is drained. DC to DC converters offer a method of generating multiple controlled voltages from a single variable battery voltage, thereby saving space instead of using multiple batteries to supply different parts of the device. 1.2 DC-DC Conversion Methods DC- DC conversion can be done in two ways: Linear Conversion: A simple method of converting one voltage to another is a circuit known as a voltage divider. This technique uses resistors in series with the voltage supply to provide a lower voltage. Switched Mode Conversion Switch-mode DC to DC converters are very similar to a switched-mode power supply, generally perform the conversion by applying a DC voltage across an inductor or transformer for a period of time (usually in the 100 kHz to 5 MHz range) which causes current to flow through it and store energy magnetically, then switching this voltage off and causing the stored 6 energy to be transferred to the voltage output in a controlled manner. By adjusting the ratio of on/off time, the output voltage can be regulated even as the current demand changes 1.3 Positive Output Super-Lift Luo Converters Luo converters are DC-DC Switching Mode Boost converters. A boost converter (step-up converter) is a power converter with an output dc voltage greater than its input dc voltage. Luo converters are a class of converters providing a high gain with relatively lesser number of components. Although Luo converters provide a high gain, when cascaded, the gain increases stage by stage only in Arithmetic Progression. In order to solve this discrepancy in the Classical Luo Converters, anther class of converters called Super-lift Luo Converters were developed. While the positive aspects of the Classical Luo Converters are retained in Super-lift converters, Super-lift converters also have the advantage that the gain in this converter increases in geometric progression, stage by stage. 1.4 Objective The main objective of this thesis is to design and implement a Positive Output Super-lift converter triggered using DSP TMS 320 LF 2407A and control its operation in the Closed Loop 1.5 Organization of the thesis This thesis comprises of five chapters with the introduction as the first chapter. The Luo converters and their operation are explained in the second chapter. The third chapter deals with the open loop implementation of the Super-lift converter. The fourth chapter describes the closed loop implementation of the circuit. The sixth chapter comprises of the results and conclusion. The Appendix gives an insight of the various features of the DSP processor used. 7 CHAPTER 2 Positive Output Luo Converters 2.1 Introduction The voltage lift technique is a popular method that is widely applied in electronic circuit design. Because of the effect of parasitic elements, the output voltage and power transfer efficiency of DC–DC converters are limited. The voltage lift technique opens a good way to improve circuit characteristics. After long-term research, this technique has been successfully applied for DC–DC converters. With the increased use of DC-DC converters, Voltage-lift converters have opened up new avenues of applications for DCDC converters because of their high voltage gain. 2.2 Positive Output Voltage-lift Luo Converters Micro-power-consumption technique requires high power density DC/DC converters and power supply source. Voltage lift technique is a popular method to apply in electronic circuit design. Combining switched-capacitor and voltage lift technique, DC/DC converters with small size, high power density, high voltage transfer gain, high power efficiency can be constructed. Positive output Luo converters (also called ‘Classical Luo Converters’) are a series of new DC–DC step-up (boost) converters, which were developed from prototypes using voltage lift technique. These converters perform positive-to-positive DC–DC voltage increasing conversion with high power density, high efficiency and cheap topology in simple structure. They are different from other existing DC–DC step-up converters and possess many advantages including a high output voltage with small ripples. Therefore, these converters can be used in computer peripheral equipment and industrial applications, especially for high output voltage requirements. 8 2.3 Classical Luo Converters 2.3.1 Circuit (Single Stage Voltage Lift Converter or Self Lift Converter) The circuit of a single stage Voltage-lift Luo converter is shown in fig. 2.1 Figure 2.1 Self-Lift Converters 2.3.2 Working Equivalent circuit when switch is ON and OFF is shown in figures 2.2a and 2.2b respectively. 9 Figure 2.2a – Self Lift Converter – Switch ON When switch S is on, the instantaneous source current (i1) is the sum of the two-inductor currents (iL1 and iL2) and the current through capacitor C2 (iC2). Inductor L1 absorbs energy from the source. In the mean time inductor L2 absorbs energy from the source and capacitor C1. Both currents iL1 and iL2 increase. Capacitor is charged to voltage V1. Figure 2.2b Self Lift Converter – Switch OFF 10 When switch S is off, the instantaneous source current i1 is zero. Current iL1 flows through capacitor C2 and diode D to charge capacitor C1. Inductor L1 transfers its stored energy to capacitor C1. In the mean time, current iL2 flows through (C0-R) circuit, capacitor C2 and diode D, to keep itself continuous. Both currents iL1 and iL2 decrease. 2.3.3 Gain Let the duty ratio be ‘k’ and time period of switching be ‘T’. Current iL1 increases in switch-on period kT, and decreases in switch-off period (1-k) T. The corresponding voltages applied across L1 are V1 and –(Vc-V1) respectively. Therefore, KTV1 = (1-K) T (Vc-V1) Hence, Vc/V1 = (1/(1-k)) Current iL2 increases during switch-on period kT, and decreases during switch-off period (1-k) T. The corresponding voltages applied across L2 are (V1+Vc-V0) and –(V0-V1). Therefore, kT (Vc+V1-V0) = (1-k) T (V0-V1) Hence, 11 2.4 Super-lift Converter Classical Voltage lift converters offer a high gain. However, when the circuit is constructed for multi-stage operations, gain increases stage by stage in arithmetic progression. Super-lift converters are more powerful converters than the classical converters. In super-lift converters, the gain increases stage by stage in geometric progression. Thus, the voltage transfer gain is effectively enhanced in the power series. 2.4.1 Circuit The circuit of a single stage Super-lift converter is shown in figure 2.3 Figure 2.3 Superlift converter single stage 2.4.2 Working The equivalent circuit during switch ON and OFF is shown in figures 2.4a and 2.4b respectively. 12 Figure 2.4a Superlift converter Single stage – Switch ON During the switch-on period, the voltage across capacitor C1 is charged to Vin. The current through inductor L1 increases with the voltage Vin. Figure 2.4b Superlift converter Single stage – Switch OFF During the switch-off period, the current through the inductor decreases. The capacitor C2 is charged through Vin, VC1 and VL1. 13 2.4.3 Gain The ripple of the inductor current iL1 is ∆ iL1 = (Vin/L1) kT = ((V0-2Vin)/L1)(1-k) T V0 = ((2-k)/(1-k)) Vin Therefore, the voltage transfer gain is As seen, the gain for a single stage is greater than that obtained for classical VL converters. This can be clearly observed in the graph shown in figure 2.5: 7 6 Gain for Single stage classical converter Gain 5 4 Gain for Single stage superlift converter 3 2 1 0 0 0.2 0.4 0.6 0.8 1 Duty Cycle (k) Figure 2.5 Gain Comparison 1 14 2.5 Two stage Super-lift converter (Re-Lift Converter) The super-lift converter can be cascaded to obtain large gain. The circuit of a two-stage cascaded super-lift converter is shown in figure 2.6. Figure 2.6 Superlift converter two stage 2.5.2 Working The working of the re-lift circuit is similar that of the self-lift circuit. In this type, the output of the first stage is supplied as the input to the next stage. The equivalent circuits when the switch S is ON and OFF are shown in figure 2.7a and 2.7b respectively. 15 Figure 2.7a Superlift converter two stage – Switch ON During switch ON, capacitor C1 is charged to input voltage Vin. Also the capacitor C3 is charged to the intermediary output voltage V1. The current through the inductor L1 increases with Vin. The current through L2 increases with V1. Figure 2.7b Superlift converter two stage – Switch OFF 16 During the switch-off period, the current through the inductors decreases. The capacitor C2 is charged through Vin, VC1 and VL1. The capacitor C4 is charged through V1, VC3 and VL2. 2.5.3 Gain The ripple of the inductor current iL1 is ∆iL1 = (Vin/L1) kT = ((V1-2Vin)/L1)(1-k) T V1 = ((2-k)/(1-k))Vin The ripple of the inductor current iL2 is ∆iL2 = (V1/L2)kT = ((V0-2V1)/L2)(1-k)T V0 = ((2-k)/(1-k))V1 Therefore, The comparison of the gain of a two stage super-lift converter and a single stage classical converter is shown in figure 2.8 17 Gain 20 18 16 Gain for Single stage classical converter 14 12 10 8 6 Gain for twostage superlift converter 4 2 0 0 0.2 0.4 0.6 0.8 Duty Cycle (k) Figure 2.8 Gain Comparison 2 2.6 N-stage super-lift converter As in a relift circuit, n-stage Superlift converter can be constructed by cascading n-selflift circuits. The resultant gain is given as below: 2.7 Conclusion This chapter discussed the basic working of super-lift converters and classical converters. The difference in the gain was evident. The two-stage super-lift converter was also discussed. The voltage transfer gain in each case was also discussed. 18 CHAPTER 3 Open Loop Implementation using DSP Processor 3.1 Introduction The implementation was carried out in two phases. The first phase was the software simulation and the next phase was the hardware realization. The software simulation was carried out with the help of PSPICE. It is a computer program that allows the user to perform simulations of electric and electronic circuits. To generate the pulses for the hardware circuit TMS320C2407 Digital Signal Processor was used. 3.1.1 BENEFITS OF THE DSP CONTROLLERS Favors system cost reduction by an efficient control in all speed range implying right dimensioning of power devices. Performs high-level algorithms due to reduced torque ripple, resulting in lower vibration and longer life. Decreases the number of look up tables, which reduces the amount of memory required. It offers high speed, high resolution and capabilities to implement the mathintensive algorithms to lower the system cost. Enables reduction of harmonics using enhanced algorithms, to meet easier requirements and to reduce the converter cost. 3.2 CONTROL SYSTEM BLOCK The figure 3.1 shows the overall block diagram of the open loop circuit which contains a dc supply, converter block, a load and the controller block. 19 Fig.3.1 Basic Building Blocks of Re-Lift Circuit The block diagram shown in the Fig.3.1 is the Re-lift converter. The converter block consists of two stages of super lift converters. The load is a resistive load. The controller block consists of a DSP processor (TMS320C2407) and a driver circuit. The controller block generates the appropriate pulse to fire the MOSFET. Here the driving circuit used is a Darlington pair circuit .The DSP Processor is used to provide the pulses to trigger the MOSFET. But the output from the processor is not sufficient enough to drive the MOSFET and hence the Darlington pair is used to raise the level of the output from the DSP Processor sufficient enough to drive the MOSFET. The Darlington pair consists of two transistors connected as shown in the Fig.3.2 . 20 Fig.3.2 shows the Darlington pair circuit configuration. The circuit consists of two transistors (SN 100), two 1k resistors and a reference power supply. The output is taken from the collector of the second transistor and given as the gate drive for the MOSFET. 3.3 CIRCUIT DETAILS The circuit was simulated using PSPICE with the following specifications: DC Supply - 5V Pulse Generator Specifications: Frequency - 50 kHz Fall time - 1ns Rise time - 1ns Period - 20us Pulse Width - 10us Capacitance - 2uF Inductance - 10mH The Fig.3.3 represents the circuit configuration of the Re-lift circuit. The Re-lift circuit is obtained by adding two single stage circuits. The circuit consists of two static switches, four diodes, and four capacitors. As we see the Re-Lift circuit is derived from the elementary circuit by adding the parts (L2-D3-D4-C3-C4). In the simulation instead of a Digital Signal Processor we use a V pulse generator. 21 For the circuit in figure 3.3, the duty cycle of the pulse is chosen as ‘k’. The gain for the Re-lift circuit with duty ratio ‘k’ is given as, 3.4 SIMULATION RESULTS The simulation of the circuit shown in Fig.3.3 was carried out using PSPICE software. The input and output waveforms are shown in the Fig.3.4. Here the circuit parameters were chosen as specified in the circuit configuration. 22 Figure 3.4 Simulation Result – Output Voltage From the simulation we see that the output voltage is 32V for an input of 5. As we see the gain in the practical case is 6.4 against a practical gain of 9 (((2-0.5)/(1-0.5))2 = 32 = 9) The inductor currents flowing in the circuit during its operation is shown in figures 3.4 and 3.5. 23 Figure 3.5a Simulation Results - Current through inductor L1 Figure 3.5b Current through inductor L2 24 3.5 HARDWARE REALIZATION The hardware circuit consisted of The Darlington pair: This circuit was realized using two transistors (SN100), two resistors (1kΩ) and a RPS (Regulated Power Supply) to provide the biasing voltage. The Re-Lift Converter: This circuit was realized using four diodes (), two MOSFETs (IRF850), four capacitors (2uF) and two inductance boxes (10mH) and a regulated DC supply. The Digital Signal Processor: The DSP Processor was used with the help of the processor kit which was interfaced to the personal computer. 3.5.1 Hardware Result For an input of 5V, the output obtained was around 31V and this is comparable with the value obtained from the simulation of the circuit using PSPICE. 3.6 Conclusion The circuit of a two-stage Superlift converter (Re-lift converter) was successfully simulated and simulation results were satisfactory. The circuit was also implemented in hardware and the results were also close to those obtained in the simulation. The DSP processor was also coded successfully to generate the required pulses 25 CHAPTER 4 CLOSED LOOP IMPLEMENTATION USING DSP PROCESSOR 4.1 Introduction The main objective of the closed loop implementation is to achieve a robust control for the output voltage. In other words, the primary aim is to maintain the output voltage a constant irrespective of the input supply variations. 4.2 Block Diagram The block diagram of the closed loop implementation is shown in the figure 4.1 Figure 4.1 Basic Building Blocks for closed loop control As observed the output of the converter is fed back to the controller circuit. As explained earlier, the controller is realized using the DSP processor. The output is fed back to the processor through the ADC module. Input to the ADC module must be in the range 03.3V. In order that the voltage is within this range, the output voltage from the load is stepped down using a potential divider. The DSP processor compares the ADC output with a pre-defined value and generates an error signal. Based on this error the control action is taken. 26 4.3 Closed Loop Algorithm The algorithm used for achieving the closed loop is as follows: 1. Start 2. Configure the various registers and the pins as per the requirement 3. Initialize the timer module to generate pulses with a duty cycle of 0.5. 4. Execute a delay routine so that the converter output reaches its steady state output value. 5. Sample the output (after stepping it down to a value acceptable by the processor) 6. Store the ADC output in one of the registers and calculate the error (Pre-specified value – Sampled value) 7. If there is a positive error, the output voltage is lesser than the reference value. So increase the duty cycle. 8. If there is a negative error, the output voltage is greater than the reference value. So decrease the duty cycle. 9. Repeat steps 4 to 8 till the desired output is obtained. 10. End 4.4 Algorithm Implementation The algorithm explained in section 4.3 was implemented using the DSP processor. However the gain in the closed loop control was varied only in the range of 0.4-0.6. 4.5 Conclusion Closed loop control was successfully implemented and satisfactory results were obtained. 27 Chapter 5 Conclusion 5.1 Introduction This chapter discusses the various results of the project. Scopes of further developments in the project is also given. 5.2 Summary of Results The positive output super-lift converter was successfully implemented and controlled in both open loop and closed loop. The super-lift converter was simulated using Pspice software and a gain of 6.6 was obtained against the theoretical gain of 9 The circuit was implemented in the hardware and the real-time results matched the simulation results. The DSP processor was coded successfully to generate PWM pulses for the open loop implementation The closed loop algorithm was developed and successfully implemented using the DSP processor. 5.3 Future scope The closed loop implementation of the circuit varies the duty cycle of the switching pulses only between a small range of 0.4 and 0.6. Varying the duty cycle over a larger range can make the closed loop control more robust. Also the two MOSFETs are fired from the same source. Firing hem separately from two different sources help in finetuning the gain obtained. 28 Appendix 1 DSP PROCESSOR TMS 320 LF 2407A A1.1 INTRODUCTION The TMS 320 LF 2407A is a member of the TMS320 family of digital signal processors. DSP controllers combine real time processing capability with controller peripherals to create an ideal solution for control system applications. Very flexible instruction set, inherent operational flexibility, high-speed performance, innovative parallel architecture and cost effectiveness are the highlighting features of DSP controllers. A1.2 TMS 320 LF 2407A PROCESSOR The TMS 320 LF 2407A processor works at 40 MHz with Micro-2407A. It has 544 words of on-chip data/program dual access RAM and 32K words of on-chip flash EEPROM. It has on-chip serial ports, which can be employed. It is capable of performing 32 bit arithmetic operations with the ALU and the accumulator and has an 8word long auxiliary register file, with a separate ALU for the same. Its instruction set has specific instructions for adaptive filtering, FFT and extended precision arithmetic and supports bit-reversed indexed addressing mode for FFTs. The TMS320F2407A is capable of addressing 64K Words of data memory and an equal amount of program. This trainer based on TMS320F2407A, has program EPROM of 48K words, 16K Words of external program RAM, 32K words of external data RAM and the entire external RAM being accessed at 0 wait state. The data can be expanded to the maximum 128K words and optionally can be accessed by bank switch. 29 MICRO-2407A, is, the 16-bit Fixed Point DSP trainer, based on Texas Instruments TMS 320 LF 2407A. Embedded peripherals inside Micro-2407A are: Two Event Manager General purpose timers Analog to Digital converter Control Area Network interface Serial peripheral interface Serial communications interface General purpose digital I/O pins Watch dog timer Phase locked loop module Interrupt module A1.3 FEATURES FOR TMS 320 SERIES A1.3.1 CPU: The CPU of TMS 320 series has a 32-bit central arithmetic logic unit (CALU) and a 32bit accumulator. It is capable to have 32-bit product with the help of 16-bit X 16-bit parallel multiplier. Eight 16-bit auxiliary registers with a dedicated arithmetic unit for indirect addressing of data memory are also available. A1.3.2 MEMORY: The memory unit has 544 WORDS X 16-bits of on-chip data / program dual-access RAM, 32K words X 16-bits of on-chip program ROM or flash EEPROM and 192k words X 16-bits of maximum addressable memory space (64K words of each program/data space and 32K words of global space). It also has external memory interface module with a software wait-state generator, a 16-bit address bus, and a 16-bit data bus. 30 A1.3.3 INSTRUCTION CONTROL: A 4-level pipeline operation associated with 8-level hardware stack provides flexible instruction control. Power-drive protection, interrupts, reset, NMI and three maskable interrupts are the six external interrupts provided in TMS 320 series. A1.3.4 INSTRUCTION SET: The source code is compatible with 'C2x, 'C2xx, and 'C5x fixed-point generation of the TMS320 family. The multiply/accumulate instructions take only a single cycle to complete. Indexed-addressing capability, Single-instruction repeat operation and Memory block move instructions for program/data management are some of the other features of this instruction set. For radix-2 Fast Fourier Transforms (FFTs) the bit-reversed indexedaddressing capability of the instruction set can be used. A1.3.5 POWER: Static CMOS Technology is used in the design of the processor. Four power-down modes are available to reduce power consumption. A1.3.6 SPEED: The DSP has the capacity to process 40 Million Instructions Per Second (25ns instruction cycle time), with most instructions single cycle. A1.3.7 EVENT MANAGER: There are two event manager A and B. 8 Compare/pulse-width modulation (PWM) channels (6 independent) Four 16-bit general-purpose timers with six modes including continuous up counting and continuous up/down counting. Six 16-bit full compare units with dead band capability. Two 16-bit simple compare units. 31 Six capture units, four of which have quadrature-encoder-pulse-interface capability. A1.3.8 ADC Module ADC module has 10-bit Analog-to-Digital converter with built in sample and hold circuits. 16 multiplexed analog inputs Two independent 8 state sequencers Four sequence control registers 16 Result registers to store conversion results A1.4 SPECIFICATIONS 1. PROCESSOR: CPU: Texas Instruments TMS320LF2407A CLK FREQUENCY: 40Mhz WAIT STATES: 2 for EPROM, 0 for RAM 8 for LCD DISPLAY and 0 for SERIAL PORT 2. MONITOR (EPROM): 0000 - BFFF for 48KW 3. MEMORY: PROGRAM RAM: C000 - FFFF for 16 KW DATA RAM: 8000 - FFFF for 32 KW, expandable up to 64 KW (two banks), (9000 to 1FFF reserved area). 32 4. SERIAL: One RS232C Serial Interface using On-chip SERIAL COMMUNICATION INTERFACE (SCI) module 5. TIMER: On-chip timer can be used. 6. INTERRUPTS: 5 Interrupt lines are available 7. IBM AT KEY BOARD: On-board IBM AT keyboard Interface 8. DISPLAY: 16x2 LCD display (For Mode-2) 9. ON-BOARD BATTERY BACKUP: Onboard battery backup facility is provided for DATA, PROGRAM & I/O RAM. 10. SYSTEM POWER CONSUMPTION: + 5V: 1.5 Amps + 12V: 100 mA -12 V: 100 mA 11. POWER SUPPLY (LPOW-001A) SPECIFICATIONS: Mains: 230 Volts AC at 50Hz Outputs: 1. + 5 Volts, 3.5 Amps Regulated 2. + 12 Volts, 150 ma Regulated 33 3. -12 Volts, 150 ma Regulated 12. PHYSICAL CHARACTERISTICS: Micro-2407A PCB: Weight: A1.5 264mm x 195mm 1 Kg FUNCTIONAL BLOCKS OF 2407 A1.5.1 INPUTS AND OUTPUTS OF THE CPU: The CPU gets the clock from the clock generator logic, which uses an oscillator at 10 MHz. The reset, interrupt lines, ready and the data lines are inputs to the CPU. The CPU outputs include the address lines, data lines, control lines, clock output and the signals comprising the serial port interface. A1.5.2 ADDRESS AND DATA BUS: The 16- bit data bus and the 16- bit address bus are given to data transceivers and octal buffers. They are qualified by the R/W and STRB. The output of these buffers and latches comprise the system Data bus (D0-D15) and Address bus (A0-A15). A1.5.3 CONTROL BUS: The other bus is the control bus. The control signals required for proper operation of the system are the Read and Write signals for the memory devices, and the Read and Write signals for the I/O devices. Again, since the processor is capable of accessing memory as separate data and program spaces, the signals, PS, DS AND r/w are used to generate the proper read and write enable signals for all the devices. The entire logic is implemented using TTL MSI devices. 34 A1.5.4 CHIP SELECT LOGIC: The selection of any peripheral or memory requires a CS to enable that particular device. This requires address decoding. The decoding sections present in the trainer board implement memory and I/O decoding to map the memory devices and the various peripherals at specific address locations in the CPU address space. A1.5.5 WAIT STATE LOGIC: Since all the memory and peripherals operate at access speeds that are very low as compared to CPU read/write timings, the introduction of wait states to accommodate the operation of these slow devices on the CPU bus is imperative. This has been accomplished by programming software wait state registers. The processor works at two wait states for monitor EPROM, zero wait state for RAM & eight wait states for chip select. A1.5.6 KEYBOARD AND DISPLAY: The 104-keys AT keyboard is interfaced to the CPU with the help of CD4015 keyboard controller. The 16x2 LCD display is interfaced to the CPU through the 74LS244 latch. A1.5.7 MEMORY: 48 KW of Monitor EPROM, 16KW of program RAM, 32KW of Data RAM & are provided in the basic trainer. Program RAM & Data RAM can be expanded up to 32KW and 64KW respectively. 35 A1.5.8 ANALOG TO DIGITAL CONVERTER: The ADC is a 10-bit string/capacitor converter with internal sample and hold circuitry. The ADC module consists of two 10-bit ADCs with two built-in-sample and hold circuits. A total of 16 analog input channels are available on the TMS320F2407A to interface the real time process by the circuit based on AD8582 which has two output channels, A1.5.9 EVENT MANAGER: The Event Manager (EV) Module provides a broad range of functions and; features that are particularly useful in motion-control and motor control applications. There are two event manager each generates 8 PWM / couple outputs. A1.5.10 Watch dog and Read-Time Interrupt Module: Most conditions that temporarily disrupt chip operation and inhibit proper CPU function can be cleared and reset by the watchdog function. By its consistent performance, the watching increases the reliability of the CPU, thus ensuring system integrity. The watchdog (WD) and real-time interrupt (RTI) module monitors software and hardware operation, provides interrupts at programmable intervals, and implements system reset function upon CPU disruption. If the software goes into an improper loop, or if the CPU becomes temporarily disrupted, the WD timer overflows to assert a system reset. A1.6 Conclusion The functional features and embedded interface of the TMS 320 LF 2407A PROCESSOR was discussed in this Appendix 1. 36 Appendix 2 Program A2.1 Open loop program .INCLUDE 2407REGS.H .TEXT NOP START: SPM 0 SETC INTM ;DISABLE INTERRUPTS SPLK #0000H,IMR ;MASK ALL CORE INTERRUPTS LACC IFR ;READ INTERRUPT FLAGS SACL IFR ;CLEAR ALL INTERRUPT FLAGS CLRC SXM ;CLEAR SIGN EXTENSION MODE CLRC OVM ;RESET OVERFLOW MODE CLRC CNF ;CONFIG BLOCK B0 TO DATA MEM LDP #00E0H SPLK #006FH, WDCR ;DISABLE WD IF VCCP=5V (JP5 IN POS. 2-3) KICK_DOG ;RESET WATCHDOG LDP #0E0H SPLK #0FCH,SCSR1 ;CLKOUT=CLKIN * 4--40 MHZ LDP #150h SPLK #0092h,0 OUT 0, 0FFFFH ;;SETUP I/O PORTS;; LDP #225h SPLK #03FFFH,MCRA SPLK #0,mcrc 37 T1CMPR .SET 200 T1PRD .SET 400 LDP #232h SPLK #T1CMPR,CMPR1 SPLK #T1CMPR,CMPR2 SPLK #T1CMPR,CMPR3 SPLK #0999h,ACTRA SPLK #8200h,COMCONA SPLK #T1PRD,T1PR SPLK #0000h,T1CNT SPLK #0000h,T2CNT SPLK #0000h,T3CNT SPLK #0802h,T1CON SPLK #0000h,T2CON SPLK #0000h,T3CON SPLK #0842h,T1CON END: B END A2.2 Closed Loop Program .INCLUDE 2407REGS.H .TEXT NOP START: SPM 0 SETC INTM ;DISABLE INTERRUPTS SPLK #0000H,IMR ;MASK ALL CORE INTERRUPTS LACC IFR ;READ INTERRUPT FLAGS SACL IFR ;CLEAR ALL INTERRUPT FLAGS CLRC SXM ;CLEAR SIGN EXTENSION MODE CLRC OVM ;RESET OVERFLOW MODE 38 CLRC LDP CNF ;CONFIG BLOCK B0 TO DATA MEM #00E0H SPLK #006FH, WDCR ;DISABLE WD IF VCCP=5V (JP5 IN POS. 2-3) KICK_DOG ;RESET WATCHDOG LDP #0E0H SPLK #0FCH,SCSR1 ;CLKOUT=CLKIN * 4--40 MHZ LDP #150h SPLK #0092h,0 OUT 0, 0FFFFH LDP #225h SPLK #03FFFH,MCRA SPLK #0,mcrc T1CMPR .SET 200 T1PRD .SET 400 LDP #232h SPLK #T1CMPR,CMPR1 SPLK #T1CMPR,CMPR2 SPLK #T1CMPR,CMPR3 SPLK #0999h,ACTRA SPLK #8200h,COMCONA SPLK #T1PRD,T1PR SPLK #0000h,T1CNT SPLK #0000h,T2CNT SPLK #0000h,T3CNT SPLK #0802h,T1CON SPLK #0000h,T2CON SPLK #0000h,T3CON SPLK #0842h,T1CON ;;ADC MODULE;; 39 ATEMP .SET 0 A .SET 1 AVALUE .SET 0099h CONV: LDP #150h SPLK #0,ATEMP LDP #225h SPLK #0400h,ADCCTRL1 NOP SPLK #0,MAXCONV SPLK #0008h,CHSELSEQ1 LDP #225 SPLK #0480h,ADCTRL1 NOP SPLK #4000h,ADCTRL2 NOP SPLK #2000H,ADCTRL2 RPT #8 NOP LOOP: BIT ADCTRL2,BIT12 BCND LOOP,TC RPT #4 NOP LDP #150 BLDD #RESULT0,ATEMP LACC ATEMP,10 SACH ATEMP LDP #150 LACC ATEMP SUB #AVALUE 40 BCND END,EQ BCND NEG,NC POS: LDP #232h LACC CMPR1 ADD #5 SACL CMPR1 SUB #250 BCND END,NC B CONV NEG: LDP #232h LACC CMPR1 SUB #5 SACL CMPR1 SUB #150 BCND END,C B CONV END: B END 41 Appendix 3 Hardware Implementation Figure A3.1 Converter implementation 42 Figure A3.2 Converter with DSP processor interfacing 43 LIST OF ABBREVIATIONS USED DC Direct Current DSP Digital Signal Processor ROM Read Only Memory RAM Random Access Memory EEPROM Electrically Erasable Programmable Read Only Memory ALU Arithmetic and Logic Unit ADC Analog to Digital Converter CPU Central Processing Unit CALU Central Arithmetic and Logic Unit I/O Input/Output WD Watch Dog Timer EVM Event Manager Module SYSCLK System Clock PWM Pulse Width Modulation MOSFET Metal Oxide Semiconductor Field Effect Transistor CMOS Complementary Metal Oxide Semiconductor GND Ground