Multiformat 216 MHz

Video Encoder with Six NSV® 12-Bit DACs

ADV7320/ADV7321

High definition (HD) input formats

16-/20-, 24-/30-bit (4:2:2, 4:4:4) parallel YCrCb

Fully compliant with

SMPTE 274M (1080i, 1080p @ 74.25 MHz)

SMPTE 296M (720p)

SMPTE 240M (1035i)

RGB in 3-bit × 10-bit 4:4:4 input format

HDTV RGB supported

RGB, RGBHV

Other HD formats using async timing mode

Enhanced definition (ED) input formats

8-/10-, 16-/20-, 24-/30-bit (4:2:2, 4:4:4) parallel YCrCb

SMPTE 293M (525p)

BTA T-1004 EDTV2 (525p)

ITU-R BT.1358 (625p/525p)

ITU-R BT.1362 (625p/525p)

RGB in 3-bit × 10-bit 4:4:4 input format

Standard definition (SD) input formats

CCIR-656 4:2:2 8-/10-bit or 16-/20-bit parallel input

HD output formats

YPrPb HDTV (EIA 770.3)

RGB, RGBHV

CGMS-A (720p/1080i)

ED output formats

Macrovision® Rev 1.2 (525p/625p) (ADV7320 only)

CGMS-A (525p/625p)

YPrPb progressive scan (PS) (EIA-770.1, EIA-770.2)

RGB, RGBHV

SD output formats

Composite NTSC M/N

Composite PAL M/N/B/D/G/H/I, PAL-60

SMPTE 170M NTSC-compatible composite video

ITU-R BT.470 PAL-compatible composite video

S-video (Y/C)

EuroScart RGB

Component YPrPb (Betacam, MII, SMPTE/EBU N10)

Macrovision Rev 7.1.L1 (ADV7320 only)

CGMS/WSS

Closed captioning

GENERAL FEATURES

Simultaneous SD/HD or PS/SD inputs and outputs

Oversampling up to 216 MHz

Programmable DAC gain control

Sync outputs in all modes

On-board voltage reference

Six 12-bit NSV (noise shaped video) precision video DACs

2-wire serial I2C® interface, open-drain configuration

Dual I/O supply 2.5 V/3.3 V operation

Analog and digital supply 2.5 V

On-board PLL

64-lead LQFP package

Lead (Pb) free product

APPLICATIONS

EVD (enhanced versatile disk) players

High-end SD/PS DVD recorders/players

SD/PS/HDTV display devices

SD/HDTV set top boxes

Professional video systems

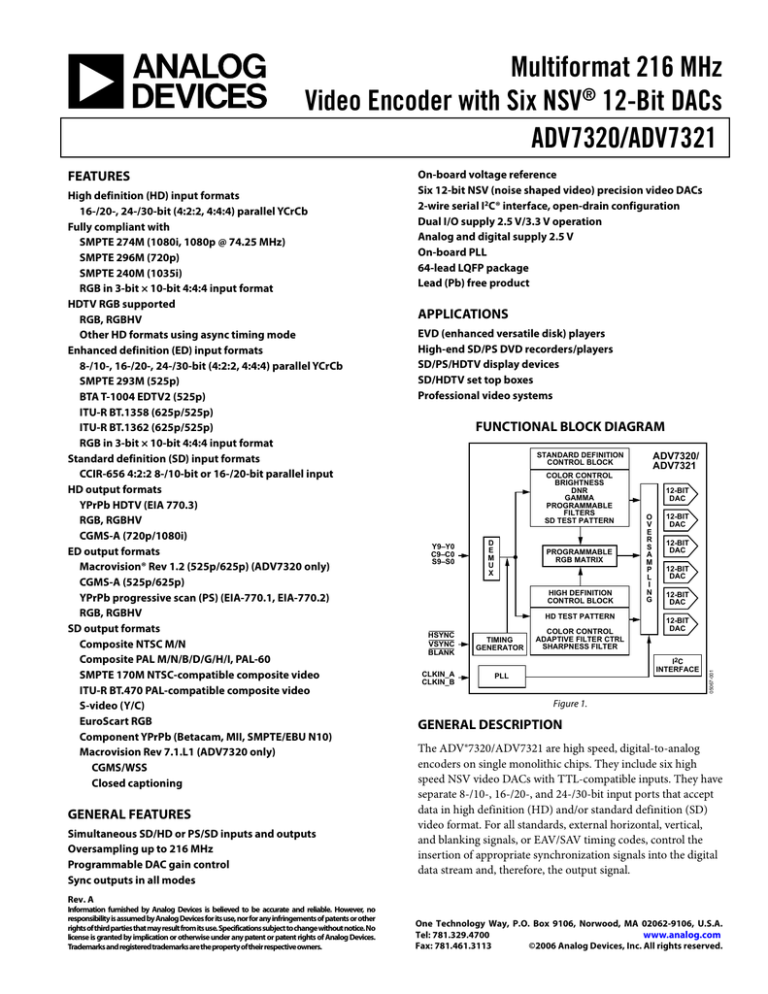

FUNCTIONAL BLOCK DIAGRAM

Y9–Y0

C9–C0

S9–S0

D

E

M

U

X

STANDARD DEFINITION

CONTROL BLOCK

ADV7320/

ADV7321

COLOR CONTROL

BRIGHTNESS

DNR

GAMMA

PROGRAMMABLE

FILTERS

SD TEST PATTERN

12-BIT

DAC

PROGRAMMABLE

RGB MATRIX

HIGH DEFINITION

CONTROL BLOCK

HD TEST PATTERN

HSYNC

VSYNC

BLANK

CLKIN_A

CLKIN_B

TIMING

GENERATOR

COLOR CONTROL

ADAPTIVE FILTER CTRL

SHARPNESS FILTER

O

V

E

R

S

A

M

P

L

I

N

G

12-BIT

DAC

12-BIT

DAC

12-BIT

DAC

12-BIT

DAC

12-BIT

DAC

I2C

INTERFACE

PLL

05067-001

FEATURES

Figure 1.

GENERAL DESCRIPTION

The ADV®7320/ADV7321 are high speed, digital-to-analog

encoders on single monolithic chips. They include six high

speed NSV video DACs with TTL-compatible inputs. They have

separate 8-/10-, 16-/20-, and 24-/30-bit input ports that accept

data in high definition (HD) and/or standard definition (SD)

video format. For all standards, external horizontal, vertical,

and blanking signals, or EAV/SAV timing codes, control the

insertion of appropriate synchronization signals into the digital

data stream and, therefore, the output signal.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

ADV7320/ADV7321

TABLE OF CONTENTS

Features .............................................................................................. 1

Reset Sequence ........................................................................... 45

General Features ............................................................................... 1

SD VCR FF/RW Sync ................................................................ 45

Applications....................................................................................... 1

Vertical Blanking Interval ......................................................... 46

Functional Block Diagram .............................................................. 1

Subcarrier Frequency Registers................................................ 46

General Description ......................................................................... 1

Square Pixel Timing Mode........................................................ 47

Revision History ............................................................................... 3

Filters............................................................................................ 48

Detailed Features .............................................................................. 4

Color Controls and RGB Matrix .............................................. 49

Terminology ...................................................................................... 5

Programmable DAC Gain Control .......................................... 53

Specifications..................................................................................... 6

Gamma Correction .................................................................... 53

Dynamic Specifications ............................................................... 7

HD Sharpness Filter and Adaptive Filter Controls................ 55

Timing Specifications .................................................................. 8

HD Sharpness Filter and

Adaptive Filter Application Examples ..................................... 56

Timing Diagrams.......................................................................... 9

Absolute Maximum Ratings.......................................................... 16

Thermal Characteristics ............................................................ 16

ESD Caution................................................................................ 16

Pin Configuration and Function Descriptions........................... 17

Typical Performance Characteristics ........................................... 19

MPU Port Description................................................................... 23

Register Access................................................................................ 25

Register Programming............................................................... 25

Subaddress Register (SR7 to SR0) ............................................ 25

Input Configuration ....................................................................... 38

SD Only........................................................................................ 38

PS Only or HDTV Only ............................................................ 38

Simultaneous SD/PS or SD/HDTV.......................................... 38

PS at 27 MHz (Dual Edge) or 54 MHz .................................... 39

Features ............................................................................................ 41

Output Configuration................................................................ 41

HD Async Timing Mode........................................................... 42

HD Timing Reset........................................................................ 43

SD Real-Time Control, Subcarrier Reset, and Timing Reset ....43

SD Digital Noise Reduction...................................................... 57

Coring Gain Border ................................................................... 58

Coring Gain Data ....................................................................... 58

DNR Threshold .......................................................................... 58

Border Area................................................................................. 58

Block Size Control...................................................................... 58

DNR Input Select Control......................................................... 58

DNR Mode Control ................................................................... 59

Block Offset Control .................................................................. 59

SD Active Video Edge................................................................ 59

SAV/EAV Step-Edge Control ................................................... 59

HSYNC/VSYNC Output Control ............................................ 61

Board Design and Layout.............................................................. 62

DAC Termination and Layout Considerations ...................... 62

Video Output Buffer and Optional Output Filter.................. 62

PCB Board Layout...................................................................... 63

Appendix 1—Copy Generation Management System .............. 65

PS CGMS..................................................................................... 65

HD CGMS................................................................................... 65

SD CGMS .................................................................................... 65

Rev. A | Page 2 of 88

ADV7320/ADV7321

CGMS Functionality...................................................................65

Appendix 2—SD Wide Screen Signaling .....................................68

Mode 2—Master Option

(Timing Register 0 TR0 = X X X X X 1 0 1) ............................79

Appendix 3—SD Closed Captioning............................................69

Mode 3—Master/Slave Option

(Timing Register 0 TR0 = X X X X X 1 1 0 or X X X X X 1 1 1)...80

Appendix 4—Test Patterns.............................................................70

Appendix 6—HD Timing ..............................................................81

Appendix 5—SD Timing Modes...................................................73

Appendix 7—Video Output Levels...............................................82

Mode 0 (CCIR-656)—Slave Option

(Timing Register 0 TR0 = X X X X X 0 0 0) ............................73

HD YPrPb Output Levels ..........................................................82

Mode 0 (CCIR-656)—Master Option

(Timing Register 0 TR0 = X X X X X 0 0 1) ............................74

Mode 1—Slave Option

(Timing Register 0 TR0 = X X X X X 0 1 0) ............................76

Mode 1—Master Option

(Timing Register 0 TR0 = X X X X X 0 1 1) ............................77

RGB Output Levels .....................................................................83

YPrPb Levels—SMPTE/EBU N10............................................84

Appendix 8—Video Standards ......................................................86

Outline Dimensions........................................................................88

Ordering Guide ...........................................................................88

Mode 2— Slave Option

(Timing Register 0 TR0 = X X X X X 1 0 0) ............................78

REVISION HISTORY

5/06—Rev. 0 to Rev. A

Replaced Figure 11 ..........................................................................12

Changes to Table 25 ........................................................................41

10/04—Revision 0: Initial Version

Rev. A | Page 3 of 88

ADV7320/ADV7321

Table 1. Standards Directly Supported 1

DETAILED FEATURES

HD programmable features (720p/1080i/1035i)

2× oversampling (148.5 MHz)

Internal test pattern generator

Color hatch, black bar, flat field/frame

Fully programmable YCrCb to RGB matrix

Gamma correction

Programmable adaptive filter control

Programmable sharpness filter control

CGMS-A (720p/1080i)

ED programmable features (525p/625p)

8× oversampling (216 MHz output)

Internal test pattern generator

Color hatch, black bar, flat frame

Individual Y and PrPb output delay

Gamma correction

Programmable adaptive filter control

Fully programmable YCrCb to RGB matrix

Undershoot limiter

Macrovision Rev 1.2 (525p/625p) (ADV7320 only)

CGMS-A (525p/625p)

SD programmable features

16× oversampling (216 MHz)

Internal test pattern generator

Color bars, black bar

Controlled edge rates for start and end of active video

Individual Y and PrPb output delay

Undershoot limiter

Gamma correction

Digital noise reduction (DNR)

Multiple chroma and luma filters

Luma-SSAF™ filter with programmable gain/attenuation

PrPb SSAF™

Separate pedestal control on component and

composite/S-video output

VCR FF/RW sync mode

Macrovision Rev 7.1.L1 (ADV7320 only)

CGMS/WSS

Closed captioning

Resolution

720 × 480

Interlace/PS

I

Frame

Rate

(Hz)

29.97

720 × 576

I

25

27

720 × 480

I

29.97

24.54

720 × 576

I

25

29.5

720 × 483

P

59.94

27

720 × 483

720 × 483

P

P

59.94

59.94

27

27

720 × 576

P

50

27

720 × 483

P

59.94

27

720 × 576

P

50

27

1920 × 1035

I

1280 × 720

P

30

29.97

60, 50,

30, 25,

24

23.97,

59.94,

29.97

30, 25

29.97

30, 25,

24

23.98,

29.97

74.25

74.1758

74.25

1920 × 1080

I

1920 × 1080

P

1

Clock

Input

(MHz)

27

SMPTE

296M

74.1758

74.25

74.1758

74.25

74.1758

Other standards are supported in async timing mode.

Rev. A | Page 4 of 88

Standard

ITU-R

BT.656

ITU-R

BT.656

NTSC

Square

Pixel

PAL

Square

Pixel

SMPTE

293M

BTA T-1004

ITU-R

BT.1358

ITU-R

BT.1358

ITU-R

BT.1362

ITU-R

BT.1362

SMPTE

240M

SMPTE

274M

SMPTE

274M

ADV7320/ADV7321

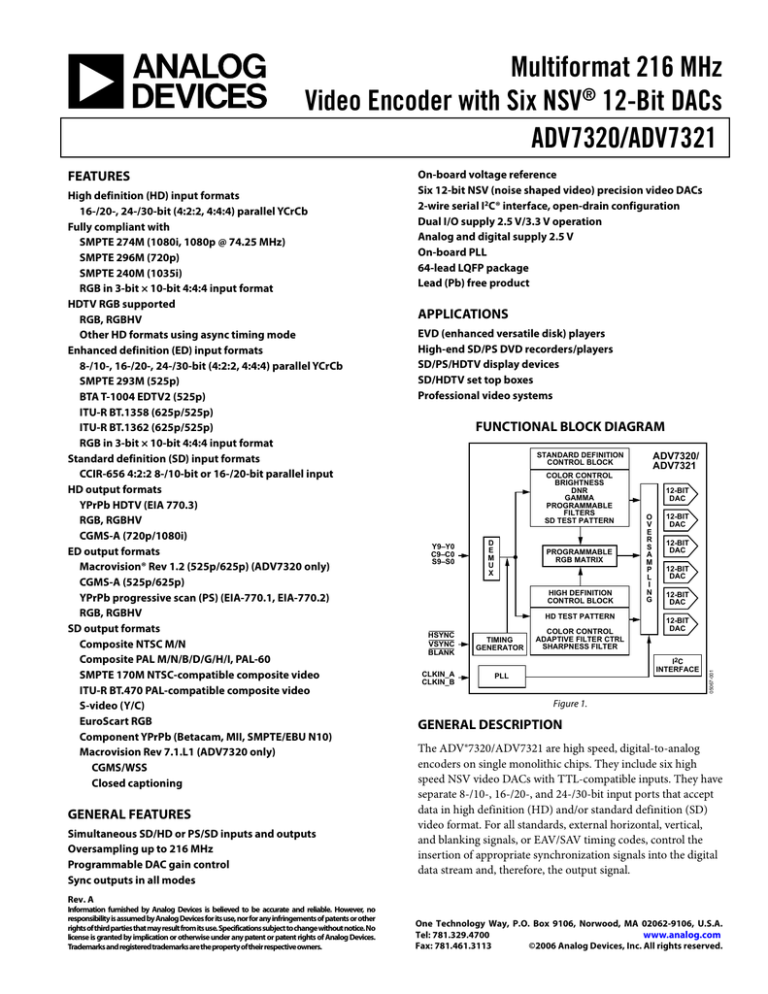

HD PIXEL

INPUT

CLKIN_B

Y

DEINTER- CR

LEAVE

CB

TEST

PATTERN

SHARPNESS

AND

ADAPTIVE

FILTER

CONTROL

Y COLOR

CR COLOR

CB COLOR

4:2:2

TO

4:4:4

PS 8×

HDTV 2×

DAC

DAC

TIMING

GENERATOR

S_HSYNC

S_VSYNC

S_BLANK

CLKIN_A

SD PIXEL

INPUT

CLOCK

CONTROL

AND PLL

DAC

U

V

TIMING

GENERATOR

UV SSAF

RGB

MATRIX

DAC

SD 16×

CB

DEINTER- CR

LEAVE

Y

TEST

PATTERN

DNR

GAMMA

COLOR

CONTROL

SYNC

INSERTION

LUMA

AND

CHROMA

FILTERS

2× OVERSAMPLING

FSC

MODULATION

CGMS

WSS

DAC

DAC

05067-002

P_HSYNC

P_VSYNC

P_BLANK

Figure 2. Detailed Functional Block Diagram

TERMINOLOGY

HDTV: high definition television video, conforming to SMPTE

274M, or SMPTE 296M and SMPTE 240M.

SD: standard definition video, conforming to

ITU-R BT.601/ITU-R BT.656.

YCrCb SD, PS, or HD component: digital video.

HD: high definition video, that is, 720p/1080i/1035i.

YPrPb SD, PS, or HD component: analog video.

EDTV: enhanced definition television (525p/625p).

PS: progressive scan video, conforming to SMPTE 293M,

ITU-R BT.1358, BTA T-1004 EDTV2, or ITU-R BT.13621362.

Rev. A | Page 5 of 88

ADV7320/ADV7321

SPECIFICATIONS

VAA = 2.375 V to 2.625 V, VDD = 2.375 V to 2.625 V, VDD_IO = 2.375 V to 3.6 V, VREF = 1.235 V, RSET = 3040 Ω, RLOAD = 300 Ω. All

specifications TMIN to TMAX (0°C to 70°C), unless otherwise noted.

Table 2.

Parameter

STATIC PERFORMANCE 1

Resolution

Integral Nonlinearity

Differential Nonlinearity, 2 +ve

Differential Nonlinearity,2 −ve

DIGITAL OUTPUTS

Output Low Voltage, VOL

Output High Voltage, VOH

Three-State Leakage Current

Three-State Output Capacitance

DIGITAL AND CONTROL INPUTS

Input High Voltage, VIH

Input Low Voltage, VIL

Input Leakage Current

Input Capacitance, CIN

ANALOG OUTPUTS

Full-Scale Output Current

Output Current Range

DAC-to-DAC Matching

Output Compliance Range, VOC

Output Capacitance, COUT

VOLTAGE REFERENCE

Internal Reference Range, VREF

External Reference Range, VREF

VREF Current 4

POWER REQUIREMENTS

Normal Power Mode

IDD 5

IDD_IO

IAA 7, 8

Sleep Mode

IDD

IAA

IDD_IO

POWER SUPPLY REJECTION RATIO

Min

Typ

Max

12

1.5

0.25

1.5

0.4 [0.4] 3

±1.0

2

2

0.8

10

2

0

1.15

1.15

4.33

4.33

1.0

1.0

7

4.6

4.6

1.235

1.235

±10

1.3

1.3

137

78

73

140

1.0

37

80

7

250

0.01

Test Conditions

Bits

LSB

LSB

LSB

2.4 [2.0]3

4.1

4.1

Unit

1.4

190 6

45

V

V

μA

pF

V

V

μA

pF

ISINK = 3.2 mA

ISOURCE = 400 μA

VIN = 0.4 V, 2.4 V

VIN = 2.4 V

mA

mA

%

V

pF

V

V

μA

mA

mA

mA

mA

mA

mA

SD only (16×)

PS only (8×)

HDTV only (2×)

SD (16×, 10 bit) + PS (8×, 20 bit)

μA

μA

μA

%/%

1

Oversampling disabled. Static DAC performance improves with increased oversampling ratios.

DNL measures the deviation of the actual DAC output voltage step from the ideal. For +ve DNL, the actual step value lies above the ideal step value; for −ve DNL, the

actual step value lies below the ideal step value.

3

For values in brackets, VDD_IO = 2.375 V to 2.75 V.

4

External current required to overdrive internal VREF.

5

IDD, the circuit current, is the continuous current required to drive the digital core.

6

Guaranteed maximum by characterization.

7

All DACs on.

8

IAA is the total current required to supply all DACs, including the VREF circuitry and the PLL circuitry.

2

Rev. A | Page 6 of 88

ADV7320/ADV7321

DYNAMIC SPECIFICATIONS

VAA = 2.375 V to 2.625 V, VDD = 2.375 V to 2.625 V, VDD_IO = 2.375 V to 3.6 V, VREF = 1.235 V, RSET = 3040 Ω, RLOAD = 300 Ω. All

specifications TMIN to TMAX (0°C to 70°C), unless otherwise noted.

Table 3.

Parameter

PS MODE

Luma Bandwidth

Chroma Bandwidth

SNR

HDTV MODE

Luma Bandwidth

Chroma Bandwidth

SD MODE

Hue Accuracy

Color Saturation Accuracy

Chroma Nonlinear Gain

Chroma Nonlinear Phase

Chroma/Luma Intermodulation

Chroma/Luma Gain Inequality

Chroma/Luma Delay Inequality

Luminance Nonlinearity

Chroma AM Noise

Chroma PM Noise

Differential Gain

Differential Phase

SNR

Min

Typ

Max

Unit

Test Conditions

12.5

5.8

65.6

72

MHz

MHz

dB

dB

Luma ramp unweighted

Flat field full bandwidth

30

13.75

MHz

MHz

0.2

0.20

0.84

−0.2

0

96.7

−1.0

0.2

84

75.3

0.25

0.2

63.5

77.7

Degrees

%

±%

±Degrees

±%

±%

ns

±%

dB

dB

%

Degrees

dB

dB

Rev. A | Page 7 of 88

Referenced to 40 IRE

NTSC

NTSC

Luma ramp

Flat field full bandwidth

ADV7320/ADV7321

TIMING SPECIFICATIONS

VAA = 2.375 V to 2.625 V, VDD = 2.375 V to 2.625 V, VDD_IO = 2.375 V to 3.6 V, VREF = 1.235 V, RSET = 3040 Ω, RLOAD = 300 Ω. All

specifications TMIN to TMAX (0°C to 70°C), unless otherwise noted.

Table 4.

Parameter

MPU PORT 1

SCLOCK Frequency

SCLOCK High Pulse Width, t1

SCLOCK Low Pulse Width, t2

Hold Time (Start Condition), t3

Setup Time (Start Condition), t4

Data Setup Time, t5

SDATA, SCLOCK Rise Time, t6

SDATA, SCLOCK Fall Time, t7

Setup Time (Stop Condition), t8

RESET Low Time

ANALOG OUTPUTS

Analog Output Delay 2

Output Skew

CLOCK CONTROL AND PIXEL PORT 3

fCLK

fCLK

Clock High Time, t9

Clock Low Time, t10

Data Setup Time, t111

Data Hold Time, t121

SD Output Access Time, t13

SD Output Hold Time, t14

HD Output Access Time, t13

HD Output Hold Time, t14

PIPELINE DELAY 4

Min

Typ

0

0.6

1.3

0.6

Max

Unit

400

kHz

μs

μs

μs

0.6

100

300

300

0.6

100

7

1

29.5

40

40

2.0

2.0

15

5.0

14

63

76

35

41

36

First clock generated after this period relevant for

repeated start condition

μs

ns

ns

ns

μs

ns

ns

ns

81

5.0

Test Conditions

MHz

MHz

% of one clock cycle

% of one clock cycle

ns

ns

ns

ns

ns

ns

Clock cycles

Clock cycles

Clock cycles

Clock cycles

Clock cycles

1

SD PAL square pixel mode

PS/HD async mode

SD (2×, 16×)

SD component mode (16×)

PS (1×)

PS (8×)

HD (2×, 1×)

Guaranteed by characterization.

Output delay measured from the 50% point of the rising edge of CLOCK to the 50% point of DAC output full-scale transition.

3

Data: C[9:0], Y[9:0], S[9:0]; Control: P_HSYNC, P_VSYNC, P_BLANK, S_HSYNC, S_VSYNC, S_BLANK.

4

SD, PS = 27 MHz; HD = 74.25 MHz.

2

Rev. A | Page 8 of 88

ADV7320/ADV7321

TIMING DIAGRAMS

CLKIN_A

t9

CONTROL

INPUTS

t12

t10

P_HSYNC,

P_VSYNC,

P_BLANK

Y9–Y0

Y0

Y1

Y2

Y3

Y4

Y5

C9–C0

Cb0

Cr0

Cb2

Cr2

Cb4

Cr4

t11

t13

CONTROL

OUTPUTS

t14

05067-003

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

Figure 3. HD Only 4:2:2 Input Mode (Input Mode 010); PS Only 4:2:2 Input Mode (Input Mode 001)

CLKIN_A

t9

CONTROL

INPUTS

t12

t10

P_HSYNC,

P_VSYNC,

P_BLANK

Y9–Y0

Y0

Y1

Y2

Y3

Y4

Y5

C9–C0

Cb0

Cb1

Cb2

Cb3

Cb4

Cb5

Cr2

Cr3

Cr4

Cr5

t11

S9–S0

Cr0

Cr1

CONTROL

OUTPUTS

t14

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

05067-004

t13

Figure 4. HD Only 4:4:4 Input Mode (Input Mode 010); PS Only 4:4:4 Input Mode (Input Mode 001)

Rev. A | Page 9 of 88

ADV7320/ADV7321

CLKIN_A

t9

CONTROL

INPUTS

t12

t10

P_HSYNC,

P_VSYNC,

P_BLANK

Y9–Y0

G0

G1

G2

G3

G4

G5

C9–C0

B0

B1

B2

B3

B4

B5

R2

R3

R4

R5

t11

S9–S0

R0

R1

CONTROL

OUTPUTS

t14

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

05067-005

t13

Figure 5. HD RGB 4:4:4 Input Mode (Input Mode 010)

CLKIN_B*

t9

CONTROL

INPUTS

t10

P_HSYNC,

P_VSYNC,

P_BLANK

Cb0

Y9–Y0

Y0

Cr0

t12

t11

Crxxx

Y1

Yxxx

t12

t11

t13

CONTROL

OUTPUTS

*CLKIN_B MUST BE USED IN THIS PS MODE.

Figure 6. PS 4:2:2 10-Bit Interleaved at 27 MHz HSYNC/VSYNC Input Mode (Input Mode 100)

Rev. A | Page 10 of 88

05067-006

t14

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

ADV7320/ADV7321

CLKIN_A

t10

t9

CONTROL

INPUTS

P_VSYNC,

P_HSYNC,

P_BLANK

Cb0

Y9–Y0

Yxxx

t13

t12

t11

Crxxx

Y1

Cr0

Y0

t14

CONTROL

OUTPUTS

05067-007

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

Figure 7. PS 4:2:2 10-Bit Interleaved at 54 MHz HSYNC /VSYNC Input Mode (Input Mode 111)

CLKIN_B*

t9

3FF

Y9–Y0

t10

00

00

XY

t12

Cb0

Y0

Cr0

Y1

t12

t11

t11

t13

CONTROL

OUTPUTS

t14

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

05067-008

*CLKIN_B USED IN THIS PS ONLY MODE.

Figure 8. PS Only 4:2:2 10-Bit Interleaved at 27 MHz EAV/SAV Input Mode (Input Mode 100)

CLKIN_A

t9

Y9–Y0

3FF

t11

t12

t10

00

00

XY

Cb0

Y0

Cr0

Y1

t13

t14

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

NOTES

1. Y0, Cb0 SEQUENCE AS PER SUBADDRESS 0x01 BIT 1.

Figure 9. PS Only 4:2:2 10-Bit Interleaved at 54 MHz EAV/SAV Input Mode (Input Mode 111)

Rev. A | Page 11 of 88

05067-009

CONTROL

OUTPUTS

ADV7320/ADV7321

CLKIN_B

t9

CONTROL

INPUTS

t12

t10

P_HSYNC,

P_VSYNC,

P_BLANK

Y9–Y0

Y0

Y1

Y2

Y3

Y4

Y5

C9–C0

Cb0

Cr0

Cb2

Cr2

Cb4

Cr4

HD INPUT

t11

CLKIN_A

CONTROL

INPUTS

S_HSYNC,

S_VSYNC,

S_BLANK

S9–S0

t9

t12

t10

SD INPUT

Cr0

Y0

Cb0

Y1

Cb1

Y2

t11

05067-010

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

Figure 10. HD 4:2:2 and SD 10-Bit Simultaneous Input Mode (Input Mode 101: SD Oversampled) (Input Mode 110: HD Oversampled)

CLKIN_B

t9

CONTROL

INPUTS

t12

t10

P_HSYNC,

P_VSYNC,

P_BLANK

Y9–Y0

Y0

Y1

Y2

Y3

Y4

Y5

C9–C0

Cb0

Cr0

Cb2

Cr2

Cb4

Cr4

PS INPUT

t11

CLKIN_A

S_HSYNC,

S_VSYNC,

S_BLANK

S9–S0

t9

t12

t10

SD INPUT

Cb0

Y0

Cr0

Y1

Cb1

Y2

t11

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

05067-011

CONTROL

INPUTS

Figure 11. PS 4:2:2 and SD 10-Bit Simultaneous Input Mode (Input Mode 011)

Rev. A | Page 12 of 88

ADV7320/ADV7321

CLKIN_B

t9

CONTROL

INPUTS

t10

P_HSYNC,

P_VSYNC,

P_BLANK

PS INPUT

Y9–Y0

Cb0

Cr0

Y0

Crxxx

Y1

t12

Yxxx

t12

t11

t11

CLKIN_A

CONTROL

INPUTS

t9

S_HSYNC,

S_VSYNC,

S_BLANK

t12

t10

SD INPUT

S9–S0

Cr0

Y0

Cb0

Y1

Cb1

Y2

t11

05067-012

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

Figure 12. PS 10-Bit and SD 10-Bit Simultaneous Input Mode (Input Mode 100)

CLKIN_A

t9

CONTROL

INPUTS

t12

t10

S_HSYNC,

S_VSYNC,

S_BLANK

S9–S0/Y9–Y0*

IN SLAVE MODE

Cb0

Y0

t11

Cr0

Y1

Cb1

Y2

t13

CONTROL

OUTPUTS

IN MASTER/SLAVE MODE

t14

*SELECTED BY ADDRESS 0x01, BIT 7: SEE TABLE 21.

05067-013

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

Figure 13. 8-/10-Bit SD Only Pixel Input Mode (Input Mode 000)

Rev. A | Page 13 of 88

ADV7320/ADV7321

CLKIN_A

t9

CONTROL

INPUTS

t12

t10

S_HSYNC,

S_VSYNC,

S_BLANK

S9–S0/Y9–Y0*

C9–C0

IN SLAVE MODE

Y0

Cb0

t11

Y1

Y2

Y3

Cr0

Cb2

Cr2

t13

CONTROL

OUTPUTS

IN MASTER/SLAVE MODE

t14

*SELECTED BY ADDRESS 0x01, BIT 7: SEE TABLE 21.

05067-014

t9 = CLOCK HIGH TIME

t10 = CLOCK LOW TIME

t11 = DATA SETUP TIME

t12 = DATA HOLD TIME

t13 = HD OUTPUT ACCESS TIME

t14 = HD OUTPUT HOLD TIME

Figure 14. 16-/20-Bit SD Only Pixel Input Mode (Input Mode 000)

Y OUTPUT

c

P_HSYNC

P_VSYNC

a

P_BLANK

Y0

Y1

Y2

Y3

C9–C0

Cb0

Cr0

Cr1

Cb1

b

05067-015

Y9–Y0

a AND b AS PER RELEVANT STANDARD.

c = PIPELINE DELAY. PLEASE REFER TO RELEVANT PIPELINE DELAY. THIS CAN BE FOUND IN THE TIMING SPECIFICATION

SECTION OF THE DATA SHEET.

A FALLING EDGE OF HSYNC INTO THE ENCODER GENERATES A FALLING EDGE OF TRI-LEVEL SYNC ON THE OUTPUT

AFTER A TIME EQUAL TO THE PIPELINE DELAY.

Figure 15. HD 4:2:2 Input Timing Diagram

Rev. A | Page 14 of 88

ADV7320/ADV7321

P_HSYNC

P_VSYNC

a

P_BLANK

Y9–Y0

Cb

Cr

Y

Y

b

05067-016

a = 32 CLKCYCLES FOR 525p

a = 24 CLKCYCLES FOR 625p

AS RECOMMENDED BY STANDARD

b(MIN) = 244 CLKCYCLES FOR 525p

b(MIN) = 264 CLKCYCLES FOR 625p

Figure 16. PS 4:2:2 10-Bit Interleaved Input Timing Diagram

S_HSYNC

S_VSYNC

PAL = 24 CLK CYCLES

NTSC = 32 CLK CYCLES

S_BLANK

S9–S0/Y9–Y0*

Cb

Y

Cr

05067-017

PAL = 264 CLOCK CYCLES

NTSC = 244 CLOCK CYCLES

*SELECTED BY ADDRESS 0x01, BIT 7: SEE TABLE 21.

Figure 17. SD Timing Input for Timing Mode 1

t3

t5

t3

SDA

t1

t6

SCLK

t2

t4

t7

t8

05067-018

t1 = SCLOCK HIGH PULSE WIDTH

t2 = SCLOCK LOW PULSE WIDTH

t3 = HOLD TIME (START CONDITION)

t4 = SETUP TIME (START CONDITION)

t5 = DATA SETUP TIME

t6 = SDATA, SCLOCK RISE TIME

t7 = SDATA, SCLOCK FALL TIME

t8 = SETUP TIME (STOP CONDITION)

Figure 18. MPU Port Timing Diagram

Rev. A | Page 15 of 88

Y

ADV7320/ADV7321

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter 1

VAA to AGND

VDD to DGND

VDD_IO to GND_IO

Digital Input Voltage to DGND

VAA to VDD

AGND to DGND

DGND to GND_IO

AGND to GND_IO

Ambient Operating Temperature (TA)

Storage Temperature (TS)

Infrared Reflow Soldering (20 sec)

1

Value

−0.3 V to +3.0 V

−0.3 V to +3.0 V

−0.3 V to +4.6 V

−0.3 V to VDD_IO +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

0°C to 70°C

–65°C to +150°C

260°C

Analog output short circuit to any power supply or common can be of

an indefinite duration.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

θJC = 11°C/W

θJA = 47°C/W

The ADV7320/ADV7321 are Pb-free, environmentally friendly

products. They are manufactured using the most up-to-date

materials and processes. The coating on the leads of each device

is 100% pure Sn electroplate. The devices are suitable for Pbfree applications and are able to withstand surface-mount

soldering up to 255°C (±5°C).

In addition, they are backward-compatible with conventional

SnPb soldering processes. This means that the electroplated Sn

coating can be soldered with Sn/Pb solder pastes at conventional

reflow temperatures of 220°C to 235°C.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. A | Page 16 of 88

ADV7320/ADV7321

64 63 62 61 60 59 58

S_VSYNC

S_HSYNC

S0

S1

S2

S3

S4

VDD

DGND

S5

S6

S7

S8

S9

CLKIN_B

GND_IO

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

57 56 55 54 53 52 51 50 49

VDD_IO

1

Y0

2

48 S_BLANK

Y1

3

46 VREF

Y2

4

45 COMP1

Y3

5

44 DAC A

Y4

6

Y5

7

Y6

8

Y7

9

PIN 1

47 RSET1

43 DAC B

ADV7320/ADV7321

42 DAC C

TOP VIEW

(Not to Scale)

41 VAA

40 AGND

VDD 10

39 DAC D

DGND 11

38 DAC E

Y8 12

37 DAC F

Y9 13

36 COMP2

C0 14

35 RSET2

C1 15

34 EXT_LF

C2 16

33 RESET

05067-019

CLKIN_A

RTC_SCR_TR

C9

C8

C7

C6

C5

P_BLANK

P_VSYNC

P_HSYNC

SCLK

SDA

ALSB

I2C

C4

C3

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Figure 19. Pin Configuration

Table 6. Pin Function Descriptions

Pin No.

11, 57

40

32

63

Mnemonic

DGND

AGND

CLKIN_A

CLKIN_B

Input/Output

G

G

I

I

45, 36

O

44

43

42

39

COMP1,

COMP2

DAC A

DAC B

DAC C

DAC D

O

O

O

O

38

DAC E

O

37

DAC F

O

23

24

25

48

49

50

13, 12,

9 to 2

30 to 26,

18 to 14

P_HSYNC

P_VSYNC

P_BLANK

S_BLANK

S_VSYNC

S_HSYNC

Y9 to Y0

I

I

I

I/O

I/O

I/O

I

C9 to C0

I

Description

Digital Ground.

Analog Ground.

Pixel Clock Input for HD Only (74.25 MHz), PS Only (27 MHz), and SD Only (27 MHz).

Pixel Clock Input. Requires a 27 MHz reference clock for PS mode or a 74.25 MHz (74.1758 MHz)

reference clock in HDTV mode. This clock is only used in dual modes.

Compensation Pin for DACs. Connect 0.1 μF capacitor from COMP pin to VAA.

CVBS/Green/Y/Y Analog Output.

Chroma/Blue/U/Pb Analog Output.

Luma/Red/V/Pr Analog Output.

In SD Only Mode: CVBS/Green/Y Analog Output; in HD Only Mode and Simultaneous HD/SD

Mode: Y/Green [HD] Analog Output.

In SD Only Mode: Luma/Blue/U Analog Output; in HD Only Mode and Simultaneous HD/SD

Mode: Pr/Red Analog Output.

In SD Only Mode: Chroma/Red/V Analog Output; in HD Only Mode and Simultaneous HD/SD

Mode: Pb/Blue [HD] Analog Output.

Video Horizontal Sync Control Signal for HD in Simultaneous SD/HD Mode and HD Only Mode.

Video Vertical Sync Control Signal for HD in Simultaneous SD/HD Mode and HD Only Mode.

Video Blanking Control Signal for HD in Simultaneous SD/HD Mode and HD Only Mode.

Video Blanking Control Signal for SD Only.

Video Vertical Sync Control Signal for SD Only.

Video Horizontal Sync Control Signal for SD Only.

SD or PS/HDTV Input Port for Y Data. Input port for interleaved progressive scan data. The LSB

is set up on Pin Y0. For 8-bit data input, LSB is set up on Pin Y2.

PS/HDTV Input Port 4:4:4 Input Mode. This port is used for the Cb[Blue/U] data. The LSB is set

up on Pin C0. For 8-bit data input, LSB is set up on Pin C2.

Rev. A | Page 17 of 88

ADV7320/ADV7321

Pin No.

62 to 58,

55 to 51

33

Mnemonic

S9 to S0

Input/Output

I

RESET

I

47, 35

RSET1, RSET2

I

22

21

20

SCLK

SDA

ALSB

I

I/O

I

1

10, 56

41

46

34

31

19

64

VDD_IO

VDD

VAA

VREF

EXT_LF

RTC_SCR_TR

I2C

GND_IO

P

P

P

I/O

I

I

I

Description

SD or PS/HDTV Input Port for Cr[Red/V] Data in 4:4:4 Input Mode. LSB is set up on Pin S0. For

8-bit data input, LSB is set up on Pin S2.

This input resets the on-chip timing generator and sets the ADV7320/ADV7321 into default

register setting. RESET is an active low signal.

A 3040 Ω resistor must be connected from this pin to AGND and is used to control the

amplitudes of the DAC outputs.

I2C Port Serial Interface Clock Input.

I2C Port Serial Data Input/Output.

TTL Address Input. This signal sets up the LSB of the I2C address. When this pin is tied low, the

I2C filter is activated, which reduces noise on the I2C interface.

Power Supply for Digital Inputs and Outputs.

Digital Power Supply.

Analog Power Supply.

Optional External Voltage Reference Input for DACs or Voltage Reference Output (1.235 V).

External Loop Filter for the Internal PLL.

Multifunctional Input. Real-time control (RTC) input, timing reset input, subcarrier reset input.

This input pin must be tied high (VDD_IO) for the ADV7320/ADV7321 to interface over the I2C port.

Digital Input/Output Ground.

Rev. A | Page 18 of 88

ADV7320/ADV7321

TYPICAL PERFORMANCE CHARACTERISTICS

PS Pr/Pb RESPONSE. LINEAR INTERPOLATION (4:2:2 TO 4:4:4)

Y PASS BAND IN PS OVERSAMPLING MODE

1.0

0

0.5

–10

0

–0.5

–30

GAIN (dB)

–40

–1.5

–50

–2.0

05067-045

–60

–70

–80

–1.0

0

20

40

60

80 100 120 140

FREQUENCY (MHz)

160

180

05067-048

GAIN (dB)

–20

–2.5

–3.0

200

0

Figure 20. PS—UV 8× Oversampling Filter (Linear)

–10

–20

–20

–30

–30

–40

–50

–60

–60

–70

60

80 100 120 140

FREQUENCY (MHz)

160

180

–70

–80

200

0

Figure 21. PS—UV 8× Oversampling Filter (SSAF)

–10

–20

–20

–30

–30

–40

–50

–60

–60

–70

60

80 100 120 140

FREQUENCY (MHz)

160

180

120

140

–40

–50

40

60

80

100

FREQUENCY (MHz)

05067-050

GAIN (dB)

–10

20

40

Y RESPONSE IN HDTV OVERSAMPLING MODE

0

05067-047

GAIN (dB)

Y RESPONSE IN PS OVERSAMPLING MODE

0

20

Figure 24. HDTV—UV 2× Oversampling Filter

0

–80

12

–40

–50

40

10

05067-049

GAIN (dB)

–10

05067-046

GAIN (dB)

0

20

6

8

FREQUENCY (MHz)

Pr/Pb RESPONSE IN HDTV OVERSAMPLING MODE

PS Pr/Pb RESPONSE. SSAF INTERPOLATION (4:2:2 TO 4:4:4)

0

4

Figure 23. PS—Y 8× Oversampling Filter (Pass Band)

0

–80

2

–70

–80

200

Figure 22. PS—Y 8× Oversampling Filter

0

20

40

60

80

100

FREQUENCY (MHz)

120

Figure 25. HDTV—Y 2× Oversampling Filter

Rev. A | Page 19 of 88

140

0

–10

–10

–20

–20

–30

–40

–30

–40

–50

–50

–60

–60

–70

05067-054

MAGNITUDE (dB)

0

05067-051

MAGNITUDE (dB)

ADV7320/ADV7321

–70

0

2

4

6

8

FREQUENCY (MHz)

10

12

0

2

Figure 26. Luma NTSC Low-Pass Filter

4

6

8

FREQUENCY (MHz)

10

12

Figure 29. Luma PAL Notch Filter

0

–10

–10

–20

–20

GAIN (dB)

MAGNITUDE (dB)

Y RESPONSE IN SD OVERSAMPLING MODE

0

–30

–40

–30

–40

–50

–50

05067-052

–70

–70

–80

0

2

4

6

8

FREQUENCY (MHz)

10

05067-055

–60

–60

12

0

0

–10

–10

–20

–20

–30

–40

160

180

200

–40

–50

–60

–60

–70

4

6

8

FREQUENCY (MHz)

80 100 120 140

FREQUENCY (MHz)

–30

–50

2

60

10

05067-056

MAGNITUDE (dB)

0

0

40

Figure 30. Y—16× Oversampling Filter

05067-053

MAGNITUDE (dB)

Figure 27. Luma PAL Low-Pass Filter

20

–70

0

12

2

4

6

8

FREQUENCY (MHz)

10

Figure 31. Luma SSAF Filter up to 12 MHz

Figure 28. Luma NTSC Notch Filter

Rev. A | Page 20 of 88

12

ADV7320/ADV7321

4

0

2

–10

MAGNITUDE (dB)

–2

–4

–6

–20

–30

–40

–50

–8

–60

05067-057

–10

–70

–12

0

1

2

3

4

FREQUENCY (MHz)

5

6

05067-060

MAGNITUDE (dB)

0

7

0

Figure 32. Luma SSAF Filter—Programmable Responses

2

4

8

6

FREQUENCY (MHz)

10

12

10

12

10

12

Figure 35. Luma CIF Low-Pass Filter

5

4

–10

3

–20

MAGNITUDE (dB)

MAGNITUDE (dB)

0

2

1

–30

–40

–50

–1

0

1

2

3

4

FREQUENCY (MHz)

5

6

05067-061

–60

05067-058

0

–70

0

7

Figure 33. Luma SSAF Filter—Programmable Gain

2

4

6

8

FREQUENCY (MHz)

Figure 36. Luma QCIF Low-Pass Filter

1

0

–10

MAGNITUDE (dB)

–1

–2

–3

–20

–30

–40

–50

–60

–5

05067-062

–4

05067-059

MAGNITUDE (dB)

0

–70

0

1

2

3

4

FREQUENCY (MHz)

5

6

0

7

Figure 34. Luma SSAF Filter—Programmable Attenuation

2

4

6

8

FREQUENCY (MHz)

Figure 37. Chroma 3.0 MHz Low-Pass Filter

Rev. A | Page 21 of 88

0

–10

–10

–20

–20

–30

–40

–30

–40

–50

–50

–60

–60

–70

0

2

4

6

8

FREQUENCY (MHz)

10

05067-066

MAGNITUDE (dB)

0

05067-063

MAGNITUDE (dB)

ADV7320/ADV7321

–70

12

0

0

–10

–10

–20

–20

–30

–40

–60

–60

4

6

8

FREQUENCY (MHz)

10

–70

0

12

2

4

6

8

FREQUENCY (MHz)

10

12

10

12

Figure 42. Chroma CIF Low-Pass Filter

0

–10

–10

–20

–20

–30

–40

–30

–40

–50

–50

–60

–60

–70

05067-068

MAGNITUDE (dB)

0

05067-065

MAGNITUDE (dB)

Figure 39. Chroma 1.3 MHz Low-Pass Filter

–70

0

2

4

6

8

FREQUENCY (MHz)

10

12

–40

–50

2

10

–30

–50

0

6

8

FREQUENCY (MHz)

05067-067

MAGNITUDE (dB)

0

–70

4

Figure 41. Chroma 0.65 MHz Low-Pass Filter

05067-064

MAGNITUDE (dB)

Figure 38. Chroma 2.0 MHz Low-Pass Filter

2

0

12

Figure 40. Chroma 1.0 MHz Low-Pass Filter

2

4

6

8

FREQUENCY (MHz)

Figure 43. Chroma QCIF Low-Pass Filter

Rev. A | Page 22 of 88

ADV7320/ADV7321

MPU PORT DESCRIPTION

The ADV7320/ADV7321 support a 2-wire serial (I2Ccompatible) microprocessor bus driving multiple peripherals.

This port operates in an open-drain configuration. Two inputs,

serial data (SDA) and serial clock (SCL), carry information

between any device connected to the bus and the ADV7320/

ADV7321. Each slave device is recognized by a unique address.

The ADV7320/ADV7321 have four possible slave addresses for

both read and write operations. These are unique addresses for

each device and are illustrated in Figure 44 and Figure 45. The

LSB sets either a read or write operation. Logic 1 corresponds to

a read operation, while Logic 0 corresponds to a write operation.

A1 is enabled by setting the ALSB pin of the ADV7320/ADV7321

to Logic 0 or Logic 1. When ALSB is set to 1, there is greater

input bandwidth on the I2C lines, which allows high speed data

transfers on this bus. When ALSB is set to 0, there is reduced

input bandwidth on the I2C lines, which means that pulses of

less than 50 ns do not pass into the I2C internal controller. This

mode is recommended for noisy systems.

1

1

0

1

0

1

A1

ADDRESS

CONTROL

SET UP BY

ALSB

05067-020

READ/WRITE

CONTROL

WRITE

READ

Figure 44. ADV7320 Slave Address = 0xD4

0

1

0

1

0

1

A1

Logic 0 on the LSB of the first byte means that the master writes

information to the peripheral. Logic 1 on the LSB of the first byte

means that the master reads information from the peripheral.

The ADV7320/ADV7321 act as standard slave devices on the

bus. The data on the SDA pin is eight bits long, supporting the

7-bit address plus the R/W bit. It interprets the first byte as the

device address and the second byte as the starting subaddress.

There is a subaddress auto-increment facility. This allows data

to be written to or read from registers in ascending subaddress

sequence starting at any valid subaddress. A data transfer is

always terminated by a stop condition. The user can also access

any unique subaddress register on a one-by-one basis without

updating all of the registers.

Stop and start conditions can be detected at any stage during

the data transfer. If these conditions are asserted out of

sequence with normal read and write operations, they cause the

device to immediately jump to the idle condition. During a

given SCL high period, the user should only issue a start

condition, a stop condition, or a stop condition followed by a

start condition. If an invalid subaddress is issued by the user,

the ADV7320/ADV7321 do not issue an acknowledge and

return to the idle condition. If the user utilizes the autoincrement method of addressing the encoder and exceeds the

highest subaddress, the following actions are taken:

X

0

1

SDA and SCL lines waiting for the start condition and the

correct transmitted address. The R/W bit determines the

direction of the data.

X

• In read mode, the highest subaddress register contents are

output until the master device issues a no acknowledge. This

indicates the end of a read. A no acknowledge condition is

when the SDA line is not pulled low on the ninth pulse.

ADDRESS

CONTROL

SET UP BY

ALSB

READ/WRITE

CONTROL

WRITE

READ

• In write mode, the data for the invalid byte is not loaded into

any subaddress register, a no acknowledge is issued by the

ADV7320/ADV7321, and the part returns to the idle

condition.

05067-021

0

1

Figure 45. ADV7321 Slave Address = 0x54

To control the various devices on the bus, the following

protocol must be followed. First, the master initiates a data

transfer by establishing a start condition, defined by a high-tolow transition on SDA while SCL remains high. This indicates

that an address/data stream will follow. All peripherals respond

to the start condition and shift the next eight bits (7-bit address

+ R/W bit). The bits are transferred from MSB down to LSB.

The peripheral that recognizes the transmitted address

responds by pulling the data line low during the ninth clock

pulse. This is known as an acknowledge bit. All other devices

withdraw from the bus at this point and maintain an idle

condition. The idle condition is where the device monitors the

Before writing to the subcarrier frequency registers, it is required

to reset ADV7320/ADV7321 at least once after power-up.

The four subcarrier frequency registers must be updated,

starting with Subcarrier Frequency Register 0 and ending with

Subcarrier Frequency Register 3. The subcarrier frequency will

only update after the last subcarrier frequency register byte has

been received by the ADV7320/ADV7321.

Figure 46 illustrates an example of data transfer for a write

sequence and the start and stop conditions. Figure 47 shows bus

write and read sequences.

Rev. A | Page 23 of 88

ADV7320/ADV7321

SCLOCK

S

9

1–7

8

START ADRR R/W ACK

9

1–7

8

SUBADDRESS ACK

1–7

DATA

8

9

ACK

P

STOP

05067-022

SDATA

Figure 46. Bus Data Transfer

S

SLAVE ADDR

A(S)

SUBADDR

A(S)

DATA

S

SLAVE ADDR A(S)

S = START BIT

P = STOP BIT

A(S) P

LSB = 1

LSB = 0

READ

SEQUENCE

DATA

A(S)

SUBADDR

A(S) S SLAVE ADDR

A(S) = ACKNOWLEDGE BY SLAVE

A(M) = ACKNOWLEDGE BY MASTER

A(S)

DATA

A(M)

A (S) = NO ACKNOWLEDGE BY SLAVE

A (M) = NO ACKNOWLEDGE BY MASTER

Figure 47. Read and Write Sequences

Rev. A | Page 24 of 88

DATA

A(M) P

05067-023

WRITE

SEQUENCE

ADV7320/ADV7321

REGISTER ACCESS

REGISTER PROGRAMMING

The MPU can write to or read from all registers of the

ADV7320/ADV7321 except the subaddress registers, which are

write only registers. The subaddress register selected determines

which register the next read or write operation will access. All

communication with the part through the bus starts with an

access to the subaddress register. A read/write operation is then

performed from/to the target address, which increments to the

next address until a stop command is performed on the bus.

The following tables describe the functionality of each register.

All registers can be read from and written to, unless otherwise

stated.

SUBADDRESS REGISTER (SR7 TO SR0)

Each subaddress register is an 8-bit write only register. After the

encoder’s bus is accessed and a read or write operation is selected,

the subaddress is set up. The subaddress register determines to

or from which register the operation takes place.

Table 7. Registers 0x00 to 0x01

SR7–

SR0

0x00

Register

Power

Mode

Register

Bit Description

Sleep Mode. With this

control enabled, the

current consumption is

reduced to μA level. All

DACs and the internal

PLL cct are disabled.

I2C registers can be

read from and written

to in sleep mode.

PLL and Oversampling

Control. This control

allows the internal PLL

cct to be powered

down and the

oversampling to be

switched off.

DAC F: Power On/Off.

Bit 7

Bit 6

Bit 5

Bit 4

0

1

0

1

0

1

Reserved.

Clock Edge.

0

0

1

Reserved.

Clock Align.

Register Setting

Sleep mode off.

Sleep mode on.

Reset Value

(Shaded)

0xFC

PLL on.

PLL off.

0

1

DAC B: Power On/Off.

DAC F off.

DAC F on.

DAC E off.

DAC E on.

DAC D off.

DAC D on.

DAC C off.

DAC C on.

DAC B off.

DAC B on.

DAC A off.

DAC A on.

Reserved.

Cb clocked upon

rising edge.

Y clocked upon rising

edge.

Only for PS

interleaved

input at 27

MHz.

0

0

1

Input Mode.

Y/C/S Bus Swap.

Bit 0

0

1

0

1

DAC C: Power On/Off.

Mode

Select

Register

Bit 1

0

1

DAC D: Power On/Off.

0x01

Bit 2

0

1

DAC E: Power On/Off.

DAC A: Power On/Off.

Bit 3

0

0

0

0

1

1

0

0

1

1

0

0

0

1

0

1

0

1

1

1

0

1

1

1

0

1

Rev. A | Page 25 of 88

Must be set if the

phase delay between

the two input clocks is

<9.25 ns or >27.75 ns.

SD input only.

PS input only.

HDTV input only.

SD and PS (20-bit).

SD and PS (10-bit).

SD and HDTV (SD

oversampled).

SD and HDTV (HDTV

oversampled).

PS only (at 54 MHz).

Allows data to be

applied to data ports

in various

configurations (SD

feature only).

Only if two

input clocks

are used.

0x38

See Table 21.

ADV7320/ADV7321

Table 8. Registers 0x02 to 0x0F

SR7–

SR0

0x02

Register

Mode Register 0

Bit Description

Reserved

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

0

Bit 0

0

0

1

Test Pattern Black

Bar

Manual RGB Matrix

Adjust

0

1

Sync on RGB 1

0

1

RGB/YPrPb Output

0

1

SD Sync

HD Sync

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0A

0x0B

0x0C

0x0D

0x0E

0x0F

1

2

0

1

0

1

RGB Matrix 0

RGB Matrix 1

RGB Matrix 2

RGB Matrix 3

RGB Matrix 4

RGB Matrix 5

RGB Matrix 6

DAC A, B, C

Output Level 2

DAC D, E, F

Output Level

x

x

x

x

x

x

x

x

x

x

x

x

x

0

1

0

…

1

0

0

1

0

…

1

0

1

0

…

1

0

0

1

0

…

1

Positive Gain to

DAC Output

Voltage

x

x

x

x

x

x

0

0

0

x

x

x

x

x

x

0

0

0

x

x

x

x

x

0

0

0

x

x

x

x

x

0

0

0

x

x

x

x

x

0

0

0

x

x

x

x

x

0

0

0

x

x

x

x

x

0

0

1

Negative Gain to

DAC Output

Voltage

0

0

1

1

1

0

1

1

1

0

1

0

0

0

0

1

0

0

0

0

1

0

0

0

0

1

0

0

0

0

1

0

0

0

1

Positive Gain to

DAC Output

Voltage

1

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

0

0

1

Negative Gain to

DAC Output

Voltage

0

0

1

1

1

0

1

1

1

0

1

0

0

0

0

1

0

0

0

0

1

0

0

0

0

1

0

0

0

0

1

0

0

0

1

1

1

1

1

1

1

1

Reserved

Reserved

Reserved

Reserved

Register Setting

0 must be written to these

bits.

Disabled.

Enabled.

Disable manual RGB

matrix adjust.

Enable manual RGB

matrix adjust.

No sync.

Sync on all RGB outputs.

RGB component outputs.

YPrPb component

outputs.

No sync output.

Output SD syncs on

S_HSYNC, S_VSYNC,

S_BLANK pins.

No sync output.

Output HD, ED, syncs on

S_HSYNC, S_VSYNC.

LSB for GY.

LSB for RV.

LSB for BU.

LSB for GV.

LSB for GU.

Bits 9 to 2 for GY.

Bits 9 to 2 for GU.

Bits 9 to 2 for GV.

Bits 9 to 2 for BU.

Bits 9 to 2 for RV.

0%

+0.018%

+0.036%

…

+7.382%

+7.5%

−7.5%

−7.382%

−7.364%

…

−0.018%

0%

+0.018%

+0.036%

…

+7.382%

+7.5%

−7.5%

−7.382%

−7.364%

…

−0.018%

Reset Values

0x20

0x11, Bit 2 must

also be enabled.

0x03

0xF0

0x4E

0x0E

0x24

0x92

0x7C

0x00

0x00

0x00

0x00

0x00

0x00

For more detail, refer to Appendix 7.

For more detail on the programmable output levels, refer to the Programmable DAC Gain Control section.

Rev. A | Page 26 of 88

ADV7320/ADV7321

Table 9. Registers 0x10 to 0x11

SR7–

SR0

0x10

Register

HD Mode

Register 1

Bit Description

HD Output Standard

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Input Sync Format

HD/ED Input Mode

Bit 2

Bit 1

0

0

1

Bit 0

0

1

0

1

1

0

HSYNC, VSYNC,

BLANK

1

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

1

0

0

1

0

1

EAV/SAV codes

SMPTE 293M,

ITU-BT. 1358

Async mode

BTA-1004,

ITU-BT. 1362

ITU-BT. 1358

ITU-BT. 1362

SMPTE 296M-1, -2

0

0

0

0

1

1

1

1

0

1

SMPTE 296M-3

SMPTE 296M-4, -5

0

0

1

1

0

0

0

0

0

1

SMPTE 296M-6

SMPTE 296M-7, -8

0

1

0

1

0

SMPTE 240M

0

0

0

1

1

1

0

1

1

1

0

0

1

0

1

Reserved

Reserved

SMPTE 274M-4, -5

0

0

1

1

1

1

1

1

0

1

SMPTE 274M-6

SMPTE 274M-7, -8

1

1

0

0

0

0

0

0

0

1

SMPTE 274M-9

SMPTE 274M-10, -11

10010–11111

0x11

HD Mode

Register 2

HD Pixel Data Valid

0

1

0

0

1

HD Test Pattern

Enable

0

1

HD Test Pattern

Hatch/Field

HD VBI Open

0

1

0

0

1

1

HD Undershoot

Limiter

HD Sharpness Filter

Register Setting

EIA770.2 output

EIA770.1 output

Output levels for

full input range

Reserved

0

1

0

1

0

1

Rev. A | Page 27 of 88

Reserved

Pixel data valid off

Pixel data valid on

Reserved

HD test pattern off

HD test pattern on

Hatch

Field/frame

Disabled

Enabled

Disabled

−11 IRE

−6 IRE

−1.5 IRE

Disabled

Enabled

Note

Reset

Values

0x00

525p @

59.94 Hz

525p @

59.94 Hz

625p @ 50 Hz

625p @ 50 Hz

720p @

60/59.94 Hz

720p @ 50 Hz

720p @

30/29.97 Hz

720p @ 25 Hz

720p @

24/23.98 Hz

1035i @

60/59.94 Hz

1080i @

30/29.97 Hz

1080i @ 25 Hz

1080p @

30/29.97 Hz

1080p @ 25 Hz

1080p @

24/23.98 Hz

0x00

Only available

in EDTV (525p/

625p)

ADV7320/ADV7321

Table 10. Register 0x12

SR7–

SR0

0x12

Register

HD Mode

Register 3

Bit Description

HD Y Delay with

Respect to Falling

Edge of HSYNC

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

0

0

0

0

1

0

0

1

1

0

0

1

0

1

0

Bit 5

Bit 4

Bit 3

HD Color Delay with

Respect to Falling

Edge of HSYNC

HD CGMS

HD CGMS CRC

Bit 2

0

0

0

0

1

Bit 1

0

0

1

1

0

Bit 0

0

1

0

1

0

0

1

0

1

Register Setting

0 clock cycles

1 clock cycle

2 clock cycles

3 clock cycles

4 clock cycles

0 clock cycles

1 clock cycle

2 clock cycles

3 clock cycles

4 clock cycles

Disabled

Enabled

Disabled

Enabled

Reset

Values

0x00

Table 11. Registers 0x13 to 0x14

SR7–

SR0

0x13

Register

HD Mode

Register 4

Bit Description

HD Cr/Cb Sequence

Bit 7

Bit 6

Reserved

HD Input Format

Register Setting

Cb after falling edge of HSYNC.

1

Cr after falling edge of HSYNC.

0

1

0

0

1

HD Chroma Input

HD Mode

Register 5

Bit 0

0

0

Reserved

HD Chroma SSAF

0x14

Bit 1

0

1

Sinc Filter on DAC D, E, F

HD Double Buffering

Bit 2

0

1

0

1

HD Timing Reset

x

HD Hsync Generation 1

0

1

HD Vsync Generation1

0 must be written to this bit.

8-bit input.

10-bit input.

Disabled.

Enabled.

0 must be written to this bit.

Disabled.

Enabled.

4:4:4

4:2:2

Disabled.

Enabled.

A low-high-low transition resets

the internal HD timing counters.

Refer to the HSYNC/VSYNC

Output Control section.

0

1

HD Blank Polarity

Reserved

HD VSYNC/Field Input

1

2

BLANK active high.

1

BLANK active low.

0

1

0

Macrovision disabled.

Macrovision enabled.

0 must be written to these bits.

0 = field input.

1

1 = VSYNC input.

HD Macrovision for

525p and 625p

Horizontal/Vertical

Counters 2

0

0

0

1

Update field/line counter.

Field/line counter free running.

Used in conjunction with HD_SYNC in Register 0x02, Bit 7, set to 1.

When set to 0, the horizontal/vertical counters automatically wrap around at the end of the line/field/frame of the standard selected. When set to 1, the

horizontal/vertical counters are free running and wrap around when external sync signals indicate to do so.

Rev. A | Page 28 of 88

Reset

Values

0x4C

0x00

ADV7320/ADV7321

Table 12. Register 0x15

SR7–

SR0

0x15

Register

HD Mode

Register 6

Bit Description

Reserved

HD RGB Input

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 1

0

1

HD Sync on PrPb

0

1

HD Color DAC Swap

0

1

HD Gamma Curve A

HD Gamma Curve B

HD Gamma Curve Enable

0

1

0

1

HD Adaptive Filter Mode

HD Adaptive Filter Enable

Bit 2

0

1

0

1

Rev. A | Page 29 of 88

Bit 0

0

Register Setting

0 must be written to this bit.

Disabled.

Enabled.

Disabled.

Enabled.

DAC E = Pb; DAC F = Pr.

DAC E = Pr; DAC F = Pb.

Gamma Curve A.

Gamma Curve B.

Disabled.

Enabled.

Mode A.

Mode B.

Disabled.

Enabled.

Reset

Values

0x00

ADV7320/ADV7321

Table 13. Registers 0x16 to 0x37

SR7–

SR0

0x16

0x17

Register

HD Y Level 1

0x18

HD Cb Level1

0x19

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

0x20

Bit Description

HD Cr Level1

HD Sharpness

Filter Gain

1

HD CGMS Data 0

HD CGMS Data 1

HD CGMS Data 2

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma A

HD Gamma B

HD Gamma B

HD Gamma B

HD Gamma B

HD Gamma B

HD Gamma B

HD Gamma B

HD Gamma B

HD Gamma B

HD Gamma B

Bit 6

x

x

Bit 5

x

x

Bit 4

x

x

Bit 3

x

x

Bit 2

x

x

Bit 1

x

x

Bit 0

x

x

Register

Setting

Y level value

Cr level value

Reset

Values

0xA0

0x80

x

x

x

x

x

x

x

x

Cb level value

0x80

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

HD Sharpness Filter Gain Value A

HD Sharpness Filter Gain Value B

0x21

0x22

0x23

0x24

0x25

0x26

0x27

0x28

0x29

0x2A

0x2B

0x2C

0x2D

0x2E

0x2F

0x30

0x31

0x32

0x33

0x34

0x35

0x36

0x37

Bit 7

x

x

HD CGMS Data Bits

HD CGMS Data Bits

HD CGMS Data Bits

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve A Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

HD Gamma Curve B Data Points

0

0

…

0

1

…

1

0

C15

C7

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

…

1

0

…

1

0

C14

C6

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

…

1

0

…

1

0

C13

C5

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

For use with internal test pattern only.

Rev. A | Page 30 of 88

0

1

…

1

0

…

1

0

C12

C4

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

…

0

1

…

1

0

0

…

1

0

…

1

0

0

…

1

0

…

1

0

1

…

1

0

…

1

C19

C11

C3

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

C18

C10

C2

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

C17

C9

C1

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

C16

C8

C0

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

Gain A = 0

Gain A = +1

…

Gain A = +7

Gain A = −8

…

Gain A = −1

Gain B = 0

Gain B = +1

…

Gain B = +7

Gain B = −8

…

Gain B = −1

CGMS 19 to 16

CGMS 15 to 8

CGMS 7 to 0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

B0

B1

B2

B3

B4

B5

B6

B7

B8

B9

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

ADV7320/ADV7321

Table 14. Registers 0x38 to 0x3D

SR7–

SR0

0x38

0x39

Register

HD Adaptive Filter

Gain 1

HD Adaptive Filter

Gain 2

HD Adaptive Filter

Gain 3

0x3C

0x3D

HD Adaptive Filter

Threshold A

HD Adaptive Filter

Threshold B

HD Adaptive Filter

Threshold C

0

0

…

1

0

…

1

x

0

0

…

1

0

…

1

x

0

1

…

1

0

…

1

x

x

x

x

x

x

x

x

x

x

x

x

x

Threshold B

0x00

x

x

x

x

x

x

x

x

Threshold C

0x00

Bit 6

Bit 5

Bit 4

HD Adaptive Filter

Gain 1, Value B

0

0

…

0

1

…

1

0

0

…

1

0

…

1

0

0

…

1

0

…

1

0

1

…

1

0

…

1

HD Adaptive Filter

Gain 2, Value A

0

0

…

0

1

…

1

0

0

…

1

0

…

1

0

0

…

1

0

…

1

HD Adaptive Filter

Threshold A

HD Adaptive Filter

Threshold B

HD Adaptive Filter

Threshold C

Bit 3

0

0

…

0

1

…

1

Bit 2

0

0

…

1

0

…

1

Bit 1

0

0

…

1

0

…

1

Bit 0

0

1

…

1

0

…

1

0

0

…

0

1

…

1

0

0

…

1

0

…

1

0

0

…

1

0

…

1

0

1

…

1

0

…

1

0

0

…

0

1

…

1

0

0

…

1

0

…

1

0

0

…

1

0

…

1

0

1

…

1

0

…

1

0

1

…

1

0

…

1

HD Adaptive Filter

Gain 3, Value A

HD Adaptive Filter

Gain 3, Value B

0x3B

0

0

…

0

1

…

1

x

Bit 7

HD Adaptive Filter

Gain 2, Value B

0x3A

Register

Setting

Gain A = 0

Gain A = +1

…

Gain A = +7

Gain A = −8

…

Gain A = −1

Gain B = 0

Gain B = +1

…

Gain B = +7

Gain B = −8

…

Gain B = −1

Gain A = 0

Gain A = +1

…

Gain A = +7

Gain A = −8

…

Gain A = −1

Gain B = 0

Gain B = +1

…

Gain B = +7

Gain B = −8

…

Gain B = −1

Gain A = 0

Gain A = +1

…

Gain A = +7

Gain A = −8

…

Gain A = −1

Gain B = 0

Gain B = +1

…

Gain B = +7

Gain B = −8

…

Gain B = −1

Threshold A

Bit Description

HD Adaptive Filter

Gain 1, Value A

Rev. A | Page 31 of 88

Reset

Values

0x00

0x00

0x00

0x00

ADV7320/ADV7321

Table 15. Registers 0x3E to 0x43

SR7–

SR0

0x3E

0x3F

0x40

Register

SD Mode Register 0

Bit Description

Reserved

Reserved

SD Standard

Bit 7

Bit 6

Bit 5