Reconfigurable switched capacitor power converter techniques

advertisement

USOO8817501B1

(12) United States Patent

(10) Patent N0.:

Low et al.

(54)

(45) Date of Patent:

RECONFIGURABLE SWITCHED

5,132,606 A

CAPACITOR POWER CONVERTER

,

_

_

Apphcant: Arctic Sand Technologies, Cambridge,

eynar

5,801,987 A

9/1998

Dinh et a1.

5,907,484 A

5/1999 Kowshik e1 31,

FOREIGN PATENT DOCUMENTS

JP

JP

10327573

11235053

Oscar Blyde, Melrose, MA (US)

OTHER PUBLICATIONS

Cambridge, MA (US)

Subject to any disclaimer, the term Ofthjs

patent is extended or adjusted under 35

O. Abutbul et a1. “Step-Up Switching-Mode Converter With High

Voltage Gain Using a Switched-Capacitor Circuit” IEEE Transac

tions on Circuits and Systems 1., vol. 50, pp. 1098-1102, Aug. 2003.

U.S.C. 154(b) by 0 days.

)

(22)

A

pp

(Continued)

1. N .: 13/846 046

0

’

Filed;

12/1998

8/1999

(Continued)

(73) Assignee: Arctic Sand Technologies, Inc.,

21

a .

Kanda et a1. .................. .. 363/60

(Continued)

(Us); Gregory SlCZ?SZyIlskis Hollis’ NH

(US); Jeff Summit, Jefferson, MA (US);

(

e

6/1998

David M. Giuliano, Brookline, MA

Notice;

$013M? t l

,

5,761,058 A *

MA (Us)

(72) Inventors: Aichen LoW, Arlington, MA (US);

(*)

Aug. 26, 2014

7/1992 Herbert

2

TECHNIQUES

(71)

US 8,817,501 B1

Primary Examiner * Adolf Berhane

Man 18, 2013

Assistant Examiner * Gary Nash

(74) Attorney, Agent, or Firm * Occhiuti & Rohlicek LLP

Related US. Application Data

(63)

Continuation of application No. 13/839,315, ?led on

(57)

Mar. 15, 2013.

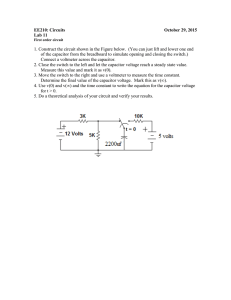

An apparatus for converting a ?rst voltage into a second

ABSTRACT

voltage includes a recon?gurable switched capacitor power

(51)

(52)

Int- ClH02M3/18

H02M 7/00

U-s- ClU.SPC .........

(58)

converter having a selectable conversion gain. converter

includes a cascade multiplier switched capacitor network

having capacitors, each of which electrically connects to a

(2006-01)

(200601)

stack node and to a phase node. A controller causes the

...... ......................... .. 363/60; 363/59

Fleld 0f ClaSSI?catlon searCh

USPC

network to transition between ?rst and second Operation

modes. In the ?rst mode, at least one capacitor is isolated from

.... ..~ ............................. .. 363/59, 60; 527/536

see apphcanon ?le for complete searCh hIStOrY

a Charge transfer path Ofthe recon?gurable switched capaci_

tor power converter. Consequently, in the ?rst mode of opera

References Cited

_

tion, the power converter operates with a ?rst gain. In the

second mode, the power converter operates with a second

U.S. PATENT DOCUMENTS

conversion gain. Meanwhile, a third voltage across the at least

(56)

4,214,174 A

4,812,961 A

one capacitor is free to assume any value.

7/1980 Dickson

3/1989 Essaffet a1.

18 Claims, 17 Drawing Sheets

Recon?guration

22 .r

Block

A1

A2

Controller

Bl

24

A3

F M

_

28 J

30..

\

/

ws

SlP

26

US 8,817,501 B1

Page 2

(56)

References Cited

U.S. PATENT DOCUMENTS

5,978,283

6,107,864

6,476,666

6,486,728

6,501,325

6,504,422

6,759,766

6,927,441

6,980,181

7,145,382

7,190,210

7,224,062

7,239,194

7,250,810

7,408,330

7,511,978

7,595,682

7,724,551

7,777,459

7,782,027

7,786,712

7,807,499

7,812,579

7,928,705

7,999,601

8,018,216

8,040,174

8,048,766

8,111,054

8,159,091

8,193,604

8,212,541

8,339,184

8,350,549

8,384,467

8,395,914

8,456,874

8,503,203

2003/0169096

2003/0227280

2004/0041620

2005/0007184

2005/0207133

2007/0146052

2007/0210774

2007/0230221

2008/0150621

2008/0157732

2008/0157733

2008/0239772

2009/0102439

2009/0257211

2009/0278520

2010/0110741

2010/0140736

2010/0202161

2010/0214746

2010/0244189

A

A

B1

B2

B1

B1

B2

B2

B2

B2

B2

B2

B2

B1

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B2

B1

B2

B2

B1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

A1

11/1999

8/2000

11/2002

11/2002

12/2002

1/2003

7/2004

8/2005

12/2005

12/2006

3/2007

5/2007

7/2007

7/2007

8/2008

3/2009

9/2009

5/2010

8/2010

8/2010

8/2010

10/2010

10/2010

4/2011

8/2011

9/2011

10/2011

11/2011

2/2012

4/2012

6/2012

7/2012

12/2012

1/2013

2/2013

3/2013

6/2013

8/2013

9/2003

12/2003

3/2004

1/2005

9/2005

6/2007

9/2007

10/2007

6/2008

7/2008

7/2008

10/2008

4/2009

10/2009

11/2009

5/2010

6/2010

8/2010

8/2010

9/2010

Hsu et al.

Fukushima et al.

Palusa et al.

Kleveland

Meng

2010/0244585

2011/0163414

2012/0146177

2012/0313602

2012/0326684

2013/0049714

2013/0094157

2013/0154600

2013/0229841

Rader et al.

Hiratsuka et al.

A1

A1

A1

A1

A1

A1

A1

A1

A1

9/2010

7/2011

6/2012

12/2012

12/2012

2/2013

4/2013

6/2013

9/2013

Tan et al.

Lin et al.

Choi et al.

Perreault et al.

Perreault et al.

Chiu

Giuliano

Giuliano

Giuliano

FOREIGN PATENT DOCUMENTS

Pappalardo et al.

Sudo

Ker et al.

Azrai et al.

Hsu

Azrai et al.

Tsen

JP

WO

WO

WO

WO

WO

Zhao

Chen et al.

Lin et al.

2010045943 A

2006093600

2009112900

2012151466

2013059446

2013096416

2/2010

9/2006

9/2009

11/2012

4/2013

6/2013

OTHER PUBLICATIONS

Yanagida et al.

Umeno et al. “A New Approach to Low Ripple-Noise Switching

Williams

Williams

Williams

Nishizawa

Williams

Hooij schuur et al.

Schlueter et al.

Kakehi

Likhterov

Converters on the Basis of Switched-Capacitor Converters” IEEE

International Symposium on Circuits and Systems, vol. 2, pp. 1077

1080, Jun. 1991.

Joly et al.

Yen et al.

Yeates

Lin et al.

Perreault et al.

Kok et al.

Kitabatake

O’keeffe et al.

Klootwijk et al.

Singer et al. .................. .. 363/60

Szczeszynski et al.

Hsu et al. .................... .. 327/536

Vinciarelli

D’Angelo et al.

Kamijo

Pavier et al.

Byeon ......................... .. 327/536

Axelrod et al. “Single-switch single-stage switched-capacitor buck

converter”, Proc. ofNORPIE 2004, 4th Nordic Workshop on Power

and Industrial Electronics, Jun. 2004.

Sun et al. “High Power Density, High Ef?ciency System Two-Stage

Power Architecture for Laptop Computers”, Power Electronics Spe

cialists Conference, pp. 1-7, Jun. 2006.

R. D. Middlebrook, “Transformerless DC-to-DC Converters with

Large Conversion Ratios” IEEE Transactions on Power Electronics,

vol. 3, No. 4, pp. 484-488, Oct. 1988.

Wood et a1, “Design, Fabrication and Initial Results of a 2g Autono

mous Glider” IEEE Industrial Electronics Society, pp. 1870-1877,

Nov. 2005.

T. A. Meynard, H. Foch, “Multi-Level Conversion: High Voltage

Choppers and Voltage-Source Inverters,” IEEE Power Electronics

Specialists Conference, pp. 397-403, 1992.

Pilawa-Podgurski et al. “Merged Two-Stage Power Converter Archi

tecture with Soft Charging Switched-Capacitor Energy Transfer”

39th IEEE Power Electronics Specialists Conference, 2008.

Han et al. “A New Approach to Reducing Output Ripple in Switched

Capacitor-Based Step-Down DC-DC Converters” IEEE Transac

Kimura et al.

Lim et al.

Lesso et al.

Williams

Williams

Oraw et al.

Williams

Kontani et al.

Perreault et al.

Lin et al.

Lin et al.

Sims et al.

Lot? et al.

tions on PowerElectronics, vol. 21, No. 6, pp. 1548-1555 Nov. 2006.

Lei et al. “Analysis of Switched-capacitor DC-DC Converters in

Soft-charging Operation” 14”“ IEEE Workshop on Control and Mod

elingfor Power Electronics, pp. 1-7, Jun. 23, 2013.

Ng et al. “Switched Capacitor DC-DC Converter: Superior where the

Buck Converter has Dominated” PhD Thesis, UC Berkeley, Aug. 17,

Klootwijk et al.

* cited by examiner

201 1.

R. Pilawa-Podgurski and D. Perreault, “Merged Two-Stage Power

Converter with Soft Charging Switched-Capacitor Stage in 180 nm

CMOS,” IEEE Journal of Solid-State Circuits, vol. 47, No. 7, pp.

1557-1567, Jul. 2012.

US. Patent

Aug. 26, 2014

20A

L,

Sheet 1 0f 17

1

ENl —>\

V'

26

US 8,817,501 B1

l

EN2 —>\

l

EN3 —>\

C4

c5

cs

\I

\I

\l

/|

/l

/l

V0

01

02

03

D4

05

D6

H

N

Pl

N

H

H

/\ C1

/\ C2

RL

r\ C3

EN1 T—I>, EN2 9, EN3 51>,

P1

-

-

FIG. 1A (Prior Art)

205

K.

V'

ENl —>\

D11

ENZ —>\

D12

ENS —§\

D13

26

014

N

FIG. IB (Prior Art)

V0

US. Patent

Aug. 26, 2014

Sheet 2 0f 17

US 8,817,501 B1

*

it

M

m

¢

1%

\\.-

r.W

M

|_|

H

1—»

R

@w

3

NW

mm

Hm

mm

i?mwV_86>0m_E5

#29.NZHzo>@2m2

cosmLi ucwh

h

{w

/_H

?m/

U8Nu3hamIE

/\r\ E(C

Nas?“

| m<N<H<

1. . om

.14/

Q:

I

n.

1.

..

US. Patent

Aug. 26, 2014

Sheet 3 0f 17

US 8,817,501 B1

221

A2 0—/

A1

FIG. 3A

AZ o—o/D—

SA1

5A2

FIG. 3B

A1

US. Patent

Aug. 26, 2014

Sheet 4 0f 17

US 8,817,501 B1

US. Patent

Aug. 26, 2014

US 8,817,501 B1

Sheet 5 0f 17

~

m

WN

m

@N

,

cotmg3s:a2u.w60

E 1mm

neww

JNN28EE_>_8a

\4/“A289805lbRm.52m0mmmmma9%ToQO

8w8mmm.“.

| m<2

2

"5%

o>_>£282M:2£2#28. £2$2 1N88m8wSmNE2%5.mmN8:8.,

M

1&3

. "am

~

An

E

VAv“HANuMnm8“8@81%

65%m

US. Patent

Aug. 26, 2014

US 8,817,501 B1

Sheet 6 0f 17

“A9858

f\

,\“mm

“.2“:8“E

mom.0. .r“

/ f\r\

mM5&2#28&2$528". £2$2 mm3%Sm5N32%aS»NNWHQNS3 r VAMum8Su

mmm0mm0%m3,Smmm082%m3 5o>£2

S8awnCQ2

$3“AMMNH66¢30nwuQmu26

5w .

m

m8m56ms“3NuMAMnVA81

hamE8

I

|m<~<2

cozL?ws=mbu

T3NN2V258E

Q

1%

US. Patent

Aug. 26, 2014

Sheet 7 0f 17

V;

US 8,817,501 B1

SwitcheId Cafpacitor

"'

Clrcult

S

'

:1

9

SE

V2

____CB2

251;,"

EN 1 —>

S

8

V1

vc

/\

,Ifgl

Old con version-gain E New conversion-gain

State 1

State 2

EN1

FIG. 7B

US. Patent

Aug. 26, 2014

Sheet 8 0f 17

01

D2

8

V6

(1,

5

42

Switched

Capacitor Circuit

FIG. 8

US 8,817,501 B1

US. Patent

Aug. 26, 2014

Sheet 9 0117

US 8,817,501 B1

VDRV

TP

VON

WC)

'

ENZ

—

i

K)

VDRV

W

VON

M74

TN

FIG. 9B

VDRV

TP

0

M76

VB

VON

1-

(—

ENZ

56

U

TN

FIG. 9C

US. Patent

Aug. 26, 2014

Sheet100f17

US 8,817,501 B1

a

_,...........-..q

QM

Eum3zo5bc2u

.YUQNE

US. Patent

Aug. 26, 2014

Sheet 11 0117

US 8,817,501 B1

3

3

3H

3

—H Nlc

AVZ

:

>—{ MP1

+

vuv '—

'— + AVl

f;

MNl

I

5

<

FIG. 10B

:1 N5c

US. Patent

Aug. 26, 2014

US 8,817,501 B1

Sheet 12 0f 17

SW1

1 Nlc

SW2

1 N2c

SW3

0—H NSC

SW4

1 N4c

SW5

/

MP2

LFIG. 10C

:1 NSC

US. Patent

Aug. 26, 2014

Old M

State 21

F51

Sheet 14 0117

5 New M 5

'

F52

'

US 8,817,501 B1

New M

5

F51

FIG. 12

Transition

Old M

New M

Interval

:

:

:

t0

t1

t2

time

FIG. 13

>

US. Patent

Aug. 26, 2014

Sheet 15 0f 17

US 8,817,501 B1

.MDEN:E

ExNE

US. Patent

Aug. 26, 2014

Sheet160f17

US 8,817,501 B1

v6~@Nm

US 8,817,501 B1

1

2

RECONFIGURABLE SWITCHED

CAPACITOR POWER CONVERTER

requires the use of large bypass transistors. Furthermore, the

pump capacitors C1-C3 that get bypassed are charged to a

voltage that is equal to the input voltage VI minus a diode

TECHNIQUES

voltage drop. For example, when the ?rst enable signal EN1

is high the positive terminal of the pump capacitor C1 is

CROSS REFERENCE TO RELATED

APPLICATION

biased to a voltage that is one diode drop below the input

voltage VI while the negative terminal of the pump capacitor

This application is a continuation of US. Ser. No. 13/839,

315, ?led Mar. 15, 2013. The content of the aforementioned

C1 is biased to ground.

When the number of capacitors in the charge transfer path

changes, the total amount of charge prior to a recon?guration

event equals the total amount of charge after the recon?gu

application is incorporated herein in its entirety.

FIELD OF DISCLOSURE

ration event due to charge conservation. This means that the

charge in each capacitor prior to the recon?guration event

The present inventive subject matter relates to techniques

for recon?guring a switched capacitor power converter.

redistributes among the remaining capacitors upon the recon

?guration event. Furthermore, the voltage across each capaci

tor before and after the recon?guration event also changes

BACKGROUND

A switch-mode power converter is a speci?c type of power

converter that produces an output voltage by switching

energy storage elements (i.e. inductors and capacitors) into

different electrical con?gurations using a switch network. A

switched capacitor power converter is a type of switch-mode

power converter that primarily utilizes capacitors to transfer

energy. In such converters, also known as switched capacitor

circuits, the number of capacitors and switches increases as

the transformation ratio or conversion-gain increases. A

20

proportionally to the conversion-gain and the input voltage

VI. The polarity of each capacitor voltage change depends on

whether the conversion-gain of the switched capacitor circuit

is either increasing or decreasing.

A challenge with recon?gurable cascade multipliers lies in

the design complexity of operating low-voltage transistors

25

robustly with either a high input voltage range or a high output

voltage range. Furthermore, current and/or voltage transients

that occur upon each change in the conversion-gain can have

signi?cant impact in terms of input electromagnetic interfer

switched capacitor circuit that has more than one conversion

ence, transistor operation, and robustness.

gain (i.e. mode) is often refer to as a multi-mode switched

capacitor circuit

sion-gain using low-voltage transistors. As used herein, con

version-gain represents a voltage gain if the switched capaci

tor circuit produces an output voltage that is larger than the

In one aspect, the invention features an apparatus for con

verting a ?rst voltage into a second voltage. Such an apparatus

includes a recon?gurable switched capacitor power converter

35

input voltage or a current gain if the switched capacitor circuit

produces an output voltage that is smaller than the input

voltage. Energy is transferred from the input to the output by

cycling the cascade multiplier network through different

topological states. Charge is transfer from the input voltage to

the output voltage via a charge transfer path. The number and

con?guration of the capacitors in each topological state sets

switched capacitor power converter includes a ?rst cascade

capacitors, each of which is electrically connected, at a ?rst

terminal thereof, to a stack node associated with the capacitor

40

outer capacitor, a second outer capacitor, and at least one

inner capacitor between the ?rst outer capacitor and the sec

ond outer capacitor. A plurality of stack switches are between

45

50

power converter operates with a ?rst conversion gain, in the

55

free to assume any value.

60

In some embodiments, during operation, the third voltage

is between the ?rst voltage and the second voltage.

Among the embodiments of the apparatus are those that

also include a pre-charge circuit. This pre-charge circuit is

con?gured to charge the at least one capacitor to a speci?ed

Unfortunately, each of the cascade multipliers 20A, 20B

ef?ciency of the cascade multipliers 20A, 20B and/or

second mode of operation, the recon?gurable switched

capacitor power converter operates with a second conversion

gain, and a third voltage across the at least one capacitor is

input voltage VI; and so on.

require a circuit coupled to the positive terminal of each of the

pump capacitors C1-C3 and a circuit coupled to the negative

terminal of each of the pump capacitors C1-C3 to change the

conversion- gain. The additional circuitry either decreases the

path of the recon?gurable switched capacitor power con

verter, the charge transfer path extending between the ?rst

voltage and the second voltage. Consequently, in the ?rst

mode of operation, the recon?gurable switched capacitor

VI. The conversion-gain can be selected based upon ?rst,

second, and third enable signals EN1, EN2, EN3. When the

?rst enable signal EN1 is high the output voltage V0 is three

times the input voltage VI; when the ?rst and second enable

signals EN1, EN2 are high the output voltage is two times the

nodes of adj acent capacitors from a plurality of capacitors. A

controller causes the ?rst cascade multiplier switched capaci

tor network to transition between a ?rst mode of operation

and a second mode of operation. In the ?rst mode of opera

tion, at least one capacitor is isolated from a charge transfer

Both of the cascade multipliers 20A, 20B can produce a

maximum output voltage VO of four times the input voltage

and at a second terminal thereof to a phase node associated

with the capacitor. This plurality of capacitors includes a ?rst

multiplier network, the conversion-gain can be modi?ed.

cascade multiplier that includes a phase voltage P1, diodes

D1-D6, pump capacitors C1-C3, and dc capacitors C4-C6. In

contrast, the cascade multiplier 20B is a symmetric cascade

multiplier that includes phase voltages P1-P2, diodes D11

D14, and pump capacitors C1-C3.

having a selectable conversion gain. This recon?gurable

multiplier switched capacitor network having a plurality of

the conversion-gain. Therefore, by recon?guring the cascade

FIGS. 1A-1B illustrate two known recon?gurable cascade

multipliers 20A, 20B that receive an input voltage VI from a

voltage source 26 and provide an output voltage V0 to a load

RL. The cascade multiplier 20A is a single-phase asymmetric

SUMMARY

30

Cascade multipliers are a family of multi-stage switched

capacitor power converters that can provide a high conver

voltage.

65

In some embodiments, the at least one capacitor is an outer

capacitor. However, in other embodiments, the at least one

capacitor is an inner capacitor.