An Evaluation of Current and Advanced Switching Devices

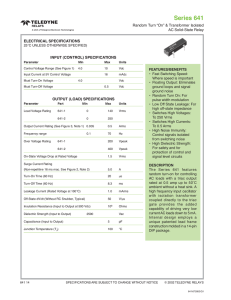

advertisement