Electrical Engineering (added 9/18/2013)

advertisement

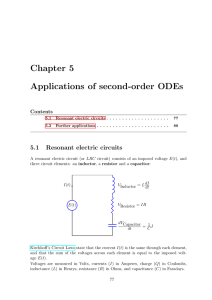

FE: Electric Circuits © C.A. Gross EE1- 1 FUNDAMENTALS OF ENGINEERING (FE) EXAMINATION REVIEW ELECTRICAL ENGINEERING Charles A. Gross, Professor Emeritus Electrical and Comp Engineering Auburn University Broun 212 334.844.1812 gross@eng.auburn.edu www.railway-technology.com FE: Electric Circuits © C.A. Gross EE1- 2 1 EE Review Problems 1. 2. 3. 4. dc Circuits Complex Numbers ac Circuits 3-phase Circuits 1st Order Transients Control Signal Processing Electronics Digital Systems FE: Electric Circuits We will discuss these. We may discuss these as time permits © C.A. Gross EE1- 3 EE1- 4 1. dc Circuits: Find all voltages, currents, and powers. FE: Electric Circuits © C.A. Gross 2 Solution The 8 and 7 resistors are in series: R1 8 7 15 R1 and 10 are in parallel: 1 R2 1 1 10 R1 10 R1 6 10 R1 FE: Electric Circuits © C.A. Gross EE1- 5 EE1- 6 Solution 4 and R2 are in series: Rab 4 R 2 10 L : Ia Vab 100 10 A Rab 10 V4 4 I a 40V (L) V10 100 40 60V FE: Electric Circuits KVL © C.A. Gross 3 Solution Ic V10 60 6A 10 10 L KCL : I b I a I c 10 6 4 A V8 8 I b 32V ( L) V7 7 I b 28V ( L) FE: Electric Circuits © C.A. Gross EE1- 7 Absorbed Powers... R4 I a2 4 10 400W 2 R10 I 10 6 360W R7 I b2 7 4 112W 2 R8 I 8 4 128W 2 b In General: 2 2 c PABS = PDEV (Tellegen's 2 Total Absorbed Power 1000W Theorem) Power Delivered by Source Vs I a 100 10 1000W FE: Electric Circuits © C.A. Gross EE1- 8 4 2. Complex Numbers Consider x2 2 x 5 0 2 (2) 2 4(1)(5) 2 16 x 2 1 2 4 1 1 1 2 1 2 The numbers "1 2 1" are called complex numbers 9 Summer 2008 The “I” (j) operator Math Department.... ECE Department Define i 1 Define j 1 x 1 j2 x 1 2i We choose ECE notation! Terminology… Rectangular Form..... Z X jY a complex number X e Z real part of Z Y Im Z imaginary part of Z 10 Summer 2008 5 Polar Form Math Department..... Z R e i a complex number R | Z | modulus of Z arg Z argument of Z radians ECE Department..... Z Z a complex number Z | Z | magnitude of Z ang Z angle of Z degrees 11 The Argand Diagram It is useful to plot complex numbers in a 2-D cartesian space, creating the so-called Argand Diagram (Jean Argand (1768-1822)). “imaginary” axis (Y) +2 Z X jY 1 j 2 “real” axis (X) +1 12 Summer 2008 6 Conversions Retangular Polar Z Y X2 Y2 Y X tan 1 Z Polar Retangular..... X Z cos X Y Z sin 13 Summer 2008 Example: Z 3 j4 X e Z 3 4 Y Im Z 4 Rect Polar..... 5 0 Z 32 42 5 3 4 Summer 2008 tan 1 0.9273 rad 53.10 3 14 7 Conjugate Z X jY Z Z * conjugate of Z X jY Z Example... (3 j 4)* 3 j 4 5 53.10 15 Summer 2008 Addition (think rectangular) A a jb A 3 j 4 553.10 B c jd B 5 j12 13 67.40 A B (a jb) (c jd ) (a c ) j (b d ) A B (3 j 4) (5 j12) (3 5) j (4 12) 8 j8 16 Summer 2008 8 Multiplication (think polar) A a jb A 3 j 4 553.10 B c jd B 5 j12 13 67.40 A B ( A ) ( B ) A B( ) A B (553.10 ) (13 67.40 ) (5) (13) (53.10 67.40 ) 65 14.30 17 Summer 2008 Division (think polar) A a jb A 3 j 4 553.10 B c jd B 5 j12 13 67.40 A A A ( ) B B B A 553.10 5 53.10 67.40 0 B 13 63.4 13 0.3846120.50 18 Summer 2008 9 Multiplication (rectangular) A B (a jb) c jd ac bd j ad bc A B (3 j 4) (5 j12) (15 48) j ( 36 20) 63 j16 65 14.30 19 Summer 2008 EL EC 38 10 Addition (polar) 553.10 Complex number addition is the same as "vector addition"! 20 Summer 2008 11.31 450 EL 13 67.40EC 38 10 10 3. ac Circuits i(t) Find "everything" in the given circuit. 8 + v(t) - 0.663 mF 26.53 mH v (t ) 141.4cos(377 t ) V FE: Electric Circuits © C.A. Gross EE1- 21 Frequency, period v (t ) 141.4cos(377 t ) V (radian) frequency 377 rad / s (cyclic) frequency f Period FE: Electric Circuits 60 Hz 2 1 1 16.67 ms f 60 © C.A. Gross EE1- 22 11 The ac Circuit To solve the problem, we convert the circuit into an "ac circuit": R, L, C elements Z (impedance) v , i sources V , I (phasors) R : Z R R j0 8 j0 L : Z L 0 j L 0 j (0.377)(26.53) 0 j10 C : ZC 0 1 1 0 j 0 j4 0.377(0.663) j C FE: Electric Circuits © C.A. Gross EE1- 23 The Phasor v (t ) VMAX cos( t ) To convert to a phasor... For example.. V FE: Electric Circuits V VMAX 2 v (t ) 141.4cos(377 t ) VMAX 2 100 0o © C.A. Gross EE1- 24 12 The "ac circuit" I L(ac ) : VR 1000 I VC FE: Electric Circuits 100 8 j10 j 4 10 36.9o VL V Z i (t ) 14.14 cos(377 t 36.9o ) © C.A. Gross EE1- 25 Solving for voltages VR Z R I (8)(10 36.9o ) 80 36.9o V v R (t ) 113.1 cos(377 t 36.9o ) VC Z C I ( j 4)(10 36.9o ) 40 126.9o V vC (t ) 56.57 cos(377t 126.9o ) VL Z L I ( j10)(10 36.9o ) 10053.1o V v L (t ) 141.4 cos(377 t 53.1o ) FE: Electric Circuits © C.A. Gross EE1- 26 13 Absorbed powers S V I * P jQ S R VR I * 80 36.9o (10 36.9o )* 800 j 0 SC VC I * 40 126.9o (10 36.9o )* 0 j 400 S L VL I * 10053.1o (10 36.9o )* 0 j1000 STOT S R SC S L 800 j 600 PTOT 800 watts; QTOT 600 var s; STOT | STOT | 1000 VA FE: Electric Circuits © C.A. Gross EE1- 27 Delivered power S S VS I * 100 0o (10 36.9o )* 800 j 600 S S STOT 800 j 600 PS PTOT 800 watts QS QTOT 600 var s In General: PABS = PDEV QABS = QDEV (Tellegen's Theorem) FE: Electric Circuits © C.A. Gross EE1- 28 14 The Power Triangle S 800 j 600 S = 1000 VA Q = 600 var = 36.90 V 1000o I 10 36.9o P = 800 W power factor pf FE: Electric Circuits P cos( ) 0.8 lagging S © C.A. Gross EE1- 29 Leading, Lagging Concepts Leading Case I Q<0 V Lagging Case V Q>0 I FE: Electric Circuits © C.A. Gross EE1- 30 15 A Lagging pf Example V 7.200 kV jX R jX j 43.2 R 103.68 FE: Electric Circuits © C.A. Gross EE1- 31 Currents I V IR V R IR IL IL jX V 7.2 69.44 A R 103.68 I IR IL V 7.2 j166.7 A jX j 43.20 FE: Electric Circuits I 69.44 j166.7 I 180.6 67.380 A © C.A. Gross EE1- 32 16 pf cos cos 67.360 0.3845 Powers I IL IR V R 1300 kVA jX 1200 k var S R V I R * 500 kW j 0 S L V I L * 0 j1200 k var SS V I * S R S L 500 kW SS 500 j1200 130067.380 FE: Electric Circuits EE1- 33 © C.A. Gross Add Capacitance I I C j125 jX C V IR IC IL IC I R 69.44 V 7.2 j125 A jX j 57.6 I L j166.7 I I R I L IC I 69.44 j166.7 j125 81 310 A FE: Electric Circuits © C.A. Gross EE1- 34 17 Powers pf cos cos 310 0.8575 900 kvar 1200 kvar SC V I C * 0 j 900 kvar 583.1 kVA SS V I * S R S L SC SS 500 j1200 j 900 500 kW SS 583.1310 kVA FE: Electric Circuits © C.A. Gross EE1- 35 Observations By adding capacitance to a lagging pf (inductive) load, we have significantly reduced the source current., without changing P! Before I 180.6 A; pf 0.3845 I 81 A; pf 0.8575 After Note that: low pf, high current; high pf, low current; If we consider the “source” in the example to represent an Electric Utility, this reduction in current is of major practical importance, since the utility losses are proportional to the square of the current. FE: Electric Circuits © C.A. Gross EE1- 36 18 Observations That is, by adding capacitance the utility losses have been reduced by almost a factor of 5! Since this results in significant savings to the utility, it has an incentive to induce its customers to operate at high pf. This leads to the “Power Factor Correction” problem, which is a classic in electric power engineering and is extremely likely to be on the FE exam. We will be using the same numerical data as we did in the previous example. Pretty clever, eh’ what? FE: Electric Circuits EE1- 37 © C.A. Gross The Power Factor Correction problem Utility Load pf correcting capacitance An Electric Utility supplies 7.2 kV to a customer whose load is 7.2 kV 1300 kVA @ pf = 0.3845 lagging. The utility offers the customer a reduced rate if he will “correct” (“improve” or “raise”) his pf to 0.8575. Determine the requisite capacitance. FE: Electric Circuits © C.A. Gross EE1- 38 19 PF Correction: the solution 1. Draw the load power triangle. 1300 kVA @ pf = 0.3845 lagging. pf 0.3845 cos 67.380 S LOAD S 130067.38 1200 kvar 0 S LOAD 500 j1200 Because the pf is lagging, the load is inductive, and Q is positive. Therefore we must add negative Q to reduce the total, which means we must add capacitance. 67.380 500 kW FE: Electric Circuits © C.A. Gross EE1- 39 PF Correction: the solution 2. We need to modify the source complex power so that the pf rises to 0.8575 lagging. pf 0.8575 cos 310 Closing the switch (inserting the capacitors) SS 500 j1200 jQC 500 j 1200 QC Let QX 1200 QC Therefore SS 500 jQX S S 310 kVA Then Tan FE: Electric Circuits QX Tan 310 0.6 500 © C.A. Gross EE1- 40 20 PF Correction: the solution QX 0.6 500 QX 300 kvar QC 1200 Q X 900 kvar 900 kvar The new source power triangle 1200 kvar Install 900 kvar of 7.2 kV Capacitors 300 kvar 500 kW FE: Electric Circuits © C.A. Gross EE1- 41 4. Three-phase ac Circuits Although essentially all types of EE’s use ac circuit analysis to some degree, the overwhelming majority of applications are in the high energy (“power”) field. It happens that if power levels are above about 10 kW, it is more practical and efficient to arrange ac circuits in a “polyphase” configuration. Although any number of “phases” are possible, “3-phase” is almost exclusively used in high power applications, since it is the simplest case that achieves most of the advantage of polyphase. It is virtually certain that some 3-phase problems will appear on the FE and PE examinations, which is why 3-phase merits our attention. 21 A single-phase ac circuit a + n Generator Line Load “a” is the “phase” conductor “n” is the “neutral” conductor For a given load, the phase a conductor must have a crosssectional area “A”, large enough to carry the requisite current. Since the neutral carries the return current, we need a total of “2A worth” of conductors. Tripling the capacity + + + Ia Ib Ic In If I a I b I c I then I n 3I We need a total of A + A +A + 3A = 6A conductors. 22 But what if the currents are not in phase? Suppose I a I 00 I b I 1200 I c I 1200 Then I n I a I b I c I 00 I 1200 I 1200 I n I 1 j0 0.5 j 0.866 0.5 j0.866 I n I 1.0 0.5 0.5) j(0.0 0.866 0.866 I (0 j 0) 0 Now we only need a total of A + A +A + 0 = 3A conductors! A 50% savings! The 3-Phase Situation FE: Electric Circuits © C.A. Gross EE1- 46 23 "Balanced" voltage means equal in magnitude, 120o separated in phase v an ( t ) V max cos( t ) 2 V cos( t ) vbn ( t ) V max cos( t 120 0 ) 2 V cos( t 120 0 ) vcn ( t ) V max cos( t 120 0 ) 2 V cos( t 120 0 ) Van V 00 Vbn V 1200 Vcn V 1200 FE: Electric Circuits © C.A. Gross EE1- 47 The “Line” Voltages By KVL Vab Van Vbn 1 3 0 Vab V 00 V 1200 V 1 j 0 j V 330 2 2 Vbc V 3 900 Vca V 31500 Vab Vbc Vca VL V 3 FE: Electric Circuits © C.A. Gross EE1- 48 24 When a power engineer says “the primary distribution voltage is 12 kV” he/she means… An Example Vab 12.47300 kV Vbc 12.47 900 kV Vab Vbc Vca VL 12.47 kV Vca 12.47 1500 kV Van Vbn Vcn Van 7.2 00 kV VL 7.2 kV 3 FE: Electric Circuits Vbn 7.2 1200 kV Vcn 7.2 1200 kV © C.A. Gross bc EE1- 49 An Important Insight…. All balanced three-phase problems can be solved by focusing on a-phase, solving the single-phase (a-n) problem, and using 3-phase symmetry to deal with b-n and c-n values! This involves judicious use of the factors 3, 3, and 1200! To demonstrate… FE: Electric Circuits © C.A. Gross bc EE1- 50 25 Recall the pf Correction Problem An Electric Utility supplies 7.2 kV to a single-phase customer whose load is 7.2 kV 1300 kVA @ pf = 0.3845 lagging. V 7.200 kV 104 j 43.2 1300 kVA 1200 kvar I I R I L 181 67 A 0 FE: Electric Circuits © C.A. Gross 500 kW bc EE1- 51 The pf Correction Problem in the 3-phase case An Electric Utility supplies 12.47 kV to a 3-phase customer whose load is 12.47 kV 3900 kVA @ pf = 0.3845 lagging. Van 7.200 kV 104 j 43.2 3900 kVA 3600 kvar I a 181 670 A 3 times bigger! 1500 kW FE: Electric Circuits © C.A. Gross 52 EE1- 26 If we want all the V’s, I’s, and S’s Van 7.2 00 kV Vab 12.47300 kV Vbn 7.2 1200 kV Vbc 12.47 900 kV Vcn 7.2 1200 kV Vca 12.47 1500 kV I a 181 670 A Sa 500 j1200 kVA I b 181 187 A Sb 500 j1200 kVA I c 181 53 A Sc 500 j1200 kVA 0 0 FE: Electric Circuits © C.A. Gross EE1- PF Correction: the 3ph solution Install 2700 kvar of Capacitance. 2700 kvar 3600 kvar The circuitry in the 3phase case is a bit more complicated. There are two possibilities…. 900 kvar 1500 kW FE: Electric Circuits © C.A. Gross EE1- 54 27 The wye connection…. S O U R C E a L O A D b c n Install three 900 kvar 7.2 kV wye-connected Capacitors. FE: Electric Circuits © C.A. Gross EE1- 55 The delta connection…. S O U R C E a L O A D b c n Install three 900 kvar 12.47 kV delta-connected Capacitors. FE: Electric Circuits © C.A. Gross EE1- 56 28 Z 3 ZY wye-delta connections wye case 2700 Qan 900 kvar 3 Ia delta case Qan Qan 900 125 A Van 7.2 Zan ZY CY Iab Van 57.6 Ia 2700 900 kvar 3 Qab 900 72.17 A Vab 12.47 Zab Z 1 46.05 F ZY C FE: Electric Circuits 12.47 172.8 72.17 1 15.35 F Z © C.A. Gross EE1- 57 1st Order Transients….. i t Network B Network A contains dc sources, resistors, one switch vt contains one energy storage element (L or C) The problem….(1) solve for v and/or i @ t < 0; (2) switch is switched @ t = 0; (3) solve for v and/or i for t > 0 FE: Electric Circuits © C.A. Gross EE1- 58 29 The inductive case vL L di L dt L's are SHORTS to dc iL(t) cannot change in zero time i L (0 ) i L (0) i L (0 ) FE: Electric Circuits © C.A. Gross EE1- 59 An Example… vL L di L dt FE: Electric Circuits i L (0 ) i L (0) i L (0 ) © C.A. Gross EE1- 60 30 Solution.... constant vC (t ) vC ( ) constant t 0: vC (t ) vC (0) t : 0 t : vC (t ) vC ( ) vC (0) vC ( ) e t / Rab C Our job is to determine vC (0); vC ( ); and Rab C FE: Electric Circuits © C.A. Gross EE1- 61 Solution.... For a capacitor: iC C dvC dt C's are OPENS to dc vC(t) cannot change in zero time Therefore, if the circuit is switched at t = 0: vC (0 ) vC (0) vC (0 ) FE: Electric Circuits © C.A. Gross EE1- 62 31 Solution: T < 0; switch and "C" OPEN + 120V - A vC 0 a 0 + vC b 120 12 48 V 12 6 12 FE: Electric Circuits © C.A. Gross EE1- 63 Solution: T > 0; switch CLOSED + 120V - a + vC - A vC iC b Rab 6 12 4 6 12 0.2 F Rab C 4(0.2) 0.8 s 120 12 80 V 0 6 12 FE: Electric Circuits © C.A. Gross EE1- 64 32 Solution.... vC (0) 48 vC ( ) 80 t 0: vC (t ) 80 48 80 e 1.25 t vC (t ) 80 32 e 1.25 t FE: Electric Circuits © C.A. Gross EE1- 65 3. 1st Order Transients: RL 0.4 H b. The switch is closed at t = 0. Find and plot iL (t). FE: Electric Circuits © C.A. Gross EE1- 66 33 Solution.... t 0: i L (t ) i L (0) i L (t ) i L ( ) i L (0) i L ( ) e t / t 0: L Rab Our job is to determine i L (0); i L ( ); and L / Rab FE: Electric Circuits © C.A. Gross EE1- 67 Solution.... For an inductor: vL L di L dt L's are SHORTS to dc iL(t) cannot change in zero time i L (0 ) i L (0) i L (0 ) FE: Electric Circuits © C.A. Gross EE1- 68 34 Solution: T < 0; switch OPEN; L SHORT + 120V - a + vC - A iL 0 iL b 120 6.667 A 12 6 FE: Electric Circuits © C.A. Gross EE1- 69 Solution: T > 0; switch CLOSED + 120V - a iL + vL - A b 120 iL 20 A 060 FE: Electric Circuits © C.A. Gross Rab 6 12 4 6 12 0.4 H L 0.4 4 Rab 0.1 s EE1- 70 35 Solution.... t 0: i L (t ) 6.667 t 0: i L (t ) 20 6.667 20 e t / i L (t ) 20 13.33 e 10 t FE: Electric Circuits © C.A. Gross EE1- 71 5. Control Given the following feedback control system: R(s) + C(s) G(s) H(s) G ( s) 1 ( s 1)( s 4) FE: Electric Circuits © C.A. Gross H ( s) K EE1- 72 36 a. Write the closed loop transfer function in rational form 1 C G ( s 1)( s 4) K R 1 GH 1 ( s 1)( s 4) C 1 1 2 R ( s 1)( s 4) K s 3s ( K 4) FE: Electric Circuits © C.A. Gross EE1- 73 b. Write the characteristic equation s 2 3s ( K 4) 0 c. What is the system order? 2 d. For K = 0, where are the poles located? s 2 3s 4 s 1 s 4 0 s = +1; s = - 4 e. For K = 0, is the system stable? FE: Electric Circuits © C.A. Gross NO EE1- 74 37 s 2 3s ( K 4) 0 f. Complete the table Roots of the CE are poles of the CLTF K poles 0 4 damping 4 .0 0, 1 .0 0 3 .0 0, 0 .0 0 u n stab le o ver 5 2 .6 2, 0 .3 8 2 o ver 6 .2 5 1 .5 0, 1 .5 0 critical 1 0 .2 5 1 .5 j 2, 1 .5 j 2 u n d er FE: Electric Circuits © C.A. Gross EE1- 75 f. Sketch the root locus j g. Find the range on K for system stability. -4 +1 If K = 4: s 2 3s 0 s s 3 0 Poles at s = 0; s = - 3 Therefore for K>4, poles are in LH s-plane and system is stable. K≥4 FE: Electric Circuits © C.A. Gross EE1- 76 38 h. Find K for critical damping CE : s 2 3s ( K 4) 0 Solving the CE: s 3 9 4( K 4) 2 Critical damping occurs when the poles are real and equal 9 4( K 4) 0 K 4 9 / 4; K 4 2.25 6.25 FE: Electric Circuits © C.A. Gross EE1- 77 6. Signal Processing a. periodic time-domain functions have continuous discrete frequency spectra. (circle the correct adjective) b. aperiodic time-domain functions have continuous discrete frequency spectra. (circle the correct adjective) FE: Electric Circuits © C.A. Gross EE1- 78 39 c. Matching d. Laplace Transform d Fourier Transform Fourier Series a Convolution integral b Inverse FT e N D exp( jn t) a. x(t ) n n N t b. y(t ) x( ) h(t ) d e. x(t ) 1 2 0 FE: Electric Circuits 0 x(t ) e c. X ( j ) d. X ( s ) x(t ) e st dt c j t X ( j ) e dt j t d © C.A. Gross EE1- 79 c. Matching d. Z-Transform d DFT Inverse ZT a Discrete Convolution b Inverse DFT e b. y[ k ] c a. X ( j) x[n] e jn n k x[ n ] h[ n k ] n N 1 c. X k x[ n] e j 2 kn / N n0 d. X ( z ) x[ n] z n n0 FE: Electric Circuits e. x[n] © C.A. Gross 1 N N 1 X k 0 k e j 2 kn / N EE1- 80 40 7. Electronics e (t ) v v e e (t ) 169.7 sin( t ) T a. Darken the conducting diodes at time T FE: Electric Circuits © C.A. Gross EE1- 81 b. Given the "OP Amp" circuit Ideal OpAmp.... •infinite input resistance • zero input voltage •infinite gain • zero output resistance FE: Electric Circuits © C.A. Gross EE1- 82 41 Find the output voltage. vi 5 V Ri 10 k R f 50 k KCL : Rf v0 vi Ri 50 v0 5 25 V 10 FE: Electric Circuits vi v 0 0 Ri R f © C.A. Gross EE1- 83 c. Find the output voltage. 40k 0 + 5 + 5 + 20k 10k KCL : v v1 v2 v3 0 0 R1 R2 R3 R f 10k + + vo LOAD - FE: Electric Circuits © C.A. Gross EE1- 84 42 "SUMMER" Solution: 0 5 5 v 0 0 40 20 10 10 40k 0 + 5 + 5 + 20k 10k 10k 10 10 10 v0 5 5 0 10 20 40 + + vo LOAD v0 7.5 V - FE: Electric Circuits © C.A. Gross EE1- 85 8. Digital Systems Logic Gates FE: Electric Circuits © C.A. Gross EE1- 86 43 a. Complete the Truth Table C A 0 Half Adder (HA) AND S B 0 XOR A B 0 0 1 1 0 1 0 1 C 0 0 0 1 A + B = CS S 0 1 1 0 FE: Electric Circuits 0 + 0 = 00 0 + 1 = 01 1 + 0 = 01 1 + 1 = 10 © C.A. Gross EE1- 87 b. Complete the indicated row in the TT A1 0 0 1 1 0 0 1 1 B1 C2 S1 0 0 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 1 FE: Electric Circuits A 11 C0 A HA S 1 B 01 HA 1C1 OR 1 C2 1 C 0 C1 0 0 0 0 1 1 1 1 S1 Full Adder (FA) © C.A. Gross EE1- 88 44 c. Indicate the inputs and outputs to perform the given sum in a 4-bit adder 1 1 1 0 1 1 1 1 0 0 0 A3 B3 C2 A2 B2 C1 A1 B1 C0 A0 B0 FA FA FA HA C3 S3 S2 S1 S0 1 1 0 0 0 FE: Electric Circuits © C.A. Gross 1010 +1110 11000 EE1- 89 d. Design a D/A Converter to accomodate 3-bit digital inputs (5 volt logic) Resolution: 3-bits (23 = 8 levels; 10 V scale) Example... Convert "110" to analog FE: Electric Circuits Digital Analog (V) 000 0.00 001 1.25 010 2.50 011 3.75 100 5.00 101 6.25 110 7.50 111 8.75 Binary Word: ABC (A msb; C lsb) © C.A. Gross EE1- 90 45 d. Finished Design ABC = 110 40k 0 C+ 5 B+ 5 A+ 20k 10k 10 10 10 5 5 0 10 20 40 7.50 v0 10k + + vo LOAD - FE: Electric Circuits © C.A. Gross EE1- 91 Good Luck on the Exam! If I can help with any ECE material, come see me (7:30 - 11:00; 1:15 - 2:30) Charles A. Gross, Professor Emeritus Electrical and Comp Engineering Auburn University Broun 212 334.844.1812 gross@eng.auburn.edu Good Evening... FE: Electric Circuits © C.A. Gross EE1- 92 46