RHD5900 - Aeroflex Microelectronic Solutions

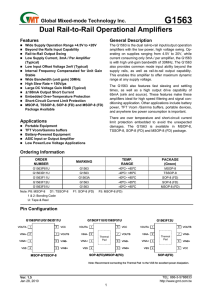

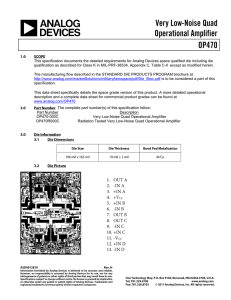

advertisement