Fairchild Reference Design RD-521

advertisement

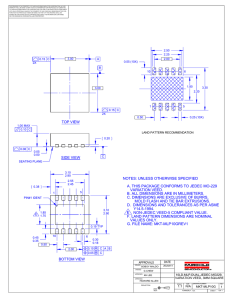

www.fairchildsemi.com Fairchild Reference Design RD-521 The following reference design supports inclusion of FSL336LR in design of an auxiliary power supply. It should be used in conjunction with the FSL336LR datasheet as well as Fairchild’s application notes and technical support team. Please visit Fairchild’s website at www.fairchildsemi.com. Application Fairchild Device Input Voltage Range Rated Output Power Output Voltage (Rated Current) Topology Auxiliary Power FSL336LR 144-374 VAC 14.8 W 16 V (0.8 A) 10 V (0.2 A) SSR Flyback Key Features Built-in Avalanche-Rugged SenseFET: 650 V Fixed Operating Frequency: 50 kHz No-Load Power Consumption: <25 mW at 230 VAC with External Bias <120 mW at 230 VAC without External Bias No Need for Auxiliary Bias Winding Frequency Modulation for Attenuating EMI Pulse-by-Pulse Current Limiting Ultra-Low Operating Current: 250 µA Built-in Soft-Start and Startup Circuit Adjustable Peak Current Limit Built-in Transconductance (Error) Amplifier Various Protections: Overload Protection (OLP), Over-Voltage Protection (OVP), Feedback Open-Loop Protection (FB_OLP), Thermal Shutdown (TSD) Fixed 650 ms Restart Time for Safe Auto-Restart of All Protections © 2014 Fairchild Semiconductor Corporation 1 RD-521_FSL336LR • Rev. 1.0 www.fairchildsemi.com 1. Schematic Figure 1. © 2014 Fairchild Semiconductor Corporation Schematic 2 RD-521_FSL336LR • Rev. 1.0 www.fairchildsemi.com 2. Transformer 2.1. Transformer Schematic Diagram Figure 2. Transformer Structure and Winding Stackup 2.2. Winding Specification Windings Pins (S→F) Wire (AWG) Turns Layers Winding Direction Winding Method Np1 3→2 28 68 2 Forward Solenoid 22 1 Forward Solenoid 14 1 Forward Solenoid 32 1 Forward Solenoid Inter-Layer Insulation: 1 tape layer between winding layers Outer Insulation: 2 tape layers after winding NS1 7→5 24 Outer Insulation: 2 tape layers after winding Ns2 10→9 2x 32 TIW Outer Insulation: 1 tape layers after winding Np2 2→1 28 Inter-Layer Insulation: 1 tape layer between coil and finish breakout lead Outer Insulation: 3 tape layers after winding Note: Start/Finish Leads: insulate with tape or tubing if needed 2.3. Electrical Characteristics Pin Specification Remark Inductance 3→1 1.15 mH +/-5% 50 kHz, 1 Vac Leakage 3→1 < 25 µH Short 5, 7, 9, 10 © 2014 Fairchild Semiconductor Corporation 3 RD-521_FSL336LR • Rev. 1.0 www.fairchildsemi.com 3. Bill of Materials Ref Des R101 R102 R103 R201 R202 R203 R204 C101 C102 C103 C104 C105 Qty 1 1 1 1 1 1 1 1 1 1 1 1 C201 1 C202 1 T101 D101 D201 D202 U101 1 1 1 1 1 Description Manufacturer Manf. P/N Package Resistor, metal oxide, 62K, 1W, 5% 1W Resistor, SMT, 0805, 49.9K, 1% 0805 Resistor, SMT, 0805, 51K, 5% 0806 Resistor, SMT, 0805, 27.4K, 1% 0807 Resistor, SMT, 0805, 5.11K, 1% 0808 Resistor, SMT, 0805, 2K, 5% 0809 Resistor, SMT, 0805, 5.1K, 5% 0810 Capacitor, Al. El., 10uF, 400V, 105C, 20% Chemi-Con KMG series Capacitor, Ceramic disc, 3.3nF, 1KV, 20% Capacitor, MLCC, 100nF, 50V, 10%, X7R, 0805 0805 Capacitor, Al. El., 22uF, 50V, 105C, 20% Nichicon PW series Capacitor, MLCC, 1nF, 50V, 10%, X7R, 0603 0603 Capacitor, Al. El., 120uF, 16V, 105C, 20%, 405mA Chemi-Con KZE series 6.3x11mm Capacitor, Al. El., 470uF, 25V, 105C, 20%, 1430mA Chemi-Con KZE series 10x16mm Transformer, 15W, EF20, PC47, 1.15mH, 10pin hrz. Custom TBH EF-20H Diode, fast rectifier, 1A, 1000V Fairchild RGP10M DO-41 Diode, ultrafast rectifier, 1A, 150V Fairchild EGP10C DO-41 Diode, ultrafast rectifier, 3A, 200V Fairchild EGP10D DO-201AD IC, PWM, intg. FET, intg. Er. Amp., 650V, 50kHz Fairchild FSL336LRN DIP-7 © 2014 Fairchild Semiconductor Corporation 4 RD-521_FSL336LR • Rev. 1.0 www.fairchildsemi.com 4. Performance 4.1. Output Current Regulation In order to maintain constant voltage on the unregulated 10 V output at its maximum load, a minimum load of ~40 mA is required on the regulated 16 V output. Below this total output power, the FSL336 enters burst-mode operation to improve light load efficiency. The 16 V load was swept to 0 A in these tests, as indicated in the curves below. Performance of the 10 V rail in this “opposite extremes” load condition could be improved by increasing the 10 V output capacitance; or possibly by reducing the value of compensation capacitor C105. Figure 3. Output regulation data plotted against load variation (Vin=144 VDC) © 2014 Fairchild Semiconductor Corporation 5 RD-521_FSL336LR • Rev. 1.0 www.fairchildsemi.com Figure 4. Output regulation data plotted against load variation (Vin=374 VDC) Output Regulation Summary: 16V output Spec. Min. = 15.2 V Spec. Max = 16.8 V Measured High = 15.893 V (min load) Measured Low = 15.842 V (max load) 10V output Spec. Min. = 7.5 V Spec. Max = 12.5 V Measured High = 12.106 V (10 V @min load, 16 V @max load, Vin=340 VDC) Measured Low* = 9.139 V (10 V @max load, 16 V @min load, Vin=144 VDC) * Excluding 10 V/200 mA condition when I(16 V) < 40 mA. © 2014 Fairchild Semiconductor Corporation 6 RD-521_FSL336LR • Rev. 1.0 www.fairchildsemi.com 4.2. Efficiency Figure 5. Efficiency data plotted against line variation. Efficiency Summary Load © 2014 Fairchild Semiconductor Corporation Vin (VDC) 50% (~7.4W) Max (~14.8W) 144 86.1% 87.3% 170 86.1% 87.3% 340 84.1% 86.1% 374 83.5% 85.6% 7 RD-521_FSL336LR • Rev. 1.0 www.fairchildsemi.com 5. Related Resources FSL336LR – Product Folder Reference Design Disclaimer Fairchild Semiconductor Corporation (“Fairchild”) provides these reference design services as a benefit to our customers. Fairchild has made a good faith attempt to build for the specifications provided or needed by the customer. Fairchild provides this product “as is” and without “recourse” and MAKES NO WARRANTY, EXPRESSED, IMPLIED OR OTHERWISE, INCLUDING ANY WARRANTY OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Customer agrees to do its own testing of any Fairchild reference designs in order to ensure design meets the customer needs. Neither Fairchild nor Customer shall be liable for incidental or consequential damages, including but not limited to, the cost of labor, requalifications, rework charges, delay, lost profits, or loss of goodwill arising out of the sale, installation or use of any Fairchild product. Subject to the limitations herein, Fairchild will defend any suit or proceeding brought against Customer if it is based on a claim that any product furnished hereunder constitutes an infringement of any intellectual property rights. Fairchild must be notified promptly in writing and given full and complete authority, information and assistance (at Fairchild’s expense) for defense of the suit. Fairchild will pay damages and costs therein awarded against Customer but shall not be responsible for any compromise made without its consent. In no event shall Fairchild’s liability for all damages and costs (including the costs of the defense by Fairchild) exceed the contractual value of the products or services that are the subject of the lawsuit. In providing such defense, or in the event that such product is held to constitute infringement and the use of the product is enjoined, Fairchild, in its discretion, shall procure the right to continue using such product, or modify it so that it becomes noninfringing, or remove it and grant Customer a credit for the depreciated value thereof. Fairchild’s indemnity does not extend to claims of infringement arising from Fairchild’s compliance with Customer’s design, specifications and/or instructions, or the use of any product in combination with other products or in connection with a manufacturing or other process. The foregoing remedy is exclusive and constitutes Fairchild’s sole obligation for any claim of intellectual property infringement and Fairchild makes no warranty that products sold hereunder will not infringe any intellectual property rights. All solutions, designs, schematics, drawings, boards or other information provided by Fairchild to Customer are confidential and provided for Customer’s own use. Customer may not share any Fairchild materials with other semiconductor suppliers. © 2014 Fairchild Semiconductor Corporation 8 RD-521_FSL336LR • Rev. 1.0