LTC6601-2 - Linear Technology

advertisement

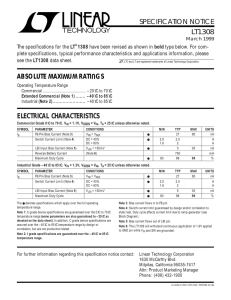

LTC6601-2 Low Power, Low Distortion, 5MHz to 27MHz, Pin Configurable Filter/ADC Driver DESCRIPTION FEATURES n n n n n n n n n n Pin Configurable Gain and Filter Response Up to 27MHz Low Power: 16mA at 3V Low Distortion (2VP-P) 1MHz: –96dBc 2nd, –112dBc 3rd 10MHz: –65dBc 2nd, –78dBc 3rd Few External Components Required Resistors Trimmed to 0.5% Accuracy Typical Capacitors Trimmed to 0.5% Accuracy Typical Adjustable Output Common Mode Voltage Rail-to-Rail Output Swing Power Configurability and Low Power Shutdown Tiny 0.75mm 20-Lead (4mm × 4mm) QFN Package APPLICATIONS n n n n n n Differential A/D Converter Driver Antialiasing/Reconstruction Filter Single-Ended to Differential Conversion/Amplification Low Voltage, Low Noise, Differential Signal Processing Common Mode Voltage Translation Portable Instrumentation The LTC®6601-2 is a low power, low distortion, very easy-to-use fully differential 2nd order active broadband RC filter and driver. On-chip resistors, capacitors, and amplifier bandwidth are trimmed to provide consistent and repeatable filter characteristics. The filter characteristics are pin-strap configurable. Cutoff frequencies range from 5MHz to 27MHz. Gain is pin-strap programmable between –17dB and +17dB. A three-state BIAS pin is provided to adjust amplifier power consumption. Select between low power (50% power reduction), high performance and standby modes with the BIAS pin. The LTC6601 family comes in two options which trade off distortion and noise. The LTC6601-2 offers the lowest distortion at high frequencies. The LTC6601-1 is configured for lowest noise. Both are available in pin-compatible packages. The LTC6601-2 is available in a compact 4mm × 4mm 20-pin leadless QFN package. L, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6271719. TYPICAL APPLICATION –50 –40 –60 –50 –70 –80 –90 –100 LTC6601-1 HD2 LTC6601-2 HD2 LTC6601-1 HD3 LTC6601-2 HD3 –110 –120 DISTORTION COMPONENT (dBc) DISTORTION COMPONENT (dBc) Distortion Comparison Between LTC6601-1 and LTC6602-2 15MHz Filter, Single-Ended Input, Low Power Mode 25MHz Filter, Single-Ended Input, Low Power Mode –60 –70 –80 –90 –100 –110 –120 1 10 FREQUENCY (MHz) 100 66012 TA01a LTC6601-1 HD2 LTC6601-2 HD2 LTC6601-1 HD3 LTC6601-2 HD3 1 10 FREQUENCY (MHz) 100 66012 TA01b 66012f 1 LTC6601-2 ABSOLUTE MAXIMUM RATINGS PIN CONFIGURATION (Note 1) Total Supply Voltage (V + to V – ) ...............................5.5V Input Voltage (Any Pin) (Note 2) ..V + + 0.3V to V – –0.3V Input Current (VOCM, BIAS)..................................±10mA Input Current (Pins 1, 5) (Note 2) ........................±20mA Input Current (Pins 2, 4) (Note 2) ........................±30mA Input Current (Pins 6, 20) (Note 2) ......................±15mA Input Current (Pins 7, 8, 9, 10, 16, 17, 18, 19) (Note 2)................................................................±10mA Output Short-Circuit Duration (Note 3) ............ Indefinite Operating Temperature Range (Note 4)....–40°C to 85°C Specified Temperature Range (Note 5) ....–40°C to 85°C Junction Temperature ........................................... 150°C Storage Temperature Range...................–65°C to 150°C C8 C7 C6 C5 IN4+ TOP VIEW 20 19 18 17 16 IN2+ 1 15 OUT– IN1+ 14 V+ 2 BIAS 3 – 13 V– 21 7 8 9 10 C3 C4 6 C2 11 OUT+ C1 12 VOCM IN4– 4 IN2– 5 IN1 UF PACKAGE 20-LEAD (4mm s 4mm) PLASTIC QFN TJMAX = 150°C, θJA = 37°C/W, θJC = 4.3°C/W EXPOSED PAD (PIN 21) IS V–, MUST BE SOLDERED TO PCB ORDER INFORMATION LEAD FREE FINISH TAPE AND REEL PART MARKING* PACKAGE DESCRIPTION TEMPERATURE RANGE LTC6601CUF-2#PBF LTC6601IUF-2#PBF LTC6601CUF-2#TRPBF LTC6601IUF-2#TRPBF 66012 66012 20-Lead (4mm × 4mm) Plastic QFN 20-Lead (4mm × 4mm) Plastic QFN 0°C to 70°C –40°C to 85°C Consult LTC Marketing for parts specified with wider operating temperature ranges. *The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/ DC ELECTRICAL CHARACTERISTICS + The l denotes the specifications which apply over the full operating – + temperature range, otherwise specifications are at TA = 25°C. V = 3V, V = 0V, VINCM = VOCM = mid-supply, BIAS tied to V or floating, ILOAD = 0, RBAL = 100k. The filter is configured for a gain of 1 unless otherwise noted. VS is defined as (V+ – V–). VOUTCM is defined as (VOUT+ + VOUT–)/2. VINCM is defined as (VINP + VINM)/2. VOUTDIFF is defined as (VOUT+ – VOUT–). VINDIFF is defined as (VINP – VINM). See Figure 1. SYMBOL PARAMETER CONDITIONS VOSDIFF (Note 6) Amplifier Differential Offset Voltage (Input Referred) VS = 2.7V to 5.25V, BIAS = Floating BIAS = V+ ΔVOSDIFF/ΔT (Note 6) Ampifier Differential Offset Voltage Drift (Input Referred) VS = 2.7V to 5.25V RIN (Note 14) Input Resistance, BIAS = V+ Single Ended Input Resistance, Pin 2 or Pin 4 VS = 3V Differential Input Resistance VS = 3V MIN l l TYP MAX UNITS ±0.25 ±0.25 ±2 ±1.25 mV mV 1 133 200 μV/°C Ω Ω 66012f 2 LTC6601-2 DC ELECTRICAL CHARACTERISTICS + The l denotes the specifications which apply over the full operating – + temperature range, otherwise specifications are at TA = 25°C. V = 3V, V = 0V, VINCM = VOCM = mid-supply, BIAS tied to V or floating, ILOAD = 0, RBAL = 100k. The filter is configured for a gain of 1 unless otherwise noted. VS is defined as (V+ – V–). VOUTCM is defined as (VOUT+ + VOUT–)/2. VINCM is defined as (VINP + VINM)/2. VOUTDIFF is defined as (VOUT+ – VOUT–). VINDIFF is defined as (VINP – VINM). See Figure 1. SYMBOL PARAMETER ΔRIN (Note 14) Input Resistance Match, BIAS = V+ Single Ended Input Resistance, Pin 2 or Pin 4 VS = 3V CONDITIONS MIN l TYP MAX ±0.25 UNITS Ω IB (Note 7) Internal Amplifier Input Bias VS = 2.7V to 5V BIAS = Floating BIAS = V+ l l IOS (Note 7) Internal Amplifier Input Offset VS = 2.7V to 5V BIAS = Floating BIAS = V+ l l VINCM (Note 8) Input Signal Common Mode Range (VINP + VINM)/2 BIAS = V+, VOCM = 2.5V BIAS = V+, VOCM = 1.5V VS = 5V VS = 3V l l BIAS Pin Floating, VOCM = 2.5V BIAS Pin Floating, VOCM = 1.5V VS = 5V VS = 3V l l Input Common Mode Rejection Ratio (Amplifier Input Referred) ΔVINCM/ΔVOSDIFF ΔVINCM = 2.5V VS = 5V 74 dB CMRRO (Notes 9, 14) Output Common Mode Rejection Ratio (Amplifier Input Referred) ΔVOCM/ΔVOSDIFF ΔVOCM = 1V VS = 5V 70 dB PSRR (Note 10) Power Supply Rejection Ratio (Amplifier Input Referred) ΔVS /ΔVOSDIFF BIAS Pin Floating BIAS = V+ VS = 2.7V to 5V VS = 2.7V to 5V l l 58 58 94 81 dB dB PSRRCM (Note 10) Common Mode Power Supply Rejection Ratio (ΔVS /ΔVOSCM) VS = 2.7V to 5V l 40 51 dB 1 V/V CMRRI (Notes 9, 14) gcm –25 –50 –12.5 –25 0 0 μA μA ±1 ±1 ±5 ±10 μA μA 0 0 4.7 1.7 V V 0 0 4.8 1.8 V V Common Mode Gain (ΔVOUTCM/ΔVOCM) ΔVOCM = 2V VS = 5V Common Mode Gain Error = 100 • (gcm – 1) ΔVOCM = 2V VS = 5V l ±0.3 ±1.0 % Output Balance (ΔVOUTCM/ΔVOUTDIFF) Single-Ended Input Differential Input ΔVOUTDIFF = 2V VS = 5V VS = 5V l l –58 –62 –40 –40 dB dB VOSCM Common Mode Offset Voltage (VOUTCM – VOCM) VS = 2.7V to 5V VS = 2.7V to 5V BIAS = Floating BIAS = V+ l l ±15 ±15 ±30 ±30 mV mV ΔVOSCM/ΔT Common Mode Offset Voltage Drift (VOUTCM – VOCM) VS = 2.7V to 5V VS = 2.7V to 5V BIAS = Floating BIAS = V+ l l 20 20 VOUTCMR (Note 8) Output Signal Common Mode Range (Voltage Range for the VOCM Pin) VS = 3V VS = 5V VS = 3V VS = 5V BIAS Pin Floating BIAS Pin Floating BIAS = V+ BIAS = V+ l l l l 1.1 1.1 1.1 1.1 BAL μV/°C μV/°C 1.8 4 1.7 4 RINVOCM Input Resistance, VOCM Pin VS = 3V l 5 7 9 VMID Voltage at the VOCM PIn VS = 3V l 1.475 1.5 1.525 V V V V kΩ V 66012f 3 LTC6601-2 DC ELECTRICAL CHARACTERISTICS + The l denotes the specifications which apply over the full operating – + temperature range, otherwise specifications are at TA = 25°C. V = 3V, V = 0V, VINCM = VOCM = mid-supply, BIAS tied to V or floating, ILOAD = 0, RBAL = 100k. The filter is configured for a gain of 1 unless otherwise noted. VS is defined as (V+ – V–). VOUTCM is defined as (VOUT+ + VOUT–)/2. VINCM is defined as (VINP + VINM)/2. VOUTDIFF is defined as (VOUT+ – VOUT–). VINDIFF is defined as (VINP – VINM). See Figure 1. SYMBOL PARAMETER CONDITIONS VOUT Output Voltage, High, Either Output Pin (Note 11) VS = 3V, IL = 0mA, BIAS Pin Floating VS = 3V, IL = –5mA, BIAS Pin Floating VS = 3V, IL = –20mA, BIAS Pin Floating VS = 5V, IL = 0mA, BIAS Pin Floating VS = 5V, IL = –5mA, BIAS Pin Floating VS = 5V, IL = –20mA, BIAS Pin Floating VS = 3V, IL = 0mA VS = 3V, IL = –5mA VS = 3V, IL = –20mA VS = 5V, IL = 0mA VS = 5V, IL = –5mA VS = 5V, IL = –20mA Output Voltage, Low, Either Output Pin (Note 11) MIN BIAS = V+ BIAS = V+ BIAS = V+ BIAS = V+ BIAS = V+ BIAS = V+ VS = 3V, IL = 0mA, BIAS Pin Floating VS = 3V, IL = 5mA, BIAS Pin Floating VS = 3V, IL = 20mA, BIAS Pin Floating VS = 5V, IL = 0mA, BIAS Pin Floating VS = 5V, IL = 5mA, BIAS Pin Floating VS = 5V, IL = 20mA, BIAS Pin Floating VS = 3V, IL = 0mA VS = 3V, IL = 5mA VS = 3V, IL = 20mA VS = 5V, IL = 0mA VS = 5V, IL = 5mA VS = 5V, IL = 20mA BIAS = V+ BIAS = V+ BIAS = V+ BIAS = V+ BIAS = V+ BIAS = V+ TYP MAX UNITS l l l l l l 240 290 470 370 430 650 450 525 850 675 775 1100 mV mV mV mV mV mV l l l l l l 245 285 415 350 390 550 450 525 750 625 700 1000 mV mV mV mV mV mV l l l l l l 110 120 170 150 170 225 200 225 300 270 300 400 mV mV mV mV mV mV l l l l l l 120 135 195 175 200 270 225 250 350 325 360 475 mV mV mV mV mV mV l l ±45 ±60 l 2.7 ISC Output Short-Circuit Current, Either Output Pin (Note 12) VS Supply Voltage Range IS Supply Current, BIAS Pin Floating VS = 2.7V VS = 3V VS = 5V l l l Supply Current, BIAS Pin Tied to V+ VS = 2.7V VS = 3V VS = 5V ISHDN Supply Current, BIAS Pin Tied to V– VBIASSD BIAS Input Pin Range for Shutdown VBIASLP (Note 13) BIAS Input for Low Power Operation VS = 3V VS = 5V ±65 ±90 mA mA 5.25 V 15.8 16 16.7 23 23.5 24.5 mA mA mA l l l 32 32.2 33 41 41.5 43 mA mA mA VS = 2.7V VS = 3V VS = 5V l l l 0.4 0.45 0.65 1 1.1 1.8 mA mA mA VS = 2.7V to 5V l V– V– + 0.4 V l V– + 1.0 V– + 1.5 V V– + 2.3 V+ V kΩ VS = 2.7V to 5V VBIASHP BIAS Input for High Performance Operation VS = 2.7V to 5V l RBIAS BIAS Input Resistance VS = 2.7V to 5V l 100 150 200 l V– + 1.05 V– + V– + 1.25 VBIAS BIAS Float Voltage VS = 2.7V to 5V V 1.15 tON Turn-On Time VS = 3V, VSHDN = 0.25V to 3V 400 ns tOFF Turn-Off Time VS = 3V, VSHDN = 3V to 0.25V 400 ns 66012f 4 LTC6601-2 AC ELECTRICAL CHARACTERISTICS + The l denotes the specifications which apply over the full operating – + temperature range, otherwise specifications are at TA = 25°C. V = 3V, V = 0V, VINCM = VOCM = mid-supply, VBIAS is tied to V or floating, unless otherwise noted. (See Figure 2 for the AC test configuration.) VS is defined as (V+ – V–). VOUTCM is defined as (VOUT+ + VOUT–)/2. VICM is defined as (VINP + VINM)/2. VOUTDIFF is defined as (VOUT+ – VOUT–). VINDIFF is defined as (VINP – VINM). SYMBOL PARAMETER CONDITIONS GAIN Filter Gain, See Figure 2, BIAS Pin Floating (Remaining AC Measurements Relative to 1MHz) ΔVIN = ±0.25V, fTEST = DC (Note 14) VIN = 600mVP-P, fTEST = 1MHz VIN = 600mVP-P, fTEST = 2MHz VIN = 600mVP-P, fTEST = 5MHz VIN = 600mVP-P, fTEST = 10MHz VIN = 600mVP-P, fTEST = 14.45MHz VIN = 600mVP-P, fTEST = 20MHz VIN = 600mVP-P, fTEST = 50MHz l l l l l l l l Filter Phase, See Figure 2, BIAS Pin Floating ΔVIN = ±0.25V, fTEST = DC VIN = 600mVP-P, fTEST = 1MHz VIN = 600mVP-P, fTEST = 2MHz VIN = 600mVP-P, fTEST = 5MHz VIN = 600mVP-P, fTEST = 10MHz VIN = 600mVP-P, fTEST = 14.45MHz VIN = 600mVP-P, fTEST = 20MHz VIN = 600mVP-P, fTEST = 50MHz l l l l l l l l NOISE Output Noise, See Figure 2, BIAS Pin Floating BW = 100MHz BW = 20MHz 154 135 μVRMS μVRMS SNR BIAS Pin Floating BW = 100MHz BW = 20MHz 73 74 dB dB Distortion VIN = 2VP-P , 10MHz, BIAS Pin Floating HD2, Single-Ended Input HD3, Single-Ended Input HD2, Differential Input HD3, Differential Input –60 –79 –65 –77 dBc dBc dBc dBc fO TC Cutoff Frequency Temperature Coefficient –120 ppm/°C GAIN Filter Gain, See Figure 2, BIAS Pin Tied to V+, AC Gain Measurements Relative to 1MHz ΔVIN = ±0.25V, fTEST = DC (Note 14) VIN = 600mVP-P, fTEST = 1MHz VIN = 600mVP-P, fTEST = 2MHz VIN = 600mVP-P, fTEST = 5MHz VIN = 600mVP-P, fTEST = 10MHz VIN = 600mVP-P, fTEST = 14.45MHz VIN = 600mVP-P, fTEST = 20MHz VIN = 600mVP-P, fTEST = 50MHz l l l l l l l l Filter Phase, See Figure 2, BIAS Pin Tied to V+ ΔVIN = ±0.25V, fTEST = DC VIN = 600mVP-P, fTEST = 1MHz VIN = 600mVP-P, fTEST = 2MHz VIN = 600mVP-P, fTEST = 5MHz VIN = 600mVP-P, fTEST = 10MHz VIN = 600mVP-P, fTEST = 14.45MHz VIN = 600mVP-P, fTEST = 20MHz VIN = 600mVP-P, fTEST = 50MHz l l l l l l l l NOISE Wide Band Output Noise, 14.45MHz Cutoff, BIAS Pin Tied to V+ BW = 100MHz BW = 20MHz 108 97 μVRMS μVRMS SNR BIAS Pin Tied to V+ BW = 100MHz BW = 20MHz 76 77 dB dB –67.5 –90 –70 –90 dBc dBc dBc dBc –120 ppm/°C PHASE PHASE DISTORTION VIN = 2VP-P , 10MHz, BIAS Pin Tied to V+ fO TC Cutoff Frequency Temperature Coefficient HD2, Single-Ended Input HD3, Single-Ended Input HD2, Differential Input HD3, Differential Input MIN TYP MAX UNITS –0.25 ±0.05 0 0.02 0.11 –0.34 –2.50 –6.55 –21.55 0.25 dB dB dB dB dB dB dB dB –0.08 –0.01 –0.54 –3.00 –7.55 –23.55 –6.0 –12.5 –31.8 –70.1 –103.5 –130.7 –0.25 –0.08 –0.01 –0.54 –2.75 –7.14 –23.70 –6.0 –12.2 –31.2 –68.8 –101.5 –128.4 0 –5.5 –11.3 –29.3 –65.2 –97.5 –125.1 –173.6 ±0.05 0 0.02 0.11 –0.34 –2.35 –6.24 –21.70 0 –5.4 –11 –28.7 –63.8 –95.5 –123.4 –169.3 0.12 0.23 –0.14 –2.00 –5.55 –19.55 –4.8 –10.1 –26.8 –60.1 –91.5 –120.7 0.25 0.12 0.23 –0.14 –1.95 –5.34 –19.70 –4.8 –9.8 –26.2 –58.8 –89.5 –118.4 Deg Deg Deg Deg Deg Deg Deg Deg dB dB dB dB dB dB dB dB Deg Deg Deg Deg Deg Deg Deg Deg 66012f 5 LTC6601-2 ELECTRICAL CHARACTERISTICS Note 1: Stresses beyond those listed under the Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. Note 2: All pins are protected by steering diodes to either supply. If any pin is driven beyond the part’s supply voltage, the excess input current (current in excess of what it takes to drive that pin to the supply rail) should be limited to less than 10mA. Note 3: A heat sink may be required to keep the junction temperature below the Absolute Maximum Rating when the output is shorted indefinitely. Long-term application of output currents in excess of the Absolute Maximum Ratings may impair the life of the device. Note 4: The LTC6601C/LTC6601I are guaranteed functional over the operating temperature range –40°C to 85°C. Note 5: The LTC6601C is guaranteed to meet specified performance from 0°C to 70°C. The LTC6601C is designed, characterized, and expected to meet specified performance from –40°C to 85°C but is not tested or QA sampled at these temperatures. The LTC6601I is guaranteed to meet specified performance from –40°C to 85°C. Note 6: Output referred voltage offset is a function of the low frequency gain of the LTC6601. To determine output referred voltage offset, or output voltage offset drift, multiply this specification by the noise gain (1 + GAIN). See Applications Information for more details. Note 7: Input bias current is defined as the average of the currents flowing into the noninverting and inverting inputs of the internal amplifier and is calculated from measurements made at the pins of the IC. Input offset current is defined as the difference of the currents flowing into the noninverting and inverting inputs of the internal amplifier and is calculated from measurements made at the pins of the IC. Note 8: Input common mode range is tested using the test circuit of Figure 1 by measuring the differential DC gain with VICM = mid-supply, and with VICM at the input common mode range limits listed in the Electrical Characteristics table, verifying the differential gain has not deviated from the mid-supply common mode input case by more than 1%, and the common mode offset (VOCMOS) has not deviated from the mid-supply common mode offset by more than ±20mV. The voltage range for the output common mode range is tested using the test circuit of Figure 1 by measuring the differential DC gain with VOCM = mid-supply, and again with a voltage set on the VOCM pin at the Electrical Characteristics table limits, checking the differential gain has not deviated from the mid-supply common mode input case by more than 1%, and that the common mode offset (VOCMOS) has not deviated by more than ±20mV from the mid-supply case. Note 9: Input CMRR is defined as the ratio of the change in the input common mode voltage at the amplifier input to the change in differential input referred voltage offset. Output CMRR is defined as the ratio of the change in the voltage at the VOCM pin to the change in differential input referred voltage offset. Note 10: Power supply rejection (PSRR) is defined as the ratio of the change in supply voltage to the change in differential input referred voltage offset. Common mode power supply rejection (PSRRCM) is defined as the ratio of the change in supply voltage to the change in the common mode offset, VOUTCM /VOCM. Note 11: Output swings are measured as differences between the output and the respective power supply rail. Note 12: Extended operation with the output shorted may cause junction temperatures to exceed the 150°C limit and is not recommended. Note 13: Floating the BIAS pin will reliably place the part into the halfpower mode. The pin does not have to be driven. Care should be taken, however, to prevent external leakage currents in or out of this pin from pulling the pin into an undesired state. Note 14: The variable contact resistance of the high speed test equipment limits the accuracy of this test. These parameters only show a typical value, or conservative minimum and maximum value. 66012f 6 LTC6601-2 TYPICAL PERFORMANCE CHARACTERISTICS High Performance Supply Current vs Temperature and Supply Voltage Low Power Supply Current vs Temperature and Supply Voltage 18.0 Shutdown Supply Current vs Temperature and Supply Voltage 0.8 35 VINCM = VOCM = MID-SUPPLY BIAS PIN FLOATING VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V+ 17.5 34 0.6 16.5 3V 2.7V 16.0 5V 32 3V 2.7V 0.2 2.7V 31 0.4 0.3 3V 15.5 5V 0.5 33 ICC (mA) ICC (mA) ICC (mA) 17.0 5V VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V – 0.7 0.1 15.0 –50 –25 25 75 0 50 TEMPERATURE (°C) 100 30 –50 125 –25 25 75 0 50 TEMPERATURE (°C) 66012 G01 0 –50 125 100 –25 25 75 0 50 TEMPERATURE (°C) 66012 G03 66012 G02 Shutdown Supply Current vs Supply Voltage and Temperature Supply Current vs Bias Pin Voltage and Temperature 50 125 100 Low Power Mode Supply Current vs Supply Voltage and Temperature 1 100 VINCM = VOCM = MID-SUPPLY VS = 3V 125°C 125°C 40 10 –40°C 25°C 30 20 ICC (mA) ICC (mA) ICC (mA) 0.1 1 –40°C 0.1 0.01 10 –40°C 25°C 125°C 0 0.01 VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V– 0.001 1 2 3 0.5 1.5 2.5 BIAS PIN VOLTAGE WITH RESPECT TO V– (V) 0 1 2 4 3 SUPPLY VOLTAGE (V) 66012 G04 125°C VOS INPUT REFERRED (mV) –40°C 1 0.1 25°C 0.01 VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V+ 0 1 3 2 4 SUPPLY VOLTAGE (V) 5 66012 G07 1 2 4 3 SUPPLY VOLTAGE (V) 1.00 VS = 3V 0.75 VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V+ 0.50 5 REPRESENTATIVE UNITS 0.25 0.00 –0.25 –0.50 –0.75 –1.00 –50 5 Low Power Mode Differential VOS vs Temperature 1.00 10 0 66012 G06 High Performance Mode Differential VOS vs Temperature 100 ICC (mA) 0.001 5 66012 G05 High Performance Supply Current vs Supply Voltage and Temperature 0.001 VINCM = VOCM = MID-SUPPLY BIAS PIN FLOATING VOS INPUT REFERRED (mV) 0 25°C VS = 3V 0.75 VINCM = VOCM = MID-SUPPLY BIAS PIN FLOATING 0.50 5 REPRESENTATIVE UNITS 0.25 0.00 –0.25 –0.50 –0.75 –25 0 50 75 25 TEMPERATURE (°C) 100 125 66012 G08 –1.00 –50 –25 0 50 75 25 TEMPERATURE (°C) 100 125 66012 G09 66012f 7 LTC6601-2 TYPICAL PERFORMANCE CHARACTERISTICS High Performance Common Mode VOS vs Temperature Low Power Common Mode VOS vs Temperature 10 Internal Amplifier Input Bias Current vs Temperature –5 15 10 LOW POWER MODE (BIAS PIN FLOATING) –10 0 IBIAS (μA) 5 VOSCM (mV) VOSCM (mV) 5 0 –15 HIGH PERFORMANCE MODE (BIAS PIN TIED TO V+) –20 –5 –5 V = 3V S VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V+ 5 REPRESENTATIVE UNITS –10 –50 –25 0 50 75 25 TEMPERATURE (°C) 100 VS = 3V –10 VINCM = VOCM = MID-SUPPLY BIAS PIN FLOATING 5 REPRESENTATIVE UNITS –15 –50 –25 0 50 75 25 TEMPERATURE (°C) 125 –25 VS = 3V VINCM = VOCM = MID-SUPPLY 100 66012 G10 FLOAT VOLTAGE (V) RESISTANCE (Ω) RESISTANCE/RNOMINAL (Ω/Ω) 1.15 175 1.10 1.05 125 –25 0 50 75 25 TEMPERATURE (°C) 100 1.00 –50 125 –25 0 50 75 25 TEMPERATURE (°C) 100 125 VS = 3V VINCM = VOCM = MID-SUPPLY RNOMINAL = 200Ω DIFFERENTIAL 1.0025 RNOMINAL = 133.3Ω SINGLE-ENDED SEE FIGURE 1 FOR CONFIGURATION 1.0000 0.9975 0.9950 –50 SINGLE-ENDED DIFFERENTIAL –25 0 50 75 25 TEMPERATURE (°C) 66012 G14 66012 G13 VS = 3V VINCM = VOCM = MID-SUPPLY 5 REPRESENTATIVE UNITS 100 125 66012 G15 High Performance Mode Frequency Response of 12 Possible Filter Configurations Low Frequency Gain vs Temperature 125 1.0050 VS = 3V VINCM = VOCM = MID-SUPPLY VS = 3V VINCM = VOCM = MID-SUPPLY 100 Filter Input Resistance vs Temperature 1.20 200 100 –50 0 50 75 25 TEMPERATURE (°C) 66012 G12 BIAS Pin Float Voltage vs Temperature 150 –25 66012 G11 BIAS Pin Input Resistance vs Temperature 1.010 –30 –50 125 Low Power Mode Frequency Response of 12 Possible Filter Configurations 10 10 0 0 1.000 0.995 0.990 –50 GAIN (dB) GAIN (dB) GAIN (V/V) 1.005 –10 –20 –20 VS = 3V VINCM = VOCM = MID-SUPPLY BIAS PIN FLOATING VS = 3V VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V+ –25 0 50 75 25 TEMPERATURE (°C) 100 125 66012 G16 –10 –30 0.1 1 10 FREQUENCY (MHz) 100 66012 G17 –30 0.1 1 10 FREQUENCY (MHz) 100 66012 G18 66012f 8 LTC6601-2 TYPICAL PERFORMANCE CHARACTERISTICS High Performance Mode Gain and Phase Repeatability of 10 Random Units Low Power Mode Gain and Phase Repeatability of 10 Random Units 4 3 1 –0.10 0 MIN – AVERAGE –1 JMIN – JAVERAGE –2 –0.15 –0.20 0.1 GAIN DEVIATION (dB) 2 0 –0.05 0.20 2 1 –0.05 0 MIN – AVERAGE –1 –2 JMIN – JAVERAGE –0.15 –4 100 1 10 FREQUENCY (MHz) 3 0 –0.10 –3 4 VS = 3V 0.15 VINCM = VOCM = MID-SUPPLY BIAS PIN FLOATING SEE FIGURE 1 0.10 JMAX – JAVERAGE 0.05 MAX – AVERAGE –3 –0.20 0.1 –4 100 1 10 FREQUENCY (MHz) 66012 G19 0 –1 8 VS = 3V VICM = VOCM = MID-SUPPLY 2 BIAS PIN FLOATING 10 RANDOM UNITS PLOTTED TA = 25°C 1 +SPECIFICATION VICM = VOCM = MID-SUPPLY 6 VS = 3V TA = 25°C PHASE ERROR (DEG) GAIN ERROR (dB) VS = 3V VICM = VOCM = MID-SUPPLY 2 BIAS PIN TIED TO V+ 10 RANDOM UNITS PLOTTED TA = 25°C 1 +SPECIFICATION 0 –1 –SPECIFICATION –SPECIFICATION –3 10 FREQUENCY (MHz) 100 1 10 FREQUENCY (MHz) 5 VICM = VOCM = MID-SUPPLY 6 VS = 3V TA = 25°C Pulse Response 1.6 VS = 5V 4 BIAS PIN 1.2 2 +SPECIFICATION VOUTDIFF (V) 0 –2 1 1.0 0 0.8 –1 0.6 –2 –SPECIFICATION 0.4 –3 –5 66012 G24 0 1 VS = 3V 1 0 –1 0.2 VOUTDIFF –4 100 2 1.4 3 2 100 66012 G23 VBIAS PIN (V) PHASE ERROR (DEG) –SPECIFICATION Turn On and Turn Off Transient Response 8 –6 BIAS PIN FLOATING 10 RANDOM UNITS PLOTTED –8 1 10 FREQUENCY (MHz) –2 66012 G22 Low Power Mode Phase Error of 10 Random Units –4 0 –6 BIAS PIN TIED TO V+ 10 RANDOM UNITS PLOTTED –8 1 10 FREQUENCY (MHz) 100 66012 G21 4 +SPECIFICATION 2 VOUTDIFF (V) 1 4 –4 –2 –2 –3 High Performance Mode Phase Error of 10 Random Units 3 3 GAIN ERROR (dB) 66012 G20 Low Power Mode Gain Error of 10 Random Units Normalized to 1MHz High Performance Mode Gain Error of 10 Random Units Normalized to 1MHz PHASE DEVIATION (DEG) VS = 3V 0.15 VINCM = VOCM = MID-SUPPLY BIAS PIN TIED TO V+ SEE FIGURE 1 0.10 JMAX – JAVERAGE 0.05 MAX – AVERAGE PHASE DEVIATION (DEG) GAIN DEVIATION (dB) 0.20 2 3 4 TIME (μs) 5 6 66012 G25 0 –2 0 1 2 3 4 5 TIME (μs) 6 7 8 66012 G26 66012f 9 LTC6601-2 TYPICAL PERFORMANCE CHARACTERISTICS Distortion vs Frequency INTEGRATED NOISE, 1 BIAS TIED TO V+ 10 1 100 10 HD2 –90 HD3 –100 –110 SINGLE ENDED INPUT DIFFERENTIAL INPUT 1 10 100 FREQUENCY (MHz) 0 CHANGE OF fO (%) GAIN (dB) 125 GAIN –30 –1.0 –45 –1.5 –60 –2.0 VS = 3V VICM = VOCM = MID-SUPPLY –2.5 BIAS PIN TIED TO V+ TEMPERATURES PLOTTED: –45°C, –10°C, 25°C, 70°C, 95°C, 125°C –3.0 1 10 FREQUENCY (MHz) –75 Phase Error vs Temperature 10 FREQUENCY (MHz) 800 –SPECIFICATION –3 –105 AVERAGE = 125Ω 900 STD. DEV = 0.22Ω 800 700 FREQUENCY 500 400 600 500 400 300 200 200 100 100 0 100 Normalized 125Ω Resistor Trim AVERAGE = 100Ω STD. DEV = 0.19Ω 300 66012 G33 10 FREQUENCY (MHz) 1000 600 100 1 66012 G32 700 FREQUENCY PHASE ERROR (dB) –1 Normalized 100Ω Resistor Trim 900 –SPECIFICATION 1 0 –2 –90 –10 –15 VS = 3V VICM = VOCM = MID-SUPPLY 2 BIAS PIN TIED TO V+ TEMPERATURES PLOTTED: –45°C, –10°C, 25°C, 1 70°C, 95°C, 125°C +SPECIFICATION 66012 G31 15 –5 –15 PHASE 66012 G30 0 100 3 PHASE (DEG) –1.5 VS = 3V VICM = VOCM = MID-SUPPLY 10 BIAS PIN TIED TO V+ TEMPERATURES PLOTTED: –45°C, –10°C, 25°C, 5 70°C, 95°C, 125°C +SPECIFICATION 1 10 FREQUENCY (MHz) Gain Error Relative to 1MHz vs Temperature –0.5 –1.0 SINGLE ENDED INPUT DIFFERENTIAL INPUT 66012 G29 0 0 100 –120 0.1 Passband Gain and Phase vs Temperature 0.5 0 50 75 25 TEMPERATURE (°C) HD3 –90 66012 G28 0.5 –25 –80 –110 –130 0.1 % Change of fO vs Temperature –0.5 HD2 –100 66012 G27 –2.0 –50 VS = 5V V = 2VP-P INPUT –60 VIN = V ICM OCM = MID-SUPPLY –70 BIAS PIN FLOATING GAIN ERROR (dB) 0.1 1 FREQUENCY (MHz) –50 –120 INTEGRATED NOISE, BIAS PIN FLOATING 0.01 HARMONIC (dBc) 100 SPECTRAL DENSITY, BIAS PIN FLOATING 0.1 0.001 VS = 5V VIN = 2VP-P INPUT –70 VICM = VOCM = MID-SUPPLY BIAS PIN TIED TO V+ –80 SPECTRAL DENSITY, BIAS TIED TO V+ 10 Distortion vs Frequency –60 INTEGRATED NOISE (μVRMS) NOISE SPECTRAL DENSITY (nV/√Hz) VS = 3V 1000 HARMONIC (dBc) Differential Output Noise 100 0.993 0.997 1.001 1.005 NORMALIZED RESISTANCE 1.009 66012 G34 0 0.99 0.994 0.998 1.002 1.006 NORMALIZED RESISTANCE 1.01 66012 G35 66012f 10 LTC6601-2 TYPICAL PERFORMANCE CHARACTERISTICS 1000 900 1000 800 700 800 AVERAGE = 200Ω 900 STD. DEV = 0.37Ω 700 600 500 400 FREQUENCY 600 FREQUENCY FREQUENCY AVERAGE = 400.01Ω 900 STD. DEV = 0.87Ω AVERAGE = 400.01Ω 800 STD. DEV = 1.0Ω 700 500 400 300 300 600 500 400 300 200 200 200 100 100 100 0 0.99 0.994 0.998 1.002 1.006 NORMALIZED RESISTANCE 0 1.01 0 0.99 0.994 0.998 1.002 1.006 NORMALIZED RESISTANCE 66012 G36 Normalized 33.3pF Capacitor Trim 1200 AVERAGE = 33.3pF 900 STD. DEV = 0.09pF 1000 700 FREQUENCY 400 AVERAGE = 48.2pF STD. DEV = 0.08pF 800 600 500 400 600 400 300 200 200 1.01 1000 800 600 0.994 0.998 1.002 1.006 NORMALIZED RESISTANCE Normalized 48.2pF Capacitor Trim 1000 AVERAGE = 21.1pF STD. DEV = 0.07pF 800 0.99 66012 G38 FREQUENCY 1200 1.01 66012 G37 Normalized 21.1pF Capacitor Trim FREQUENCY Normalized Feedback 400Ω Resistor Trim Normalized Input 400Ω Resistor Trim Normalized 200Ω Resistor Trim 200 100 0 0 0.984 0.990 0.997 1.003 1.009 NORMALIZED CAPACITANCE 1.015 0.988 0.993 0.999 1.005 1.010 NORMALIZED CAPACITANCE 0 1.016 0.992 0.995 0.998 1.001 1.004 1.007 1.010 NORMALIZED CAPACITANCE 66012 G40 66012 G39 66012 G41 Normalized 10.55pF Capacitor Trim Normalized 81.5pF Capacitor Trim 1000 Normalized 16.1pF Capacitor Trim 350 400 AVERAGE = 81.5pF 900 STD. DEV = 0.1pF AVERAGE = 10.55pF 350 STD. DEV = 0.03pF 300 AVERAGE = 16.1pF STD. DEV = 0.05pF 800 300 600 500 400 250 250 FREQUENCY FREQUENCY FREQUENCY 700 200 150 300 0 50 50 100 0.993 0.996 0.999 1.002 1.004 1.007 1.010 NORMALIZED CAPACITANCE 66012 G42 0 150 100 100 200 200 0.987 0.991 0.996 1.000 1.005 1.009 1.014 NORMALIZED CAPACITANCE 66012 G43 0 0.988 0.992 0.995 0.999 1.003 1.006 1.010 1.014 NORMALIZED CAPACITANCE 66012 G44 66012f 11 LTC6601-2 PIN FUNCTIONS (Refer to the Block Diagram) IN1+, IN2+, IN4+ (Pins 2, 1, 20): Input to a trimmed 100Ω, 200Ω, 400Ω resistor which feeds a noninverting summing node. Can accept an input signal, be floated or tied to OUT–. For best performance, stray capacitance should be kept as low as possible by keeping printed circuit connections as short and direct as possible. If necessary, strip back the surrounding ground plane away from these pins. BIAS (Pin 3): Input to a three-state comparator whose three states allow the user to tailor amplifier power. The pin impedance appears as a 150k resistor whose default open-circuit potential is 1.15V with respect to the V– power supply. If BIAS is driven to within 0.4V of the V– supply, the amplifier is placed into a low power shutdown, consuming typically 450μA. When BIAS is floated, the amplifier operates in its low power active state. Forcing the pin 2.3V above V– places the part into the high performance active state. See Applications Information for more detail. IN1–, IN2–, IN4– (Pins 4, 5, 6): Input to a trimmed 100Ω, 200Ω, 400Ω resistor which feeds an inverting summing node. Can accept an input signal, be floated or tied to OUT+. For best performance, it is highly recommended that stray capacitance be kept to as low as possible by keeping printed circuit connections as short and direct as possible, and if necessary, stripping back nearby surrounding ground plane away from these pins. C1, C2 (Pins 7, 8): Input to a trimmed 16.1pF, 33.3pF capacitor which feeds a noninverting summing node. Typically, either float or tie to OUT–. If either of these pins is tied to a low impedance source other than OUT–, a resistance of at least 25Ω should be placed in series. For best performance, it is highly recommended that stray capacitance be kept to as low as possible by keeping printed circuit connections as short and direct as possible, and if necessary, stripping back nearby surrounding ground plane away from these pins. C3, C4 (Pins 9, 10): Input to a trimmed 10.55pF, 21.1pF capacitor which feeds the amplifier inverting summing node. Typically, either float or tie to OUT+. For best performance, it is highly recommended that stray capacitance be kept to as low as possible by keeping printed circuit connections as short and direct as possible, and if necessary, stripping back nearby surrounding ground plane away from these pins. OUT+, OUT– (Pins 11, 15): Output Pins. Besides driving the internal feedback network, each pin can drive an additional 50Ω to ground with typical short-circuit current limiting of ±65mA. Capacitive loading of these pins should be minimized by resistively decoupling the outputs from the load with at least 25Ω. VOCM (Pin 12): Output Common Mode Reference Voltage. The voltage on VOCM sets the output common mode voltage level (which is defined as the average of the voltages on the OUT+ and OUT– pins). The VOCM pin is the midpoint of an internal resistive voltage divider between the supplies, developing a (default) mid-supply voltage potential to maximize output signal swing. The VOCM pin can be overdriven by an external voltage reference capable of driving the input impedance presented by the VOCM pin. The VOCM pin has an input resistance of approximately 7k to a mid-supply potential. It should be bypassed with a high quality ceramic bypass capacitor (for instance of X7R dielectric) of at least 0.01μF, (unless using symmetrical split supplies, then connect directly to a low impedance, low noise ground plane) to minimize common mode noise from being converted to differential noise by impedance mismatches both externally and internally to the IC. 66012f 12 LTC6601-2 PIN FUNCTIONS (Refer to the Block Diagram) V+, V– (Pins 14, 13): Power Supply Pins. It is critical that close attention be paid to supply bypassing. For single supply applications (Pin 13 grounded), it is recommended that a high quality 0.1μF surface mount ceramic bypass capacitor (X7R dielectric for instance) be placed between Pins 14 and 13, with direct short connections. Pin 13 should be tied directly to a low impedance ground plane with minimal routing. For dual (split) power supplies, it is recommended that at least two additional high quality 0.1μF ceramic capacitors are used to bypass V+ to ground and V– to ground, again with minimal routing. For driving large loads (< 200Ω), additional bypass capacitance may be added for optimal performance. Keep in mind that small geometry (e.g., 0603) surface mount ceramic capacitors have a much lower ESL than do leaded capacitors, and perform best in high speed applications. C5, C6 (Pins 19, 18): Input to a trimmed 16.1pF, 33.3pF capacitor which feeds an inverting summing node. Typically, either float or tie to OUT+. If either of these pins are tied to a low impedance source other than OUT+, a resistance of at least 25Ω should be placed in series. For best performance, it is highly recommended that stray capacitance be kept to as low as possible by keeping printed circuit connections as short and direct as possible, and if necessary, stripping back nearby surrounding reference plane away from these pins. Exposed Pad (Pin 21): Always tie the underlying Exposed Pad to V– (Pin 13). If split supplies are used, do not tie the pad to ground. Tie it to V–. C7, C8 (Pins 17, 16): Input to a trimmed 10.55pF, 21.1pF capacitor which feeds the amplifier noninverting summing node. Typically, either float or tie to OUT–. For best performance, stray capacitance should be kept as low as possible by keeping printed circuit connections as short and direct as possible.If necessary, strip back the surrounding ground plane away from these pins. 66012f 13 LTC6601-2 BLOCK DIAGRAM 20 19 IN4+ 18 C5 17 16.1pF 400Ω 16 C8 C7 C6 33.3pF 81.5pF 400Ω 1 IN2+ 200Ω 10.55pF OUT– 15 21.1pF 2 IN1+ 100Ω V+ 48.2pF 14 V – + 2.3V 860Ω 180k 3 BIAS 125Ω 60k BIAS V– + – 125Ω 180k 860Ω 14k 48.2pF 4 IN1– 100Ω 14k VOCM IN2– 12 21.1pF OUT+ 10.55pF 5 13 200Ω 11 400Ω 81.5pF 400Ω IN4– 6 33.3pF 16.1pF C1 7 C2 8 C3 9 C4 10 66012 BD 66012f 14 LTC6601-2 TEST CIRCUITS 20 19 18 17 16 LTC6601-2 1 15 2 VOUT– + V+ 14 VINP – BIAS 0.1μF + – 3 IL 25Ω RBAL 0.1μF 13 V– 0.1μF 12 VOCM 0.01μF VOUT(CM) – VINM + 4 11 5 6 7 8 9 VOUT+ RBAL IL 25Ω 10 66012 F01 Figure 1. DC Test Circuit LTC6601-2 5V 6 9 10 11 12 VIN 14 LT6411 15 19 18 17 16 1 1μF 13 20 15 8 VOUT– 100Ω 1μF 2 VINP 5 16 BIAS 0.1μF + – 1 2 3 7 17 3 V– 0.1μF 12 VOCM 0.01μF 4 11 5 6 7 8 9 0.1μF 13 –5V 1μF VINM COILCRAFT TTWB-4-B V+ 14 VOUT+ 100Ω 50Ω 1μF 10 66012 F02 Figure 2. AC Test Circuit (Frequency Response Testing) 66012f 15 LTC6601-2 APPLICATIONS INFORMATION FUNCTIONAL DESCRIPTION Figure 3 shows the basic filter architecture. The Laplace transfer function from VINDIFF to VOUTDIFF is given by the following generalized equation for a 2nd order lowpass filter: The LTC6601 is designed to make the implementation of high frequency fully-differential filtering functions very easy. A very low noise amplifier is surrounded by 8 precision matched resistors and 12 precision matched capacitors so that a myriad of filter transfer functions limited only by possible combinations and imagination can be configured by hard wiring pins. The amplifier itself is a wide band, low noise and low distortion fully-differential amplifier with accurate output phase balancing. It is optimized for driving low voltage, single-supply, differential input, analog-to-digital converters (ADCs). The LTC6601’s outputs are capable of swinging rail-to-rail on supplies as low as 2.7V, which makes the amplifier ideal for converting ground referenced, single-ended signals into VOCM referenced differential signals. Unlike traditional op amps which have a single output, the LTC6601 has two outputs to process signals differentially. This allows for two times the signal swing in low voltage systems when compared to single-ended output amplifiers. The balanced differential nature of the amplifier and matched surrounding components provide even-order harmonic distortion cancellation, and less susceptibility to common mode noise (like power supply noise). The LTC6601 can be used as a single-ended input to differential output amplifier, or as a differential input to differential output amplifier. VOUTDIFF = VINDIFF Gain 1+ s s2 + 2πfO • Q ( 2πf O )2 Both Gain and Q of the filter are based on component ratios, which match and track extremely well over temperature. The corner frequency of the filter is a function of an RC product. This RC product is trimmed to ±1% (typical) and is not expected to drift by more than ±1% from nominal over the entire temperature range –40°C to 85°C. As a result, fully differential filters with tight magnitude, phase tolerance and repeatability are achieved. Although Figure 3 implies a differential input, the LTC6601 easily accepts single-ended inputs to either input, and will faithfully replicate the signal at the output in differential form. The LTC6601’s output common mode voltage, defined as the average of the two output voltages, is independent of the input common mode voltage, and is adjusted by applying a voltage on the VOCM pin. If the pin is left open, there is an internal resistive voltage divider, which develops a R2 C2 R1 fO = GAIN = + – VIN(DIFF) fO • R3 f3dB = C1 1 Q= 6089 • 0.2236 • fO • C2 1+ 1+ GAIN • R3 C2 – R2 C1 R2 R1 VOUT(DIFF) – + R1 C2 R3 • C1 R2 Q= C1 R3 1 2P R2 • R3 • C1• C2 (3568 • Q 4 ) ( ) 1788 • Q 2 + 447 + 1.287 • 105 • 2 • Q 2 1 507.6 • Q (9.891• 10 • f (16 • f • (8.29 • 10 • f 5 2.109 • 10 • 12 O 2 3dB 9 4 ) ( ) 5.486 • 109 • fO4 + 120 • 5.526 • 109 • f3dB2 + 3.082 • 106 • fO2 3dB 2 ) + 4.127 • 109 • fO2 6.638 • 1010 • f3dB 4 ) R2 66012 F03 Figure 3. Basic Filter Topology and Equations 66012f 16 LTC6601-2 APPLICATIONS INFORMATION potential halfway between the V+ and V– pins. Whenever this pin is not hard tied to a low impedance ground plane, a high quality ceramic capacitor should be used to bypass the VOCM pin to a low impedance ground plane (see Layout Considerations). The LTC6601’s internal common mode feedback path forces accurate output phase balancing to reduce even order harmonics, and centers each individual output about the potential set by the VOCM pin. VOUT + + VOUT – VOUTCM = VOCM = 2 The outputs (OUT+ and OUT–) of the LTC6601 are capable of swinging rail-to-rail. They can source or sink up to approximately 75mA of current. Load capacitances should be decoupled with at least 25Ω of series resistance from each output. The LTC6601 Electrical Characteristics table specifies an input referred offset. This specification actually lumps voltage offsets due to offset bias currents (IOS), and amplifier voltage offset into one specification. To refer this specification to the output, you simply multiply the specification by the noise gain the LTC6601 is configured in: VOSODIFF = 1 + Gain where Gain is the closed loop gain in the particular filter application: Gain = R2 R1 COMPONENT INPUT PIN PROTECTION All of the LTC6601 pins with the exception of V+ and V– are protected with steering diodes to either power supply. In the event that a pin is driven beyond the supply rails, the excess current should be limited to under 10mA to prevent damage to the IC. BIAS Pin The LTC6601 has a BIAS pin (Pin 3) whose function is to tailor both performance and power of the LTC6601. The pin has a Thevenin equivalent impedance of approximately 150kΩ to a voltage source whose potential is 1.15V above the V– supply. This pin has fixed logic levels relative to V– (see the Electrical Characteristics table), and can be driven by an external source keeping in mind its equivalent input impedance and equivalent input voltage. If the BIAS pin is floated, care should be taken to control external leakage currents to this pin to under 1μA to prevent putting the LTC6601 an undesired state. If BIAS is tied to the positive supply, the LTC6601 differential filter will be in a fully active state configured for highest performance (lowest noise and lowest distortion). If the BIAS pin is floated or left unconnected, the LTC6601 filter will be in a fully active state, with amplifier currents reduced and performance scaled back to preserve power consumption. If the BIAS pin is tied to the most negative supply (V–), the LTC6601 will be placed into a low power shutdown mode with amplifier outputs disabled. In this state, the LTC6601 draws approximately 450μA. In low power shutdown, all internal biasing current sources are shut off, and the output pins, OUT+ and OUT–, will each appear as open collectors with a non-linear capacitor in parallel and steering diodes to either supply. The turn-on and turn-off time constant between states are on the order of 0.4μs. Using this function to wire-OR outputs together is not recommended. General Design and Usage As levels of integration have increased and correspondingly, system supply voltages decreased, there has been a need for ADCs to process signals differentially in order to maintain good signal-to-noise ratios. These ADCs are typically supplied from a single supply voltage which can be as low as 3V (2.7V min), and will have an optimal common mode input range near mid-supply. The LTC6601 makes interfacing to these ADCs easy, by providing antialias filtering, single-ended to differential conversion and common mode level shifting (translation). Figure 3 shows a general application of this. The low frequency gain to VOUTDIFF from VIN is simply: VOUTDIFF = VOUT + – VOUT – ≈ R2 •V R1 INDIFF The differential output voltage (VOUT+ – VOUT–) is completely independent of input and output common mode voltages, or the voltage at the common mode pin. This makes the 66012f 17 LTC6601-2 APPLICATIONS INFORMATION LTC6601 ideally suited for pre-amplification, level shifting and conversion of single-ended signals to differential output signals for driving differential input ADCs. INPUT IMPEDANCE Figure 4 shows a simplified low frequency equivalent circuit of the LTC6601. For balanced input sources (VINP = –VINM), the low frequency input impedance is given by the equation: RINP = RINM = R1 The differential input impedance is simply: RINDIFF = 2 • R1 For single-ended inputs (VINM = 0), the input impedance actually increases over the balanced differential case due to the fact the summing node (at the junction of R1, R2 and R3) moves in phase with VINP to bootstrap the input impedance. Referring to Figure 4 with VINM = 0, the input impedance looking into either input is: R1 ⎛ 1 ⎛ R2 ⎞ ⎞ ⎜⎝ 1– 2 • ⎜⎝ R1+ R2 ⎟⎠ ⎟⎠ + VINP – – VINM RINM VOUT– + VOUTDIFF – R1 + R2 For the general case, the upper input common mode voltage limit should be constrained to: VOCM • R1 R2 + VINCM • ≤ V + – 1.4V R1+ R2 R1+ R2 ( – R3 The lower limit of the input common mode range is dictated by the ESD protection diodes at the input. While it is possible for the inputs to swing below V–, the diodes will conduct if the inputs are taken a diode drop below V–. The upper limit of the input common mode range varies as a function of the filter configuration (GAIN), VOCM potential, and whether or not the inputs are single-ended or differential. While it is possible to exceed the upper limit of the common mode range, doing so will degrade filter linearity. Referring to Figure 4, for linear operation, the summing junction where R1, R2 and R3 merge together should be prevented from swinging to within 1.4V of the V+ power supply. ) R1 ⎛ R1⎞ VINCM ≤ ⎜ 1+ ⎟ V + − 1.4V − •V ⎝ R2 ⎠ R2 OCM R1 R3 VINP + VINM 2 Or equivalently: R2 RINP The input common mode voltage is defined as the average of the two inputs: VINCM = Calculating the low frequency input impedance of the LTC6601 depends on how the inputs are driven (whether they are driven from a single-ended or a differential source). RINP = RINM Input and Output Common Mode Voltage Range + VOUT+ VOCM The specifications for input common mode range (VINCMR) are based on these constraints with R1 = R2 = 100Ω, and VOCM = mid-supply. Substituting the numbers for a single 3V power supply, (V+ = 3V, V– = 0V) with VOCM =1.5V, and R1 = R2 = 100Ω, into the above equation, the input common mode range (VINCMR) is between the two limits: 0V ≤ VINCM ≤ 1.7V which is as is specified for a 3V supply. 0.1μF 66012 F04 Figure 4. Input Impedance 66012f 18 LTC6601-2 APPLICATIONS INFORMATION Likewise, substituting the numbers for a single 5V power supply, (V+ = 5V, V– = 0V) with VOCM = 2.5V, and R1 = R2 = 100Ω, into the above equation, the input common mode range (VINCMR) is between the two limits: 0V ≤ VINCM ≤ 4.7V The output common mode voltage is defined as the average of the two outputs: VOUTCM = VOCM = VOUT + + VOUT – 2 The VOCM pin sets this average by an internal common mode feedback loop which internally forces VOUT+ = –VOUT–. The output common mode range extends from 1.1 V above V– to 1V below V+. The VOCM pin sits in the middle of a voltage divider which sets the default midsupply open circuit potential. In single supply applications, where the LTC6601 is used to interface to an ADC, the optimal common mode input to the ADC is often determined by the ADC’s reference. If the ADC makes a reference available for setting the input common mode voltage, it can be directly tied to the VOCM pin, but must be capable of driving the input impedance of the VOCM pin (RVOCM). This impedance can be assumed to be connected to a mid-supply potential. If an external reference drives the VOCM pin, it should still be bypassed with a high quality 0.01μF or higher capacitor to a low impedance ground plane to filter any thermal noise and to prevent common mode signals on this pin from being inadvertently converted to differential signals. Noise Considerations When comparing the LTC6601 noise to other amplifiers, be sure to compare similar specifications. Competing devices often specify noise referred to the inputs of the amplifier. The input referred voltage noise of the LTC6601-2 is 4.7nV/√Hz. In addition to the noise generated by the amplifier, the surrounding feedback resistors also contribute noise. A noise model is shown in Figure 5. The output spot noise generated by both the amplifier and the feedback components is governed by the equation: 2 2 2 2 ⎛ ⎛ ⎛ ⎛ ⎛ R2 ⎞ ⎞ ⎞ ⎛ R2 ⎞ ⎞ ⎛ R2 ⎞ ⎞ ⎛ R2 ⎞ ⎞ 2 2 2 ⎛ eno = ⎜ eni • ⎜ 1+ ⎟ ⎟ + 2 • ⎜ In • ⎜ R2 + R3 • ⎜ 1+ ⎟ ⎟ ⎟ + 2 • ⎜ enR1 • ⎜ ⎟ ⎟ + 2 ⎜ enR3 • ⎜ 1+ ⎟ ⎟ + 2 • enR2 2 ⎝ R1⎠ ⎠ ⎟⎠ ⎝ R1⎠ ⎠ ⎝ R1⎠ ⎠ ⎝ R1⎠ ⎠ ⎜⎝ ⎝ ⎝ ⎝ ⎝ Substituting the equation for Johnson noise of a resistor (enR = 4kTR), and simplifying: 2 2 2 ⎛ ⎛ ⎛ ⎛ R2 ⎞ ⎛ ⎛ R2 ⎞ ⎞ ⎞ ⎛ R2 ⎞ ⎞ ⎛ R2 ⎞ ⎞ eno = ⎜ eni • ⎜ 1+ ⎟ ⎟ + 2 • ⎜ In 2 • ⎜ R22 + R32 • ⎜ 1+ ⎟ ⎟ ⎟ + 8 • k • T ⎜ R2 ⎜ 1+ ⎟ + R3 ⎜ 1+ ⎟ ⎟ ⎝ R1⎠ ⎠ ⎟⎠ ⎝ R1⎠ ⎠ ⎝ R1⎠ ⎠ ⎜⎝ ⎝ ⎝ ⎝ ⎝ R1⎠ 66012f 19 LTC6601-2 APPLICATIONS INFORMATION enR22 R2 * enR12 In+2 R1 enR32 * R3 * + * enR32 enR12 eni2 eno2 R3 – * R1 In–2 * enR22 * R2 66012 F05 Figure 5. Differential Noise Model of the LTC6601 Table 1 lists the amplifier input referred noise for the LTC6601-2. Tables 2 to10 list the noise referred to the input pins of the IC for common configurations of the LTC6601-2. To determine the spot noise at the output, simply multiply the noise by the Gain = R2/R1. To estimate the integrated noise at the output, multiply the noise by the gain, and the square root of the noise bandwidth. The noise bandwidth depends on the filter configuration. For Figure 2, the noise bandwidth is 100MHz, or approximately 7 times the filter bandwidth. Improvements in SNR can be made by adding an additional RC filter at the output to band limit wide band noise before feeding ADCs. See the section “Interfacing the LTC6601 to ADC Converters” for more detail. Table 1. Amplifier (Input Referred) Noise Characteristics for the LTC6601-2 BIAS PIN PULLED TO V+ BIAS PIN FLOATING eni nV/√Hz in pA/√Hz eni nV/√Hz in pA/√Hz 4.7 3 5.2 2.1 LAYOUT CONSIDERATIONS Because the LTC6601 is a very high speed amplifier, it is sensitive to both stray capacitance and stray inductance. It is critical that close attention be paid to supply bypassing. For single supply applications, it is recommended that a high quality 0.1μF surface mount ceramic bypass capacitor be placed between Pins 14 and 13 with direct short connections. Pin 13 and the Exposed Pad, Pin 21, should be tied directly to a low impedance ground plane with minimal routing. For dual (split) power supplies, it is recommended that an additional high quality, 0.1μF ceramic capacitor be used to bypass pin V+ to ground and V– to ground, again with minimal routing. For driving large differential loads (<200Ω), additional bypass capacitance may be needed between V+ and V– for optimal performance. Note that small geometry (e.g., 0603) surface mount ceramic capacitors have a much higher self resonant frequency than capacitors with leads, and perform best in high speed applications. The VOCM pin should be bypassed to ground with a high quality ceramic capacitor whose value exceeds 0.01μF, with direct, short connections. In split supply applications, the VOCM pin can be either bypassed to ground or directly hardwired to ground. Be careful not to violate the output common mode range specifications for the VOCM pin. Stray parasitic capacitances to unused component pins that set up the filter’s characteristics, should be kept to an absolute minimum. This prevents deviations from the ideal frequency response. An ideal layout technique would be to remove the solder pads for the unused component pins, and strip away the ground plane underneath these pins to lower capacitance to an absolute minimum. Floating unused component pins which set up the filter characteristics will not reduce the reliability of the LTC6601. At the output, always keep in mind the differential nature of the LTC6601, and that it is critical that the load impedances seen by both outputs (stray or intended), should be as balanced and symmetric as possible. This will help preserve the natural balance of the LTC6601, which minimizes the generation of even order harmonics and preserves the rejection of common mode signals and noise. 66012f 20 LTC6601-2 APPLICATIONS INFORMATION INTERFACING THE LTC6601 TO ADC CONVERTERS The LTC6601’s rail-to-rail differential output and adjustable output common mode voltage make the LTC6601 ideal for interfacing to low voltage, single supply, differential input ADCs. The sampling process of ADCs creates a sampling transient that is caused by the switching-in of the ADC sampling capacitor. The switching-in of this sampling capacitor momentarily “shorts” the output of the amplifier as charge is transferred between amplifier and sampling capacitor. The amplifier must recover and settle from this load transient before this acquisition period has ended, for a valid representation of the input signal. The LTC6601 will settle much more quickly from these periodic load impulses than it does from a 2V input step, but it is a good idea to add an RC network after the outputs of the LTC6601 to decouple the sampling transient of the ADC (See Figure 6). The capacitance of the decoupling network serves to provide the bulk of the charge during the sampling process, while the two resistors of the filter network are used to dampen and attenuate any transient induced by the ADC. The ADC’s sampling bandwidth will LTC6601-2 20 19 18 17 15 2 VOUT– C1 R CONTROL VIN – 3V 14 BIAS The selection of the RC time constant is trial and error for a given ADC, but the following guidelines are recommended. Choose an RC pole frequency greater than the cutoff frequency of the LTC6601. 80MHz RC filters are good for filtering broadband noise. Lower frequency RC filters improve SNR at the expense of settling time. The resistors in the decoupling network should be at least 25Ω. Too much resistance in the decoupling network leaves insufficient settling time and will create a voltage divider between the dynamic input impedance of the ADC and the decoupling resistors. Using insufficient resistance might prevent proper dampening of the load transient caused by the sampling process, and prolong the time required for settling. In 16-bit applications, this will typically require a minimum of 11 RC time constants. It is recommended that the capacitor is chosen with low dielectric absorption (such as a C0G multilayer ceramic capacitor). 16 1 + often be much greater than that of the LTC6601, so having this discrete RC filter will give the additional benefit of band limiting broadband output noise. 0.1μF + – 3 C2 13 AIN– VOCM 10nF 12 1μF 4 11 5 D15 • • D0 AIN+ 1μF VOUT+ VCM GND 1μF 3.3V 1μF 2.2μF R C1 66012 F06 6 7 8 9 10 t = R • (C1 + 2 • C2) Figure 6. Interfacing the LTC6601 to A/D Converters 66012f 21 LTC6601-2 APPLICATIONS INFORMATION A GALLERY OF BASIC FILTER TOPOLOGIES Tables 2 through 10 list (sorted by Gain) a hundred possible filter topologies that can be easily implemented with the LTC6601. The tables also list the LTC6601-2 approximate midband (1MHz) spot noise ein referred to the input resistor, R1 (with the BIAS pin pulled to V+). The gains for these topologies range from 1V/V to 7V/V. The Qs listed are within the range of 0.54 and 1.72. The fOs listed are in the range of 6.96MHz and 22.71MHz, and the –3dB frequencies listed range from 5.5MHz to 27.5MHz. For all filters listed, R3 = 125Ω. Figures 7 to 10 show how to pin-strap each filter configuration. Table 2. Gain of 7 Filter Configurations GAIN V/V dB fO (MHz) 7.0 16.902 7.0 16.902 7.0 7.0 C2 (pF) ein (nV/√Hz) 48.2 97.6 6.1 48.2 114.8 6.1 400.00 48.2 130.9 6.1 400.00 58.75 130.9 6.1 C2 (pF) ein (nV/√Hz) f–3dB (MHz) Q R1 (Ω) R2 (Ω) C1 (pF) 10.38 7.43 0.539 57.14 400.00 9.57 10.36 0.771 57.14 400.00 16.902 8.96 12.10 1.175 57.14 16.902 8.12 7.49 0.656 57.14 Table 3. Gain of 6 Filter Configurations GAIN V/V dB fO (MHz) f–3dB (MHz) Q R1 (Ω) R2 (Ω) C1 (pF) 6.0 15.563 10.38 10.03 0.684 66.67 400.00 48.2 97.6 6.2 6.0 15.563 9.57 12.52 1.071 66.67 400.00 48.2 114.8 6.2 6.0 15.563 8.67 7.67 0.634 66.67 400.00 58.75 114.8 6.2 6.0 15.563 8.12 9.59 0.870 66.67 400.00 58.75 130.9 6.2 6.0 15.563 7.47 6.07 0.592 66.67 400.00 69.3 130.9 6.2 Table 4. Gain of 5 Filter Configurations GAIN V/V dB fo (MHz) f–3dB (MHz) Q R1 (Ω) R2 (Ω) C1 (pF) C2 (pF) ein nV/√Hz 5.0 13.979 11.36 9.67 0.614 80.00 400.00 48.2 81.5 6.5 5.0 13.979 10.38 12.78 0.936 80.00 400.00 48.2 97.6 6.5 5.0 13.979 9.40 7.67 0.594 80.00 400.00 58.75 97.6 6.5 5.0 13.979 8.67 10.07 0.849 80.00 400.00 58.75 114.8 6.5 5.0 13.979 8.12 11.25 1.290 80.00 400.00 58.75 130.9 6.5 5.0 13.979 7.98 6.46 0.591 80.00 400.00 69.3 114.8 6.5 5.0 13.979 7.47 8.16 0.779 80.00 400.00 69.3 130.9 6.5 5.0 13.979 6.96 5.50 0.579 80.00 400.00 79.85 130.9 6.5 66012f 22 LTC6601-2 APPLICATIONS INFORMATION Table 5. Gain of 4 Filter Configurations GAIN V/V dB fO (MHz) f–3dB MHz Q R1 (Ω) R2 (Ω) C1 (pF) C2 (pF) ein nV/√Hz 4.0 12.041 11.36 13.05 0.834 100.00 400.00 48.2 81.5 6.8 4.0 12.041 10.38 14.80 1.480 100.00 400.00 48.2 97.6 6.8 4.0 12.041 9.40 10.47 0.799 100.00 400.00 58.75 97.6 6.8 4.0 12.041 8.67 12.00 1.284 100.00 400.00 58.75 114.8 6.8 4.0 12.041 8.65 6.76 0.575 100.00 400.00 69.3 97.6 6.8 4.0 12.041 7.98 8.84 0.794 100.00 400.00 69.3 114.8 6.8 4.0 12.041 7.43 6.09 0.596 100.00 400.00 79.85 114.8 6.8 4.0 12.041 7.47 10.00 1.141 100.00 400.00 69.3 130.9 6.8 4.0 12.041 6.96 7.57 0.775 100.00 400.00 79.85 130.9 6.8 Table 6. Gain of 3 Filter Configurations GAIN V/V dB fO (MHz) f–3dB (MHz) Q R1 (Ω) R2 (Ω) C1 (pF) C2 (pF) ein (nV/√Hz) 3.0 9.542 16.06 12.36 0.568 66.67 200.00 48.2 81.5 7.1 3.0 9.542 14.68 15.74 0.763 66.67 200.00 48.2 97.6 7.1 3.0 9.542 13.53 17.83 1.091 66.67 200.00 48.2 114.8 7.1 3.0 9.542 13.29 9.88 0.554 66.67 200.00 58.75 97.6 7.1 3.0 9.542 12.26 12.39 0.715 66.67 200.00 58.75 114.8 7.1 3.0 9.542 11.36 15.77 1.300 133.33 400.00 48.2 81.5 7.4 3.0 9.542 11.48 14.07 0.928 66.67 200.00 58.75 130.9 7.1 3.0 9.542 11.29 8.34 0.552 66.67 200.00 69.3 114.8 7.1 3.0 9.542 10.29 11.04 0.763 133.33 400.00 58.75 81.5 7.4 3.0 9.542 10.57 10.06 0.674 66.67 200.00 69.3 130.9 7.1 3.0 9.542 9.40 12.85 1.224 133.33 400.00 58.75 97.6 7.4 3.0 9.542 8.65 9.54 0.788 133.33 400.00 69.3 97.6 7.4 3.0 9.542 8.06 6.69 0.601 133.33 400.00 79.85 97.6 7.4 3.0 9.542 7.98 10.88 1.212 133.33 400.00 69.3 114.8 7.4 3.0 9.542 7.43 8.48 0.825 133.33 400.00 79.85 114.8 7.4 3.0 9.542 6.96 9.40 1.172 133.33 400.00 79.85 130.9 7.4 3.0 9.542 9.85 7.13 0.544 66.67 200.00 79.85 130.9 7.1 66012f 23 LTC6601-2 APPLICATIONS INFORMATION Table 7. Gain of 2 Filter Configurations GAIN C1 (pF) C2 (pF) ein (nV/√Hz) 200.00 48.2 81.5 8.1 200.00 58.75 81.5 8.1 200.00 48.2 97.6 8.1 200.00 58.75 97.6 8.1 100.00 200.00 69.3 97.6 8.1 1.200 100.00 200.00 58.75 114.8 8.1 0.835 100.00 200.00 69.3 114.8 8.1 13.97 1.197 200.00 400.00 58.75 81.5 8.5 10.51 9.76 0.660 100.00 200.00 79.85 114.8 8.1 10.57 13.97 1.102 100.00 200.00 69.3 130.9 8.1 6.021 9.47 10.52 0.796 200.00 400.00 69.3 81.5 8.5 6.021 9.85 11.17 0.819 100.00 200.00 79.85 130.9 8.1 2.0 6.021 8.82 7.55 0.616 200.00 400.00 79.85 81.5 8.5 2.0 6.021 8.65 11.91 1.254 200.00 400.00 69.3 97.6 8.5 2.0 6.021 8.06 9.48 0.864 200.00 400.00 79.85 97.6 8.5 2.0 6.021 7.43 10.40 1.341 200.00 400.00 79.85 114.8 8.5 V/V dB fO (MHz) f–3dB (MHz) Q R1 (Ω) R2 (Ω) 2.0 6.021 16.06 18.95 0.868 100.00 2.0 6.021 14.55 12.69 0.626 100.00 2.0 6.021 14.68 20.46 1.323 100.00 2.0 6.021 13.29 15.34 0.840 100.00 2.0 6.021 12.24 10.96 0.640 2.0 6.021 12.26 16.66 2.0 6.021 11.29 12.98 2.0 6.021 10.29 2.0 6.021 2.0 6.021 2.0 2.0 Table 8. Gain of 1.667 Filter Configurations GAIN V/V dB fO (MHz) f–3dB MHz Q R1 (Ω) R2 (Ω) C1 (pF) C2 (pF) ein nV/√Hz 1.667 4.437 19.67 19.35 0.696 80.00 133.33 48.2 81.5 8.5 1.667 4.437 17.97 22.12 0.934 80.00 133.33 48.2 97.6 8.5 1.667 4.437 16.57 23.16 1.336 80.00 133.33 48.2 114.8 8.5 1.667 4.437 16.28 15.60 0.679 80.00 133.33 58.75 97.6 8.5 1.667 4.437 15.01 17.80 0.875 80.00 133.33 58.75 114.8 8.5 1.667 4.437 14.33 18.58 1.046 80.00 133.33 58.75 126 8.5 1.667 4.437 13.82 13.19 0.676 80.00 133.33 69.3 114.8 8.5 1.667 4.437 12.94 14.77 0.826 80.00 133.33 69.3 130.9 8.5 1.667 4.437 12.06 11.32 0.666 80.00 133.33 79.85 130.9 8.5 66012f 24 LTC6601-2 APPLICATIONS INFORMATION Table 9. Gain of 1.333 Filter Configurations GAIN C1 (pF) C2 (pF) ein nV/√Hz 133.33 48.2 81.5 9.4 133.33 58.75 81.5 9.4 133.33 48.2 97.6 9.4 133.33 58.75 97.6 9.4 100.00 133.33 69.3 97.6 9.4 1.097 100.00 133.33 58.75 114.8 9.4 1.506 100.00 133.33 58.75 130.9 9.4 15.61 0.814 100.00 133.33 69.3 114.8 9.4 12.88 12.03 0.663 100.00 133.33 79.85 114.8 9.4 12.94 16.64 1.025 100.00 133.33 69.3 130.9 9.4 12.06 13.45 0.801 100.00 133.33 79.85 130.9 9.4 V/V dB fO (MHz) f–3dB MHz Q R1 (Ω) R2 (Ω) 1.333 2.499 19.67 22.73 0.841 100.00 1.333 2.499 17.82 15.77 0.633 100.00 1.333 2.499 17.97 24.34 1.185 100.00 1.333 2.499 16.28 18.44 0.818 100.00 1.333 2.499 14.99 13.58 0.646 1.333 2.499 15.01 19.82 1.333 2.499 14.06 20.12 1.333 2.499 13.82 1.333 2.499 1.333 2.499 1.333 2.499 Table 10. Gain of 1 Filter Configurations GAIN V/V dB fO (MHz) f–3dB MHz Q R1 (Ω) R2 (Ω) C1 (pF) C2 (pF) ein nV/√Hz 1.0 0.0 22.71 25.40 0.804 100.0 100.0 48.2 81.5 10.7 1.0 0.0 20.75 27.23 1.079 100.0 100.0 48.2 97.6 10.7 1.0 0.0 20.57 17.86 0.623 100.0 100.0 58.75 81.5 10.7 1.0 0.0 19.14 27.50 1.543 100.0 100.0 48.2 114.8 10.7 1.0 0.0 18.80 20.62 0.784 100.0 100.0 58.75 97.6 10.7 1.0 0.0 17.31 15.35 0.634 100.0 100.0 69.3 97.6 10.7 1.0 0.0 17.33 22.15 1.011 100.0 100.0 58.75 114.8 10.7 1.0 0.0 16.23 22.58 1.312 100.0 100.0 58.75 130.9 10.7 1.0 0.0 15.96 17.45 0.781 100.0 100.0 69.3 114.8 10.7 1.0 0.0 14.55 19.09 1.079 200.0 200.0 58.75 81.5 11 1.0 0.0 14.87 13.57 0.650 100.0 100.0 79.85 114.8 10.7 1.0 0.0 14.95 18.59 0.954 100.0 100.0 69.3 130.9 10.7 1.0 0.0 13.39 14.90 0.798 200.0 200.0 69.3 81.5 11 1.0 0.0 13.92 15.04 0.769 100.0 100.0 79.85 130.9 10.7 1.0 0.0 12.48 11.38 0.650 200.0 200.0 79.85 81.5 11 1.0 0.0 12.24 16.25 1.115 200.0 200.0 69.3 97.6 11 1.0 0.0 11.40 13.27 0.850 200.0 200.0 79.85 97.6 11 1.0 0.0 11.29 16.47 1.715 200.0 200.0 69.3 114.8 11 1.0 0.0 10.51 14.17 1.167 200.0 200.0 79.85 114.8 11 1.0 0.0 9.47 13.26 1.350 400.0 400.0 69.3 81.5 11.8 1.0 0.0 8.82 10.86 0.935 400.0 400.0 79.85 81.5 11.8 1.0 0.0 8.06 11.57 1.535 400.0 400.0 79.85 97.6 11.8 66012f 25 LTC6601-2 APPLICATIONS INFORMATION 20 19 18 17 16 20 LTC6601-2 1 R1 57.14Ω 15 11 6 7 8 9 10 20 19 18 17 16 15 11 6 7 8 9 10 20 19 18 17 16 10 20 19 18 17 16 15 + – 11 6 7 8 9 10 20 19 18 17 16 LTC6601-2 1 15 1 + 11 8 9 + 4 – 5 15 2 R1 200Ω 7 9 5 LTC6601-2 6 8 4 – 4 7 2 R1 100Ω 2 6 1 + 5 R1 133.33Ω 11 LTC6601-2 1 4 – 5 LTC6601-2 2 16 + 4 – 5 R1 80Ω 17 15 2 R1 66.66Ω 4 18 1 + 2 19 LTC6601-2 – 5 11 10 6 20 19 18 17 7 8 9 10 16 LTC6601-2 1 R1 400Ω 15 + 2 4 – 5 11 6 7 8 9 10 66012 F07 Figure 7. Pin-Strap Hookup for a Particular R1 66012f 26 LTC6601-2 APPLICATIONS INFORMATION 20 19 18 17 16 20 LTC6601-2 1 15 5 11 6 7 8 9 10 20 19 18 17 16 – 11 6 7 8 9 10 20 19 18 17 16 LTC6601-2 1 15 1 + 11 7 8 9 + R2 400Ω 4 – 5 15 2 R2 200Ω 6 R2 133Ω 5 LTC6601-2 4 16 + 4 – 2 17 15 2 R2 100Ω 4 18 1 + 2 19 LTC6601-2 – 5 11 10 6 7 8 9 66012 F08 10 Figure 8. Pin-Strap Hookup for a Particular R2 20 19 18 17 16 20 LTC6601-2 1 15 C1 48.2pF 4 – 5 11 6 7 8 9 10 20 19 18 17 16 C1 58.75pF 4 – 11 6 7 8 9 10 20 19 18 17 16 1 + C1 69.3pF – 5 11 7 + 5 15 6 16 LTC6601-2 1 4 17 15 2 LTC6601-2 2 18 1 + 2 19 LTC6601-2 8 9 10 15 + 2 C1 79.85pF 4 – 5 11 6 7 8 9 10 66012 F09 Figure 9. Pin-Strap Hookup for a Particular C1 66012f 27 LTC6601-2 APPLICATIONS INFORMATION 20 19 18 17 16 20 LTC6601-2 1 15 C2 81.5pF 4 – 5 11 6 7 8 9 10 20 19 18 17 16 C2 114.8pF 4 – 11 6 7 8 9 10 20 19 18 17 16 1 + C2 97.6pF – 5 11 7 + 5 15 6 16 LTC6601-2 1 4 17 15 2 LTC6601-2 2 18 1 + 2 19 LTC6601-2 8 9 10 15 + 2 C2 130.9pF 4 – 5 11 6 7 8 9 10 66012 F10 Figure 10. Pin-Strap Hookup for a Particular C2 66012f 28 LTC6601-2 APPLICATIONS INFORMATION Example Filter Configurations of Basic 2nd Order Filters Figure 11 shows some simplified component hookups of a selection of filters taken from Tables 7, 9 and 10. For 20 19 18 17 simplicity, VOCM pin bypass and power supply bypass are not shown. 16 20 LTC6601-2 1 15 VOUT(DIFF) – 11 7 19 VOUT(DIFF) 8 9 10 18 17 16 20 11 18 17 16 VOUT(DIFF) 8 9 – 5 10 11 6 GAIN = 6dB fO = 9.85MHz Q = 0.819 7 8 9 10 18 17 16 GAIN = 6dB fO = 16.06MHz Q = 0.868 19 18 17 16 20 LTC6601-2 15 1 + 15 + 2 VIN VOUT(DIFF) VIN VOUT(DIFF) 4 – 5 11 7 19 LTC6601-2 1 6 19 + 4 5 4 10 VIN – 2 9 15 2 VOUT(DIFF) 20 8 1 + VIN 7 7 LTC6601-2 15 6 11 GAIN = 0dB fO = 22.71MHz Q = 0.804 1 4 – 6 LTC6601-2 2 + 5 GAIN = 0dB fO = 13.92MHz Q = 0.769 20 16 VIN 4 5 6 17 15 2 VIN 4 18 1 + 2 19 LTC6601-2 8 9 10 – 5 11 6 7 8 9 10 66012 F11 GAIN = 2.5dB fO = 12.06MHz Q = 0.801 GAIN = 2.5dB fO = 19.67MHz Q = 0.841 Figure 11. Basic 2nd Order Filter Configurations 66012f 29 LTC6601-2 APPLICATIONS INFORMATION Figure 12 shows some simplified component hookups of a selection of filters taken from Tables 4, 5, and 6. For 20 19 18 17 simplicity, VOCM pin bypass and power supply bypass are not shown. 16 20 LTC6601-2 1 15 VOUT(DIFF) 11 VOUT(DIFF) 8 9 10 18 17 16 20 15 VOUT(DIFF) 11 17 16 VOUT(DIFF) 8 9 – 5 10 11 6 GAIN = 14dB fO = 6.96MHz Q = 0.579 7 8 9 10 18 17 16 GAIN = 14dB fO = 11.36MHz Q = 0.614 19 18 17 16 20 LTC6601-2 15 1 + 15 + 2 VIN VOUT(DIFF) VIN VOUT(DIFF) 4 – 5 11 7 19 LTC6601-2 1 6 18 + 4 5 7 19 VIN – 4 10 15 2 VIN 2 9 1 + 20 8 LTC6601-2 1 6 7 GAIN = 12dB fO = 11.36MHz Q = 0.834 19 4 11 6 LTC6601-2 2 – 5 GAIN = 12dB fO = 6.96MHz Q = 0.775 20 + 4 5 7 16 VIN – 6 17 15 2 VIN 4 18 1 + 2 19 LTC6601-2 8 9 10 – 5 11 6 7 8 9 10 66012 F12 GAIN = 9.54dB fO = 9.85MHz Q = 0.544 GAIN = 9.54dB fO = 16.06MHz Q = 0.568 Figure 12. Basic 2nd Order Filter Configurations 66012f 30 LTC6601-2 APPLICATIONS INFORMATION COMPLEX FILTER CONFIGURATIONS A Modified 2nd Order Lowpass Filter Topology The basic filter topology of Figure 3 can be modified as shown in Figure 13. The Figure 13 circuit includes an impedance path between the two summing nodes (the circuit nodes common to resistors R1, R2 and R3). A resistor and/or a capacitor connection between the summing nodes provide even more flexibility, and enhance the filter design options (the fO and Q equations shown in Figure 13 reduce to equations of Figure 3 if C3 is zero and R4 is infinite). The modified second order filter topology provides for setting the Q value (with R4) without changing the fO value and increasing the passband gain to greater than one without changing the Q value (in the Q equation of Figure 13 the value of Q does not change if the value of the [1 + GAIN + 2(R2/R4)] denominator factor does not change). Using R4 to set the Q value allows the option to design the –3dB frequency (f3dB). If the Q value varies and the fO value is constant then the f3dB frequency varies in a second order lowpass function (refer to the f3dB equation of Figure 13). Figures 14 to 17 show additional circuits highlighting the use of R4 or C3 in the modified second order cicuit to set the f3dB frequency to 13MHz, 19MHz, 22.7MHz and 24.6MHz respectively. The design procedure for a specified f3dB frequency is as follows: 1 Using the chosen C1, C2 and C3 values calculate the fO value. 2. Using fO of step 1 and the specified f3dB calculate the Q value. 3. Calculate the R4 value using the Q value of step 3. 4. Calculate the required external resistor REXT value for the R4 value in step 3. Example, in Figure 14 the Q value for f3dB = 5MHz is 0.54, the required R4 resistor is 350Ω, the R4A and R4B resistors are the internal 100Ω and the REXT resistor is 150Ω [REXT = R4 – (R4A + R4B)]. Note: The modified second order filter topology requires the use of at least two of the three input resistor pairs (two of the three 400Ω, 200Ω and 100Ω pairs). 66012f 31 LTC6601-2 APPLICATIONS INFORMATION R2 C2 R1 C1 R3 R4A + – C3A VIN(DIFF) REXT R4B VOUT(DIFF) 49.9Ω – + C3B C1 R3 R1 C2 R2 66012 F13 R4 = R4A + R4B + REXT C3 = C3A /2 (C3A = C3B) (3568 • Q 6089 • fO • f3dB = 4 ) ) 507.6 • Q (9.891• 10 • f (16 • f • (8.29 • 10 • f 5 2.109 • 10 • 0.2236 • fO • Q= 12 O 2 3dB 9 4 ) ( ) 5.486 • 109 • fO4 + 120 • 5.526 • 109 • f3dB2 + 3.082 • 106 • fO2 3dB 2 ) + 4.127 • 109 • fO2 6.638 • 1010 • f3dB 4 ) 1.25 • 10 4 • C1• Q • R2 R4 = 559 • C1• VOUT(DIFF) VIN(DIFF) GAIN = – fO = ( 1788 • Q 2 + 447 + 1.287 • 105 • 2 • Q 2 1 R2 • =– S2 + VOUT(DIFF) VIN(DIFF) ) ( GAIN R2 • R3 • C1• (C2 + 2 • C3) ) R1• R2 • (2 • R3 + R4) + R3 • R4 + R2 • R3 • R4 =– 1 2•• ( C2 + 2 • C3 50 • Q • C1• (125 • GAIN + R2 + 125) C2 • R2 C1 R1• R2 • R3 • R4 • (C2 + 2 • C3) •S+ 1 R2 • R3 • C1• (C2 + 2 • C3) R2 R1 R2 • R3 • C1• (C2 + 2 • C3) Q= R3 R2 • C2 C3 C1 + 2 • C1 R2 R3 C2 1+ 1+| GAIN | + 2 • • – R4 R2 C1 Figure 13. Modified Filter Topology and Equations 66012f 32 LTC6601-2 APPLICATIONS INFORMATION 20 19 18 17 16 20 LTC6601-2 1 VIN(DIFF) ZIN(DIFF) = 400Ω 15 VOUT(DIFF) 200Ω 4 5 VOUT(DIFF) 8 9 – 5 11 10 6 GAIN = 1 fO = 11.28MHz Q = 0.835 f–1dB = 10MHz f–3dB = 13MHz 7 8 9 GAIN = 2 fO = 11.28MHz Q = 0.835 f–1dB = 10MHz f–3dB = 13MHz Gain Magnitude vs Frequency (Gain = 1) 10 66012 F14a Passband Phase and Group Delay 30 5 0 0 PHASE –30 –5 PHASE (DEG) –15 –20 –90 –120 50 40 –25 30 GROUP DELAY –30 GROUP DELAY (ns) –60 –10 GAIN (dB) 16 + 4 11 7 17 15 2 VIN(DIFF) ZIN(DIFF) = 200Ω – 6 18 1 + 2 19 LTC6601-2 20 –35 10 –40 100k 1M 10M FREQUENCY (Hz) 100M 66012 F14b 0 100k 4M 0 16M 8M 12M FREQUENCY (Hz) 66012 F14c Figure 14. Modified Filter Configuration Using a Resistor Between Summing Nodes (f–3dB = 13MHz) 66012f 33 LTC6601-2 APPLICATIONS INFORMATION 20 19 18 17 16 20 LTC6601-2 1 15 VOUT(DIFF) 200Ω 4 VOUT(DIFF) 11 8 9 – 5 11 10 6 GAIN = 1 fO = 16MHz Q = 0.868 f–1dB = 15.4MHz f–3dB = 19MHz 7 8 9 10 66012 F15a GAIN = 2 fO = 16MHz Q = 0.868 f–1dB = 15.4MHz f–3dB = 19MHz Gain Magnitude vs Frequency (Gain = 1) Passband Phase and Group Delay 5 30 0 0 –5 –30 PHASE PHASE (DEG) –15 –20 –90 –120 50 40 –25 30 –30 GROUP DELAY 20 –35 –40 100k GROUP DELAY (ns) –60 –10 GAIN (dB) 16 + 4 5 7 17 15 2 VIN(DIFF) ZIN(DIFF) = 200Ω – 6 18 1 + 2 VIN(DIFF) ZIN(DIFF) = 400Ω 19 LTC6601-2 10 1M 10M FREQUENCY (Hz) 100M 66012 F15b 0 100k 4M 8M 12M FREQUENCY (Hz) 0 20M 16M 66012 F15c Figure 15. Modified Filter Configuration Using a Resistor Between Summing Nodes (f–3dB = 19MHz) 66012f 34 LTC6601-2 APPLICATIONS INFORMATION 20 33.2Ω 19 18 17 16 20 LTC6601-2 1 15 VOUT(DIFF) 4 33.2Ω VOUT(DIFF) 11 8 9 – 5 11 10 6 GAIN = 1 fO = 19.7MHz Q = 0.84 f–1dB = 19MHz f–3dB = 22.7MHz 7 8 9 10 66012 F16a GAIN = 1.33 fO = 19.7MHz Q = 0.84 f–1dB = 19MHz f–3dB = 22.7MHz Gain Magnitude vs Frequency (Gain = 1) Passband Phase and Group Delay 5 30 0 0 –5 –30 PHASE PHASE (DEG) –15 –20 –90 –120 50 40 –25 30 –30 GROUP DELAY (ns) –60 –10 GAIN (dB) 16 + 4 5 7 17 15 2 VIN(DIFF) ZIN(DIFF) = 200Ω – 6 18 1 + 2 VIN(DIFF) ZIN(DIFF) = 266Ω 19 LTC6601-2 20 GROUP DELAY –35 10 –40 100k 1M 10M FREQUENCY (Hz) 100M 66012 F16b 0 100k 4.6M 9.2M 13.8M 18.4M FREQUENCY (Hz) 0 23M 66012 F16c Figure 16. Modified Filter Configuration Using a Resistor Between Summing Nodes (f–3dB = 22.7MHz) 66012f 35 LTC6601-2 APPLICATIONS INFORMATION Passband Gain vs Frequency 20 19 18 17 1.0 16 0.5 LTC6601-2 1 15 VOUT(DIFF) 49.9Ω 4 – 5 GAIN (dB) VIN(DIFF) ZIN(DIFF) = 200Ω 0.0 + 2 11 –0.5 –1.0 –1.5 –2.0 6 7 8 GAIN = 1 fO = 20.7MHz Q = 0.88 f–1dB = 20.5MHz f–3dB = 24.6MHz 9 10 –2.5 –3.0 100k 66012 F17a 40M 66012 F17b Gain Magnitude vs Frequency (Gain = 1) Passband Phase and Group Delay 5 30 PHASE 0 0 –30 –5 –60 PHASE (DEG) –10 –15 –20 –90 –120 50 40 30 –25 20 GROUP DELAY –30 GROUP DELAY (ns) GAIN (dB) 1M 10M FREQUENCY (Hz) 10 –35 100k 1M 10M FREQUENCY (Hz) 100M 66012 F17c 0 100k 5.2M 10.4M 15.6M 20.8M FREQUENCY (Hz) 0 26M 66012 F17d Figure 17. Modified Filter Configuration Using a Capacitor Between Summing Nodes (f–3dB = 24.6MHz) 66012f 36 LTC6601-2 APPLICATIONS INFORMATION DC1251A Demonstration Board The DC1251A demonstration circuit contains an LTC6601-2 (DC1251A-B). On a DC1251A the LTC6601 programming pins can be connected through 0603 resistor jumpers. In addition, optional surface mount capacitors and inductors at the LTC6601 input and/or output can be installed for additional filtering (a lowpass filter up to a 5th order can be implemented with a DC1251A demonstration circuit). The DC1251A has SMA connectors for the differential input and output of the LTC6601. An on board 106MHz lowpass RC filters the LTC6601 output. DC1251A Top Silk Screen 66012f 37 38 J2 VIN– J1 VIN+ C13 10μF 10V C6 (OPT) RZ2 C1 (OPT) RZ1 ASSY DC1251A-A DC1251A-B C14 1μF 10V RG6 RG5 RG4 C2 (OPT) RG3 RG2 RG1 U1 LTC6601CUF-1#TR LTC6601CUF-2#TR BOARD ASSEMBLY (24AWG-VIA) E2 GND E1 V+ IN 2.7V TO 5.5V (24AWG-VIA) RIN2 C4 (OPT) C3 (OPT) RIN1 C5 (OPT) V + C15 0.1μF RQ1 R4 RC3 R5 20Ω 1% (OPT) 20Ω 1% (OPT) RC2 C3 9 V– V+ OUT 4 6 5 JP1 2 3 RF7 IN– 6 RF10 SHDN LP HP V+ RF9 RF11 RF12 C4 10 OUT C8 16 RF6 IN2– C2 8 17 RF5 C7 LTC6601-2 C6 18 RF4 VOCM C1 7 C5 19 RF3 IN1– BIAS IN1+ IN2+ IN3+ 20 RF1 1 RF8 5 4 3 2 1 RF2 11 12 13 14 15 LTC6601-X Demonstration Circuit DC1251A C12 0.01μF R3 49.9Ω, 1% R2 49.9Ω, 1% C10 0.01μF V+ R1 49.9Ω, 1% C11 1000pF C9 10pF C8 10pF E4 GND (24AQG-VIA) E3 EXT VOCM (24AWG-VIA) J4 VOUT+ 66012 DC C7 10pF J3 VOUT– LTC6601-2 APPLICATIONS INFORMATION 66012f LTC6601-2 PACKAGE DESCRIPTION UF Package 20-Lead Plastic QFN (4mm × 4mm) (Reference LTC DWG # 05-08-1710) 0.70 p0.05 4.50 p 0.05 3.10 p 0.05 2.45 p 0.05 (4 SIDES) PACKAGE OUTLINE 0.25 p0.05 0.50 BSC RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS BOTTOM VIEW—EXPOSED PAD 4.00 p 0.10 (4 SIDES) R = 0.115 TYP 0.75 p 0.05 PIN 1 NOTCH R = 0.30 TYP 19 20 0.38 p 0.10 PIN 1 TOP MARK (NOTE 6) 1 2 2.45 p 0.10 (4-SIDES) (UF20) QFN 10-04 0.200 REF 0.00 – 0.05 0.25 p 0.05 0.50 BSC NOTE: 1. DRAWING IS PROPOSED TO BE MADE A JEDEC PACKAGE OUTLINE MO-220 VARIATION (WGGD-1)—TO BE APPROVED 2. DRAWING NOT TO SCALE 3. ALL DIMENSIONS ARE IN MILLIMETERS 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE 66012f Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights. 39 LTC6601-2 TYPICAL APPLICATION 5th Order, 20MHz, Lowpass Filter 20 19 18 17 16 LTC6601-2 33.2Ω 1 15 220nH* VIN(DIFF) ZIN(DIFF) = 266Ω 33.2Ω 82pF 82pF 82pF + 2 270pF VOUT(DIFF) 4 – 220nH* 5 11 *COILCRAFT 0603CS 6 7 8 9 10 66012 TA02a Passband Gain vs Frequency 1.0 0 0.5 –10 0 –20 –0.5 GAIN (dB) GAIN (dB) Gain Magnitude vs Frequency 10 –30 –1.0 –40 –1.5 –50 –2.0 –60 –2.5 –70 100k 1M 10M FREQUENCY (Hz) 100M –3.0 100k 1M FREQUENCY (Hz) 10M 66012 TA02c 66012 TA02b RELATED PARTS PART NUMBER DESCRIPTION COMMENTS LT®1568 Very Low Noise, High Frequency, Active RC, Filter Building Block Up to 10MHz Filters, SNR = 92dB, THD = –84dBc at 2MHz LT1993-2/LT1993-4/ LT1993-10 800MHz/900MHz/700MHz Low Distortion, Low Noise Differential Amplifier/ADC Driver AV = 2V/V / AV = 4V/V / AV = 10V/V, NF = 12.3dB/14.5dB/12.7dB, OIP3 = 38dBm/40dBm/40dBm at 70MHz LT1994 Low Noise, Low Distortion Fully differential Input/Output Amplifier/Driver Low Distortion, 2VP-P, 1MHz: –94dBc, 13mA, Low Noise: 3nV/√Hz LT6402-6/LT6402-12/ LT6402-20 300MHz Low Distortion, Low Noise Differential Amplifier/ ADC Driver AV = 6dB/AV = 12dB/AV = 20dB, NF = 18.6dB/15dB/12.4dB, OIP3 = 49dBm/43dBm/51dBm at 20MHz LTC6404-1 Fully Differential Amplifier, GBW = 500MHz Very Low Distortion, (2VP-P, 10MHz): –91dBc LTC6404-2 Fully Differential Amplifier, GBW = 900MHz Very Low Distortion, (2VP-P, 10MHz): –96dBc LTC6404-4 Fully Differential Amplifier, GBW = 1700MHz Very Low Distortion, (2VP-P, 10MHz): –101dBc LT6600-2.5/LT6600-5/ LT6600-10/LT6600-20 Very Low Noise, Fully Differential Amplifier and Filter 2.5MHz/5MHz/10MHz/20MHz Integrated Filter, 3V Supply, SO-8 Package LTC6601-1 Low Noise, Pin-Configurable Filter 5MHz to 27MHz Bandwidth, Second Order Differential Filter LTC6602 Dual, Matched Bandpass Filter Programmable Gain and Bandwidth for RFID Applications (40kHz to 1MHz) LTC6603 Dual, Matched Lowpass Filter Programmable Gain and Bandwidth (25kHz to 2.5MHz) LT6604-X Dual, Matched Lowpass Filter 2.5MHz, 5MHz, 10MHz and 15MHz LTC6605-X Dual, Matched Lowpass Filter 7MHz, 10MHz and 14MHz 66012f 40 Linear Technology Corporation LT 0309 • PRINTED IN USA 1630 McCarthy Blvd., Milpitas, CA 95035-7417 (408) 432-1900 ● FAX: (408) 434-0507 ● www.linear.com © LINEAR TECHNOLOGY CORPORATION 2009