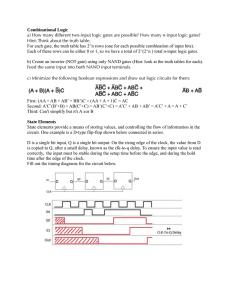

Gates, Circuits, and Computational Logic

advertisement

Chapter 2— Gates, Circuits, and Combinational Logic

2-1

Chapter 2— Gates, Circuits, and Combinational Logic

2-2

Chapter 2: Gates, Circuits, and

Combinational Logic

Analog and Digital Systems

• An analog circuit can have any value between its maximum

and minimum limits

• A digital circuit (at least in concept) has one of a fixed number

of values and changes from one value to another

instantaneously

Dr. Tim McGuire

Sam Houston State University

• Digital electronic circuits use a binary system, with two values (0

and 1)

• Ideally, if a computer runs off 5V, a 0 (false, low, off) value would

be represented by 0.0 V and 1 (true, high, on) by +5.0V

• This is TTL (which is common but being replaced by faster

and cooler devices)

• We can't unfortunately, construct devices with such

precision, so we assign ranges of values to represent 0 and 1

Based on notes by

Miles Murdocca

Chapter 2— Gates, Circuits, and Combinational Logic

2-3

Truth Tables

Assignments of Logical 0

and Logical 1 to Voltage Ranges

+5 V

• Developed in 1854 by George Boole

• Further developed by Claude Shannon (Bell Labs)

• Outputs are computed for all possible input combinations

(how many input combinations are there?

+5 V

Logical 1

Consider a room with two light switches. How must they work†?

Logical 1

2.4 V

Chapter 2— Gates, Circuits, and Combinational Logic

2-4

2.0 V

Inpu ts

Forbidden range

Forbidden range

GND

0.8 V

0.4 V

0V

Logical 0

0V

Logical 0

(a) At the output of a

logic gate

Switch A

Chapter 2— Gates, Circuits, and Combinational Logic

B

False

AND

AB

A

AB

B

XOR

OR

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

1

1

1

1

0

0

0

1

1

0

0

1

1

1

1

0

1

0

1

0

1

0

1

B

Z

0

0

0

1

0

1

1

1

0

1

1

0

show this to your electrician, or wire your house this way. This circuit

definitely violates the electric code. The practical circuit never leaves the lines

to the light "hot" when the light is turned off. Can you figure how?

Chapter 2— Gates, Circuits, and Combinational Logic

2-6

Truth Tables Showing All Possible

Functions of Two Binary Variables

A

Switch B

A

†Don't

(b) At the input to a

logic gate

2-5

Output

Light Z

“Hot”

Logic Gates and Their Symbols

Logic Gate

Symbols for

AND, OR,

Buffer, and

NOT Boolean

functions

A B

F

A B

F

0 0

0 1

0

0

0

0

0

1

0

1

1 0

1 1

0

1

1

1

0

1

1

1

A

B

F = AB

A

B

F=A+B

A ND

OR

A

B

NOR

XNOR

B

A+B

A

A+B

NAND

True

0

0

1

1

1

1

1

1

1

1

A

F

A

F

0

1

0

0

0

0

1

1

1

1

0

1

0

1

0

1

1

0

1

0

0

0

1

1

0

0

1

1

1

1

0

1

0

1

0

1

0

1

A

F =A

Buffer

• The more frequently used functions have names: AND, XOR,

OR, NOR, XNOR, and NAND. (Always use upper-case spelling.)

A

F=A

NOT (Inverter)

• Note the use of the “inversion bubble.”

• Be careful about the “nose” of the gate when drawing AND vs. OR.

Page 1

Chapter 2— Gates, Circuits, and Combinational Logic

2-7

Chapter 2— Gates, Circuits, and Combinational Logic

2-8

Variations of Basic Logic Gate

Symbols

Logic Gate Symbols for NAND, NOR, XOR,

and XNOR Boolean functions

A B

F

A B

F

0

0

1

1

1

1

1

0

0

0

1

1

1

0

0

0

0

1

0

1

A

B

0

1

0

1

A

B

F=AB

A

B

F = ABC

F=A+B

(a)

F=A+B

NAND

(b)

NOR

A B

F

A B

F

0

0

1

1

0

1

1

0

0

0

1

1

1

0

0

1

0

1

0

1

A

B

C

0

1

0

1

A

A+B

A+B

B

(c)

A

B

A

B

F=A+B

Exclusive-OR (XOR)

F=A

B

(a) 3 inputs

Exclusive-NOR (XNOR)

Chapter 2— Gates, Circuits, and Combinational Logic

2-9

Transistor Circuits

VCC

Output voltage vs. Input voltage

Vout

Vo ut– Output voltage– V

4.0

VCC

A

RL

VCC

Vout

A

Collector

Emitter

Base

Vin

A

A

3.5

VCC = 5 V

RL = 400 ?

3.0

V1

VCC

AB

A

2.5

V out

2.0

A+B

1.5

1.0

V2

0.5

0

0.2 0.4 0.6 0.8

1

1.2 1 .4 1.6 1.8

V1

B

0

GND = 0 V

(c) Complementary outputs

Chapter 2— Gates, Circuits, and Combinational Logic

2-10

The Inverter at the

Transistor Level

VCC = +5 V

(b) A negated input

2

V2

A

B

Vin– Input voltage– V

(a)

Power

terminals for

an inverter

made visible

(b)

(c)

Transistor

symbol

(d)

A transistor used

as an inverter

Inverter transfer

function

(a) A two-input NAND gate

Chapter 2— Gates, Circuits, and Combinational Logic

2-11

Chapter 2— Gates, Circuits, and Combinational Logic

2-12

The Basic Properties of Boolean

Algebra

Relationship

Dual

Property

A B = BA

A + B = B + A

Commutative

A (B + C ) = A B + AC

A + B C = (A + B )( A + C )

Distributive

1A = A

0 + A = A

Identity

AA = 0

A + A = 1

Inverse

0A = 0

1 + A = 1

Null

AA = A

A + A = A

Idempotence

A (BC ) = ( AB )C

A + ( B + C ) = (A + B ) + C

Associative

A = A

DeMorgan’s Theorem

Principle of duality:

The dual of a Boolean

function is gotten by

replacing AND with OR

and OR with AND,

constant 1s by 0s,

and 0s by 1s

Postulates

A + B = AB

D e M o r g a n ’s T h e o r e m

AB + AC + BC =

A B + AC

(A + B ) ( A + C ) ( B + C ) =

(A + B ) (A + C )

Consensus Theorem

A

B

0

0

AB = A+B

1

1

A+B

1

=

A B

1

0

1

1

1

0

0

1

0

1

1

0

0

1

1

0

0

0

0

DeMorgan’s theorem: A + B = A + B = A B

Theorems

A

B

Complement

AB = A + B

(b) A two-input NOR gate

Page 2

F=A+B

A

B

F=AB

Chapter 2— Gates, Circuits, and Combinational Logic

2-13

The Sum-of-Products (SOP) Form

Minterm

Index

A

B C

F

0

1

2

3

4

5

6

7

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

0

1

0

1

1

1

Truth Table for

the Majority

Function

0

1

0

1

0

1

0

1

The SOP Form of the Majority Gate

1

• The SOP form for the 3-input majority gate is:

00

0-side

• M = ABC + ABC + ABC + ABC = m3 + m5 +m6 +m7 = ? ?(3, 5, 6, 7)

• Each of the 2n terms are called minterms, running from 0 to 2n - 1

1-side

A balance tips to the left or

right depending on whether

there are more 0‘s or 1’s.

• Note the relationship between minterm number and Boolean value.

• Discuss: common-sense interpretation of equation.

• Transform the function into a two-level AND-OR equation

• Implement the function with an arrangement of logic gates

from the set {AND, OR, NOT}

• M is true when A = 0, B = 1, and C = 1, or when A = 1, B = 0, and

C = 1, and so on for the remaining cases.

• Represent logic equations by using the sum-of-products (SOP)

form

Chapter 2— Gates, Circuits, and Combinational Logic

2-15

B

Chapter 2— Gates, Circuits, and Combinational Logic

2-16

Four Notations Used at Circuit

Intersections

A Two-Level AND-OR Circuit

Implements the Majority Function

A

Chapter 2— Gates, Circuits, and Combinational Logic

2-14

C

ABC

Connection

No connection

Connection

No connection

ABC

F

ABC

ABC

Discuss: what is the gate count?

Chapter 2— Gates, Circuits, and Combinational Logic

2-17

Chapter 2— Gates, Circuits, and Combinational Logic

2-18

Positive and Negative

Logic Assignments

Positive versus Negative Logic

•Positive logic: truth, or assertion is represented by logic 1, higher voltage;

falsity, de- or unassertion, logic 0, is represented by lower voltage.

•Negative logic: truth, or assertion is represented by logic 0 , lower voltage;

falsity, de- or unassertion, logic 1, is represented by lower voltage

Voltage levels

A

low

low

Gate Logic: Positive vs. Negative Logic

Normal Convention: Postive Logic/Active High

Low Voltage = 0; High Voltage = 1

F

low

low

A B

0 0

0 1

F

0

0

high low

high high

low

high

1

1

0

1

A

B

Alternative Convention sometimes used: Negative Logic/Active Low

Positive logic levels

B

low

high

Physical

AND gate

F

0

1

A

B

F=AB

Negative logic levels

A B

F

1

1

0

0

1

1

1

0

1

0

1

0

A

B

F =A+ B

F

Voltage levels

Voltage T ruth T able

A

low

low

high

high

B

low

high

low

high

F

low

low

low

high

Behavior in terms

of Electrical Levels

Positive Logic

A

0

0

1

1

B

0

1

0

1

Positive logic levels

Negative logic levels

Negative Logic

F

0

0

0

1

A

1

1

0

0

B

1

0

1

0

F

1

1

1

0

A

B

Two Alternative Interpretations

Positive Logic AND

Negative Logic OR

Dual Operations

Page 3

A

B

F

low

low

high

high

low

high

low

high

high

high

high

low

Physical

NAND gate

F

A

B

A B

F

0

0

1

1

1

1

1

0

0

1

0

1

A

1

1

0

0

F=AB

A

B

B

1

0

1

0

F

0

0

0

1

F =A+ B

Chapter 2— Gates, Circuits, and Combinational Logic

2-19

Chapter 2— Gates, Circuits, and Combinational Logic

2-20

SN7400 QUADRUPLE 2-INPUT POSITIVE-NAND GATES

Digital Components

description

These devices contain four independent

2-input NAND gates.

• High-level digital circuit designs are normally made using

collections of logic gates referred to as components, rather

than using individual logic gates. The majority function can be

viewed as a component.

• Levels of integration (numbers of gates) in an integrated circuit

(IC) can be roughly considered as:

•

•

•

•

INPUTS

A

B

H

H

L

X

X

L

Simplified

Data Sheet

for 7400

NAND

gate

Small-scale integration (SSI): 10–100 gates.

Medium-scale integration (MSI): 100–1000 gates.

Large-scale integration (LSI): 1000–10,000 logic gates.

Very large scale integration (VLSI): 10,000–upward.

schematic (each gate)

VC C

package ( top view)

function table (each gate)

OUTP UT

Y

L

H

H

1A

1B

1Y

2A

2B

2Y

GND

absolute maximum ratings

Supply voltage, VCC

Input voltage:

Operating free-air temperature range:

Storage temperature range

1

14

2

13

3

12

4

11

5

10

6

9

7

8

VCC

4B

4A

4Y

3B

3A

3Y

4 k?

130 ?

1.6 k?

A

B

Y

7V

5.5 V

0°C to 70°C

– 65°C to 150°C

1 k?

GND

recommended operating conditions

MIN NOM MAX

logic diagram (positive logic)

1A

1B

2A

2B

3A

3B

4A

4B

1Y

2Y

3Y

4Y

Y = AB

V CC

Supply voltage

V IH

High-level input voltage

4.75

UNIT

5 5.25

V

2

V

V IL

Low-level input voltage

I OH

High-level output current

– 0.4

mA

I OL

Low-level output current

16

mA

TA

Operating free-air temperature

70

°C

0.8

0

V

electrical characteristics over recommended operating f ree-air temperature range

VALUE

• These levels are approximate, but the distinctions are useful in

comparing the relative complexity of circuits.

• Let us consider several useful MSI components.

OPERATING CONDITIONS

MIN

TYP

2.4

3.4

MA X

UNIT

V OH

V CC = MIN, VI L = 0.8 V, IOH = – 0.4 mA

V OL

V CC = MIN, VI H = 2 V, I OL = 16 mA

0.4

V

I IH

V CC = MA X, V I = 2.4 V

40

?A

I IL

V CC = MA X, V I = 0.4 V

– 1.6

mA

I CCH

V CC = MA X, V I = 0 V

8

mA

I CCL

V

0.2

4

V CC = MA X, V I = 4.5 V

12

mA

22

switching characteristics, V CC = 5 V, TA = 25° C

P ARAMETER

FROM (input)

TO (output)

TEST CONDITIONS

MIN NOM MAX

UNIT

tPLH

A or B

Y

R L = 400 ?

C L = 15 pF

11

22

ns

7

15

ns

tPHL

Chapter 2— Gates, Circuits, and Combinational Logic

2-21

Chapter 2— Gates, Circuits, and Combinational Logic

2-22

The Multiplexer (MUX)

An 8-1 MUX Can Implement

the Majority Function

This is a 4-to-1

Multiplexer

Data inputs

Block Diagram and Truth Table

D0

00

D1

01

D2

10

D3

11

F

A

B

F

0

0

0

1

D0

D1

1

0

D2

1

1

D3

A B

Control inputs

F = A B D0 + A B D1 + A B D2 + A B D 3

AND-OR Circuit Implementation

D0

D1

F

D2

D3

A

B C

M

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

0

1

0

1

1

1

0

1

0

1

0

1

0

1

0

000

0

001

0

010

1

011

0

100

1

101

1

110

1

111

F

A B C

A

Principle: Use the 3 MUX control inputs to select (one at a time) the 8 data inputs

B

Chapter 2— Gates, Circuits, and Combinational Logic

2-23

Chapter 2— Gates, Circuits, and Combinational Logic

2-24

The Demultiplexer Is a Decoder

with an Enable Input

The Demultiplexer (DEMUX)

F0

A Circuit for a 1-4 DEMUX

F1

Block Diagram and Truth Table

D

00

F0

01

F1

10

F2

11

F3

A B

F0 = D A B

F2 = D A B

F1 = D A B

F3 = D A B

D

D

A B

F0 F1 F2 F 3

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

1

1

0

0

0

0

1

0

0

1

0

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

0

0

0

F2

Compare to Decoder

on next slide

F3

A

B

Block Diagram and Truth Table

Enable = 1

B

D1

0

0

1

0

0

10

D2

0

1

0

1

11

D3

1

0

0

0

1

1

0

0

D0

A

01

0

B

1

Enable

D0 = A B

Page 4

Enable = 0

A

00

D1 = A B

D 0 D1 D2 D3

A

B

D0 D 1 D2 D3

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

0

0

0

0

1

1

1

0

0

0

0

D2 = A B

D3 = A B

Chapter 2— Gates, Circuits, and Combinational Logic

2-25

A 3-to-8 Decoder Used to Implement

the Majority Function

F0

F1

DEMUX

Chapter 2— Gates, Circuits, and Combinational Logic

2-26

An AND Circuit for a 2-4 Decoder

D

F2

F3

A

000

D0

001

B

D1

A

B

A

B

D2

C

010

011

M

100

101

110

D3

111

Enable

Chapter 2— Gates, Circuits, and Combinational Logic

2-27

Tri-State Buffers

C A

A

C

0

0

0

1

1

0

1

1

F

A Programmable Logic Array

C A

F

0

0

0

0

0

1

1

0

1

1

1

?

?

F=AC

or

F=?

C

Tri-state buffer

A

B

C

1

OR matrix

?

?

• A PLA is a

customizable AND

m atrix followed by a

customizable OR

m atrix

F=AC

or

F=?

A

Chapter 2— Gates, Circuits, and Combinational Logic

2-28

Tri-state buffer, inverted control

Fu ses

• There is a third state: high impedance. This means the gate

output is essentially disconnected from the circuit.

• This state is indicated by ? in the figure.

AND matrix

F0

Chapter 2— Gates, Circuits, and Combinational Logic

2-29

Simplified Representation

of a PLA

A

B

C

ABC

ABC

ABC

ABC

F0

F1

(Majo rity)

(Unused)

Page 5

F1