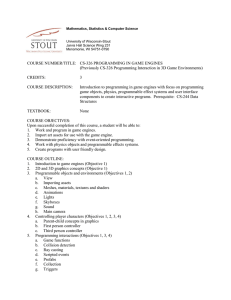

Chapter 3 Logic Gates

advertisement

ETEC 2301 Programmable Logic Devices Chapter 3 Logic Gates Shawnee State University Department of Industrial and Engineering Technologies Copyright © 2007 by Janna B. Gallaher The Inverter Input Output 0 1 1 0 Logic Symbol Truth Table Timing Diagram Inverter Operation Logic Expression The AND Gate Logic Symbol A B X 0 0 0 0 1 0 1 0 0 1 1 1 Truth Table Timing Diagram 0*0=0 0*1=0 1*0=0 1*1=1 Boolean Expression Logic Expression The OR Gate Logic Symbol A B X 0 0 0 0 1 1 1 0 1 1 1 1 Truth Table Timing Diagram 0+0=0 0+1=1 1+0=1 1+1=1 Boolean Expression Logic Expression The NAND Gate Logic Symbol A B X 0 0 1 0 1 1 1 0 1 1 1 0 Timing Diagram Truth Table Equivalent Operation A B AB = X 0 0 0*0=0=1 0 1 0*1=0=1 1 0 1*0=0=1 1 1 1*1=1=0 The NOR Gate Logic Symbol A B X 0 0 1 0 1 0 1 0 0 1 1 0 Timing Diagram Truth Table Equivalent Operation A B A+B = X 0 0 0+0=0=1 0 1 0+1=1=0 1 0 1+0=1=0 1 1 1+1=1=0 The Exclusive-OR and Exclusive-NOR Gates Logic Symbols A B X X 0 0 0 1 0 1 1 0 1 0 1 0 1 1 0 1 ExOR & ExNOR Truth Tables Timing Diagram A B A ExOR B = X A B A ExNOR B = X 0 0 0 x 0=0 0 0 0 x 0=0=1 0 1 0 x 1=1 0 1 0 x 1=1=0 1 0 1 x 0=1 1 0 1 x 0=1=0 1 1 1 x 1=0 1 1 1 x 1=0=1 Programmable Logic Large scale integrated circuit with programmable logic blocks to implement high level logic functions. Usually based on a Basic AND Array: Older styles were one-time programmable, newer technology uses flash memory. Programmable Logic (continued) Different vendors use different technologies: − Fuse Technology − Antifuse Technology − Similar to programmable read-only memories Also one-time programmable EEPROM Technology − Creates a conductive path where none exists Also one-time programmable EPROM Technology − Metal fuse that was one-time programmable Similar to programmable read-only memories Can be re-programmed SRAM Technology Uses static ram style storage Volitile memory – looses information when powered-down Programmable Logic (continued) Device Programming − Production environments use dedicated programming devices − Development environments use development boards − Designers use Integrated Development Software along with programmers and development boards Fixed-Function Logic Integrated Circuit Logic Device Families − Each family contains basic logic operations (NOT, AND, OR, NAND, NOR, EXOR, and EXNOR) − Two major families use different semiconductor technology: − TTL series – uses binary junction transistors CMOS series – uses MOS transistors CMOS 74XX and 54XX series of standard fixed-function logic (74 series = commercial grade, 54 series = military grade) Voltages: 5, 3.3, 2.5, and 1.8 volt 5 Volt logic: HC & HCT = High Speed, AC & ACT = Advanced 3.3 volt logic: LV & LVC = Low Voltage, ALVC = Advanced BiCMOS technology: hybrid CMOS and TTL logic family − 74BCTXX, 74ABTXX, 74LVTXX, and 74ALBXX series Fixed-Function Logic (continued) Integrated Circuit Logic Device Families (continued) − TTL 5 volt supply only 74XX and 54XX series devices available (74 series = commercial grade, 54 series = military grade) Several variations for speeds and power − 74 − 74S – Schottky TTL – higher speed − 74AS – Advanced Schottky TTL − 74LS – Low-power Schottky TTL − 74ALS – Advanced Low-power Schottky TTL − 74F – Fast TTL Types of Fixed-Function Logic Gates Standard Numbering System: Quad 2-input NAND 00 Dual 4-input NAND 20 Quad 2-input NOR 02 Dual 2-input AND - 21 21 HEX inverter 04 Triple 3-input NOR 27 Quad 2-input AND 08 Single 8-input NAND 30 Triple 3-input NAND 10 Quad 2 input OR 32 Triple 3-input AND 11 Quad XOR 86 Quad XNOR 266 Performance Characteristics and Parameters Propagation Delay Time (tp) DC Supply Voltage (Vcc) Power Dissipation (PD) − Input and Output Logic Levels − Product of supply voltage and average current VIH = High Level Input Voltage, VIL = Low Level Input Voltage Speed-Power Product (SPP) − Measure of the performance of a logic circuit − It is the product of the Power Dissipation and the Propagation Delay time Fan-Out and Loading − Maximum number of inputs to other gates that can be connected with reliable results.