Low-Power and Wideband LC-VCO for WiMAX in CMOS

advertisement

2014 UKSim-AMSS 16th International Conference on Computer Modelling and Simulation

Low-power and Wideband LC-VCO for WiMAX in CMOS Technology

Mohammed Aqeeli, Zhirun Hu, Xianjun Huang, Abdullah Alburaikan, Cahyo Muvianto

School of Electrical and Electronic Engineering

The University of Manchester

Manchester, UK

mohammed.aqeeli-3@postgrad.manchester.ac.uk, z.hu@manchester.ac.uk, xianjun.huang@manchester.ac.uk,

Abdullah Alburaikan@manchester.ac.uk, cahyo.muvianto@manchester.ac.uk

High-performance LC-VCOs is a major challenge and

require low-phase noise, low-loss and a wide tuning range

varactors and sophisticated current biasing source. To

achieve this object, the present work utilizes body-grounded

NMOS devices as varactors to obtain high quality factor and

better capacitance range and so better phase noise. In

addition, a newly controlled current biasing source is

designed to avoid higher power supply sensitivity and higher

up-conversion of flicker noise. Furthermore, an improve

phase noise property of VCO is achieved by implementing

Metal-Oxide-Metal (MOM) capacitors in the tank of the

VCO taking advantage of their high quality factor, high

capacitance density, low parasitic capacitance, narrow

spacing and thinner dielectric layers. This paper is organized

as follows. Section II explains the VCO’s core design and

the implementation process, while Section III presents the

implementation and the measured results, followed by the

conclusion in Section IV.

Abstract—This work presents an ultralow phase-noise and

wide turning-range voltage-controlled oscillator (VCO) for

5.72GHz WiMAX applications. The fully integrated VCO is

designed and simulated using 130-nm CMOS technology.

Instead of using the conventional diode-based varactor in the

tank design, high-performance body-grounded NMOS

transistors are employed as effective varactors. A controlled

self-biasing current source is implemented to avoid higher

power supply sensitivity and higher up-conversion of flicker

noise. The proposed VCO-measured results demonstrate a

worst case phase noise of -132.68dBc/Hz at 1MHz frequency

offset with an excellent figure of merit (FOM), which is

-201.6dBc/Hz under a power consumption of 2.21mW. The

VCO shows a tuning range of approximately 37.59%.

Keywords—CMOS; CMOS processes; Body-grounded

NMOS varactor; current source; (MOM) capacitor; figure of

merit; low phase noise.

I.

INTRODUCTION

II.

The recent exponential growth and higher integration of

wireless communication has attracted remarkable efforts to

develop more channels in mobile communication

applications. The IEEE.16 unlicensed band of Worldwide

Interoperability for Microwave Access (WIMAX), which

refers to interoperable operations of the IEEE 802.16 for

wireless-networks standards approved by the Windex Forum,

provides fixed and portable wireless broadband connectivity

independent of a base station. Three spectrum bands are

adapted for global deployment, one of which is the

unlicensed band (5.725-5.850)GHz[1]. Nowadays, the

demand for high-performance VCOs has increased, and

consequently this demand has imposed stricter requirements

on VCO phase noise. Phase noise can be triggered by a

number of conditions, but it is mostly affected by VCO

frequency stability, which is one of the most important

parameters for the quality and performance of information

transfer and in turn affects reliability in data

communication[2]. P-N junction varactors[3], body-biased

PMOS varactors[4] and switched capacitor arrays[5] are

different approaches which are used widely to increase the

bandwidth of VCOs design. Owing to the implemented

techniques, the bandwidth and the phase noise of the VCO is

substantially improved. However, PN junction present a

narrower tuning range, large power dissipation is still

unavoidable due to the stacking of body-biased PMOS

transistors and additional noise appears because of the use of

capacitor array switches.

978-1-4799-4923-6/14 $31.00 © 2014 IEEE

DOI 10.1109/UKSim.2014.79

VCO DESIGN AND IMPLEMENTATION

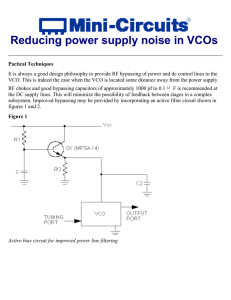

The schematic diagram and the layout of the proposed

VCO are shown in Fig. 1. The prime design considerations

for the proposed VCO aim at improving tuning range and

phase noise. For the tank circuit, body-grounded NMOS

varactors are employed instead of PMOS or common PNjunction varactors. In order to implement a wide LC-VCO

tuning range, it is important to decrease the number of

parasitic capacitors. In this design, NMOS transistors are

chosen due to the fact that parasitic capacitors in an NMOS

pair are fewer than in a PMOS pair due to the smaller

transistor size. Therefore, for the same value of gm, the W/L

of an NMOS cross-couple is approximately one-third of a

PMOS cross-couple. Also importantly, the proposed design

utilizes a direct bias current source rather than the

conventional mirrored bias current. The bias current of the

VCO, which is an important parameter for phase noise

optimization, is designed to handle the maximum current

allowed by the specifications.

A. Body-grounded NMOS varactor in 130nm CMOS

Implementing (VCOs) in standard complementary metal

oxide semiconductor (CMOS) technology is a major

challenge for the design of radio-frequency (RF) transceiver

integrated circuits (ICs). MOS devices in VCOs can produce

wider tuning range, better Q and lower phase noise than

diode varactors.

552

This new varactor mode is referred to as body-grounded

NMOS varactor. Since the tuning voltage and the common

mode point are both Vdd referred, supply noise is not coupled

into the tank by the varactor back gate capacitance and the

VCO has excellent supply. The current biasing source,

maintain a constant large signal tank swing across NMOS

varactors, thereby producing a constant common mode point

from a constant current into a constant tank resonate

impedance[6]. In the proposed body-grounded varactor, four

pairs of symmetrical NMOS varactors are formed with 64

gate fingers. If the voltage VGS<VTH, an inversion zone is

established. The minimum value Cmin is reached when the

voltage difference between electrodes is equal to the

threshold voltage VTH. The maximum capacitance value per

unit of area, Cmax is equal to ο/tox which corresponds to a

high accumulation value under the gate oxide. The tuning

range is defined by the ratio between Cmin and Cmax.

According to the Cadence virtuoso analogue simulation

results, each pair of varactors alters capacitance from 0.25 to

0.70 pF as tuning voltage varies from 0 to 2.5V.

C. Self-biasing current source

A new controlled current source is designed specifically

for the proposed VCO to achieve optimal phase noise and

well-balanced differential outputs but with less power

consumption. The tail current reference source is designed

to generate current independently of the supply voltage

because of the high impedance element which has the ability

to overcome any possible variations. The current mirror is

formed by PMOS transistors (M3, M6) developing current

in the two branches of the circuit. The start-up circuit is

used to inject current and to move the current source from

the zero condition to the point of operation. By adjusting

resistor R1, the circuit will generate the suitable current for

the VCO. This current source is optimized properly to

reduce swing and as a result decrease phase noise even

more, in which case the circuit consumes less than 150 ȝA.

To sustain the oscillation, the higher the gm must be,

(a)

(b)

Figure1 (a) Schematic diagram (b) Layout of the designed 5.2 GHz 130nm

CMOS VCO.

gm ≥

B. Body-grounded NMOS varactor in 130nm CMOS

Implementing (VCOs) in standard complementary metal

oxide semiconductor (CMOS) technology is a major

challenge for the design of radio-frequency (RF)

transceiver integrated circuits (ICs). MOS devices in VCOs

can produce wider tuning range, better Q and lower phase

noise than diode varactors. The two most important types

used for VCOs application are the PMOS and NMOS

varactors.A PMOS varactor is mediated between the source

of the PMOS transistor and a power supply, while an

NMOS varactor is mediated between the source of the

NMOS transistor and ground.

An improved four parallel NMOS varactor for the

proposed LC-tank VCO applications is implemented in this

work by connecting the NMOS varactor fourth terminal BG

to a ground-isolated common mode point of the negative

transconductance (gm) devices used to pump the VCO tank.

RC

L

(1)

The minimum biasing current, Ibias=2ID is inversely

proportional to the transconducance efficiency and the

inductance value and its quality therefore:

I bias ≥

2

§ gm ·

¨

¸ .QL .ω0

© ID ¹

(2)

Taking into consideration all of the parasitic mostly

associated with the tank of the VCO’s, the frequency of

oscillation can be derived as:

ω0 =

553

2

R 2 (C + C gs + 4C gd 0 )

1

2 1−

L

L(C + C gs + 4C gd 0 )

(3)

2

I bias ≥

§ gm

¨

© ID

·

¸ .QL .

¹

L − R ( C + Cgs + 4C gd 0 )

2

(C + C

gs

≈ 1.84mA

+ 4Cgd 0 )

E. MOM capacitors

VCOs depend only on technology-dependent factors, in

other words on the Q of inductor(s) and capacitors[2].

Integrated inductance-capacitances (LCs) are standard

components in LC tank VCO circuits and may become the

most important part of a high-performance VCO circuit

design. VCOs use various types of integrated capacitors

utilizing MOS, p-n junctions, MIM (metal-insulator-metal),

poly-to-poly, MOM and other structures. MOM capacitors

are one of the most widely used, due to their high

capacitance density, low parasitic capacitance, symmetrical

plate design, superior RF characteristics and no additional

masks or process steps – and thus low cost.

In symmetric-type MOM structures, the architecture

consists of two ports, and the number of fingers per layer is

limited to even numbers, in order to maintain symmetry.

There are six metal layers, finger length (Lf) is 12 and the

area is 424.36ȝm2. Fig.3 illustrates simulated frequency

dependent quality factor of MOM capacitor designed with a

130nm CMOS process technology[2].

(4)

In this work we can calculate the minimum required

biasing current from (4). From this equation it can be seen

clearly that transistor capacitance C requires a decrease in

the C value compared with the ideal case for a given

resonant frequency[2]. This equation establishes the

importance of MOSFET size, and the result is that the

bigger it is, the higher the gm must be to achieve oscillation.

D. Center taped inductor

The proposed inductors turned out to be near optimum

for the oscillator design goal of reducing the internal series

resistor. Relatively small L and high Q inductor values are

key to a high-performance, low-power and low-noise

oscillator. In this work, the designed inductor is a

symmetrical center-tapped inductor, taken into consideration

by obtaining the maximum Q factor at 5.72 GHz[2]. It was

simulated at different frequencies, as shown in Fig. 2, and

the measured quality factor Q was 18.10 for 359 pH

inductors, while the area was 15190 ȝm2. For the planner

inductor, value L can be given approximately by[6]:

(5)

60

50

40

30

20

The total length of the winding (l) is:

l = (4n + 1)r + 9( N + 1) N ( w + s )

Frequency - Quality factor

70

Quality factor

μ § §

··

l

+ 0.2 ¸¸ ¸¸

L = 0 .l.¨¨ ln ¨¨

2π © © n (t + w)

¹¹

80

10

0

(6)

2

4

6

Frequency(GHz)

8

10

Figure 3. Characteristics of a MOM capacitor designed with 130nm CMOS

process technology.

where s is winding spacing, t is the thickness of the material,

n is the winding count, w is the winding width, N= integer

(n), ı is the conductivity of the interconnect, į is skin depth

and μ 0 is magnetic permeability.

III. SIMULATION RESULTS

The demonstrated VCO generates stable periodic signals

with a harmonic index and measured output power of

5.73dBm at the resonance frequency, as shown in Fig. 4.

20

V/Vout:pss dB20

5.7201GHz

5.73823dB

Harmonics(dB)

0

-20

V/Vout:pss dB20

10.40286GHz

-37.39623dB

-40

-60

-80

-100

0

2

4

6

8

10 12 14 16 18 20 22

Frequency(GHz)

Figure 2. Inductor quality and SRF versus L values in 130nm CMOS

process technology

Figure 4. Simulated power output plot of a 5.72 GHz VCO

554

By implementing body-grounded NMOS varactors, the

VCO can significantly increase the tuning range from (4.625.68)GHz to (4.63-6.78)GHz. This provides up to 19.23%

better performance than the conventional NMOS varactors

and approximately 12% better than the body-biased PMOS

varactors as shown in Fig.5, with tuning voltage varying

from 0 to 2.5 V. The solid and the dotted lines represent

simulation results using NMOS varactors with and without

body-grounding.

7.0

­f ½

­ Pd ½

FOM = L{Δf }− 20 log ® 0 ¾ + 10 log ®

¾

Δ

f

¯1mW ¿

¯ ¿

0

Phase noise(dBc/Hz)

6.0

5.5

5.0

4.5

4.0

0.0

0.5

1.0

1.5

2.0

Tuning voltage(V)

2.5

-20

-40

-60

-80

-100

-120

-140

-160

1.0

Figure 5. Output frequency of the designed VCO

Phase noise: -132.6805dBc/Hz

10.0

100.0

10K

100K

0.1M 1.0M

Reative frequency (Hz)

Generally, random FM walk noise is an enduring

component in oscillator phase noise [6]. This component

seems to be unnoticeable because the component,

which

is up-converted from the flicker noise in active

devices and current sources, significantly outweighs random

FM walk noise. However, since the proposed circuit design

can reduce flicker noise in MOSFETs, FM flicker noise is

kept to a minimum. The phase noise of an LC-VCO is

described, according to Leeson, as [7]

ª 1 § § f · 2 ·§ f

·§ FKT

0

¸ + 1¸¨¨ c + 1¸¸¨¨

L( f m ) = 10 log f « ¨ ¨¨

¸© f m

« 2 ¨© © 2 f m Q1 ¸¹

¹© ps

¹

¬

·º

¸¸ »

¹ »¼

Figure 6. Simulated phase noise at 1 MHz offset.

(7)

Fig. 6 shows the phase noise measurement results at 5.72

GHz, for which the SSB phase noise measured at 1 MHz

offset from the carrier frequency were -132.68dBc/Hz. By

using a 1.2 V supply voltage, the total power consumption of

TABLE I.

(8)

Fig.7 depicts the curves of the oscillation frequency and

FOM versus the controlled voltage from the simulation.

Simulated tuning range(body-grounded NMOS)

(body- biased NMOS)

(body-biased PMOS)

6.5

Frequency(GHz)

the VCO core is 2.21 mW. To compare the performance of

previously published oscillators and the FOM, we used the

model adopted by Ham and Hajimiri[8], which normalizes the

measured phase noise with respect to center frequency and

power consumption. It is defined by equation (8):

Figure 7. Tuning characteristics and FOM of the VCO.

PERFORMANCE COMPARISON OF CMOS VCOS

Process

F (GHz)

P (mW)

PN(dBc/Hz)

Offset

TR(GHz)

FOM(dBc/Hz)

Ref.

0.09µmCMOS

0.18µmCMOS

0.18µmCMOS

0.18µmCMOS

0.18µmCMOS

0.25µmCMOS

0.18µmCMOS

0.09µmCMOS

0.13µmCMOS

5.63

5.20

6.00

5.80

5.10

4.77

6.98

3.95

5.72

14.00

9.70

12.50

10.08

9.70

18.18

3.40

6.60

2.21

-108.50

-113.70

-115,50

-117.00

-122.40

-122.10

-108.10

-147.00

-132.68

1.0

1.0

1.0

1.0

1.0

1.0

1.0

10.0

1.0

4.50-7.10

4.39-5.26

5.72-6.02

5.27-6.41

4.80-5.40

3.60-4.77

6.54-6.98

3.40-4.50

4.63-6.78

-172.00

-180.00

-179.80

-184.00

-152.00

-184.90

-180.00

-191.00

-201.60

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

F: Frequency, P: power, PN: Phase noise, TR: Tuning range, FOM: Figure of Merit.

555

This work

Table I summarizes measured performance, where the figure

of merits with tuning range is used for comparison between

this work and other state-of-the-art CMOS applications.

Phase noise automatically decreases, while power

consumption is reduced; thus, there is a trade-off between

power consumption and phase noise[6].

[7]

[8]

[9]

IV. CONCLUSIONS

A general design methodology for low-power and

wideband LC-VCO with body-grounded NMOS varactors is

proposed to reduce the flicker noise, and meanwhile increase

the tuning range. Moreover, the self-biasing current source

circuit avoids two major disadvantages; higher power supply

sensitivity and higher up-conversion of flicker noise. It is

shown that optimization will yield a trade-off between phase

noise and power consumption. As proof of the concept, the

overall measured worst-case phase noise was -132.68dBc/Hz

at a 1 MHz frequency offset, approximately over the whole

working band. As a result, this CMOS VCO achieves a best

FOM of -201.60dB. The VCO shows an approximate

37.59% tuning range. The VCO is tuned from (4.63-6.78)

GHz with a tuning voltage varying from 0 to 2.50 V and a

power dissipation of only 2.21 mW. Importantly, the

proposed NMOS VCO design demonstrates very low phase

noise and approximately fixed values at all tuning range due

to the high quality LC-tank components and the direct bias

current source

[10]

[11]

[12]

[13]

[14]

[15]

ACKNOWLEDGMENT

[16]

The authors would like to thank Prof. Zhipeng Wu and

Prof. Ali Rezazadeh, for all their help and support.

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

H. Labiod, Wi-Fi, Bluetooth, Zigbee and WiMAX / by H. Labiod, H.

Afifi, C. De Santis. Dordrecht: Dordrecht: Springer, 2007.

M. Aqeeli, Zhirun Hu, Cahyo Muvianto, “A 6.72GHz Low-PhaseNoise Voltage Controlled Oscillator Adopting Metal-Oxide-Metal

Capacitors Using 130nm CMOS Technology” the 2013 Fifth

International

Conference

on

Computational

Intelligence,

Communication Systems and Networks, pp.101 – 106, 2013.

M. Dousti, F. Temcamani, J. Gautierassoud, “A Fully Differential

Low Phase Noise and Extra Linear VCO Design in SiGe BiCMOS

Technology,” 3rd International Conference on Information and

Communication Technologies, 2008.

D. Cordeau, J-M. Paillot, L.A. Dascalescu, “5-GHz fully integrated

full PMOS low-phase-noise LC VCO,” IEEE Journal of Solid-State

Circuits, vol. 40, pp. 2087 – 2091, 2005.

X. Tang, F. Huang, M. Shao, Y. Zhang “A wideband 0.13ȝm CMOS

LC-VCO for IMT-Advanced and UWB applications,” IEEE MTT-S

International Microwave Workshop Series on Millimeter Wave

Wireless Technology and Applications (IMWS), 2012.

Marc Tieboud, “Low power VCO design in CMOS,” Berlin,

Heidelberg, Netherlands: Springer, 2006.

556

D. B. Lesson, “A simple model of feedback oscillator noise

spectrum,” Proceedings of the IEEE, vol. 54, no. 2, Feb. 1966.

D. Ham and A. Hajimiri, “Concepts and methods in optimization of

integrated LC VCOs,” IEEE Journal of Solid-State Circuits, vol. 36,

no. 6, pp. 896–909, 2001.

B. Soltanian, H. Ainspan, R. Woogeun, D. Friedman, and P. Kinget,

“An Ultra Compact Differentially Tuned 6 GHz CMOS LC VCO

with Dynamic Common-Mode Feedback,” IEEE Circuits Conference

in Custom Integrated, CICC ’06, pp. 671-674, 2006.

M. Young-Jin, R. Yong-Seong, J. Chan-Young, and Y. Changsik, “A

4. 39&5.26 GHz LC tank CMOS Voltage-Controlled Oscillator With

Small VCO-Gain Variation,” Microwave and Wireless Components

Letters, IEEE, vol. 19, pp. 524-526, 2009.

J. Lin, C. Yeung Bun, and Y. Wooi-Gan, “A 5.8-GHz VCO with

Precision Gain Control,” (RFIC) IEEE Symposium in Radio

Frequency Integrated Circuits (RFIC), pp. 701-704, 2007.

G. Chao, H. Jun, Z. Siheng, S. Houjun, and L. Xin, “A 5-GHz lowphase-noise CMOS LC-VCO for China ETC applications,” in

Microwave Technology & Computational Electromagnetics

(ICMTCE), 2011 IEEE International Conference on, pp. 267-269,

2011.

P. Ruippo, T. A. Lehtonen, and N. T. Tchamov, “An UMTS and

GSM Low Phase Noise Inductively Tuned LC VCO,” Microwave and

Wireless Components Letters, IEEE, vol. 20, pp. 163-165, 2010.

B. Catli and M. M. Hella, “A 1.94 to 2.55 GHz, 3.6 to 4.77 GHz

Tunable CMOS VCO Based on Double-Tuned, Double-Driven

Coupled Resonators,” IEEE Journal of Solid-State Circuits, vol. 44,

pp. 2463-2477, 2009.

L. Jianing, Z. Jun, G. Yuanlin, and L. Huihua, “A ultra-low-voltage

6.9 GHz CMOS quadrature VCO with superharmonic and back-gate

coupling,” The International Workshop in Microwave and Millimeter

Wave Circuits and System Technology (MMWCST), 2012.

L. Fanori and P. Andreani, “Highly Efficient Class-C CMOS VCOs,

Including a Comparison With Class-B VCOs,” IEEE Journal of

Solid-State Circuits, vol. 48, pp. 1730-1740, 2013.