5. Low-Power OpAmps

advertisement

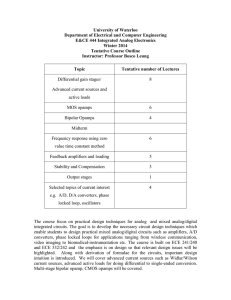

5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 5. Low-Power OpAmps Francesc Serra Graells francesc.serra.graells@uab.cat Departament de Microelectrònica i Sistemes Electrònics Universitat Autònoma de Barcelona paco.serra@imb-cnm.csic.es Integrated Circuits and Systems IMB-CNM(CSIC) Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 1 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 1 Low-Voltage vs Low-Current 2 Subthreshold Operation 3 Class-AB Output Stages 4 Rail-to-Rail Topologies 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 2 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 1 Low-Voltage vs Low-Current 2 Subthreshold Operation 3 Class-AB Output Stages 4 Rail-to-Rail Topologies 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 3 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Low-Voltage vs Low-Current OpAmp overall power consumption: Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 4 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Low-Voltage vs Low-Current OpAmp overall power consumption: Alternative supply sources (battery, solar cell, scavenging) Poor power scaling Limited by technology Low-voltage circuit techniques: Rail-to-rail Inverter-based Supply multipliers Back gate ... Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 5 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Low-Voltage vs Low-Current OpAmp overall power consumption: Alternative supply sources (battery, solar cell, scavenging) Poor power scaling Limited by technology Low-voltage circuit techniques: Rail-to-rail Strong power savings Limited by noise and bandwidth Inverter-based Supply multipliers Back gate ... Low-current circuit techniques: Subthreshold Class-AB Dynamic biasing Duty cycle ... Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 6 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Low-Voltage vs Low-Current OpAmp overall power consumption: Alternative supply sources (battery, solar cell, scavenging) Poor power scaling Limited by technology Low-voltage circuit techniques: Rail-to-rail Strong power savings Limited by noise and bandwidth Inverter-based Supply multipliers Back gate ... Low-current circuit techniques: Subthreshold Class-AB Dynamic biasing Duty cycle ... Conflicts can arise between low-current and low-voltage design techniques! Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 7 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 1 Low-Voltage vs Low-Current 2 Subthreshold Operation 3 Class-AB Output Stages 4 Rail-to-Rail Topologies 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 8 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Optimizing MOSFET Biasing Each transistor has its own purpose and requirements! M7 M8 M1 e.g. single-ended two-stage Miller OpAmp M3 M5 M2 M4 M6 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 9 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Optimizing MOSFET Biasing Each transistor has its own purpose and requirements! M7 M8 M1 e.g. single-ended two-stage Miller OpAmp M3 M5 M2 M4 M6 good current matching Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 10 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Optimizing MOSFET Biasing Each transistor has its own purpose and requirements! M7 M8 M1 e.g. single-ended two-stage Miller OpAmp M3 good current matching M5 M2 M4 M6 good transconductance Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 11 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 12 /43 Optimizing MOSFET Biasing Forward saturation example (neglecting CLM): Each transistor has its own purpose and requirements! M7 M8 M1 e.g. single-ended two-stage Miller OpAmp M3 good current matching M5 Moderate Weak M2 M4 Strong inversion M6 Leakage good transconductance Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Optimizing MOSFET Biasing Each transistor has its own purpose and requirements! M7 M8 M1 e.g. single-ended two-stage Miller OpAmp M3 good current matching Individual operating point selection by sizing + biasing: M5 inversion coefficient M2 M4 M6 good transconductance IC-based circuit design: IC>>1 e.g. good current matching IC~1 optimized transconductance/power IC<<1 e.g. translinear ex functions Strong inversion Weak Design of Analog and Mixed Integrated Circuits and Systems Moderate F. Serra Graells 13 /43 Intro 5. Low-Power OpAmps Subthreshold Specific Current Generator IS-based current reference: IS-based current M5 M M6 N Vbias M7 1 Rail-to-Rail Inverter-Based proportional to absolute temperature (PTAT) Neglecting CLM PTAT voltage M4 1 M3 1 Ibias MIbias Class-AB Ibias M1 P M2 1 Vptat weak inversion sat. strong inversion sat. strong inversion cond. By using Ibias for biasing circuits, IC selection is independent from technology http://dx.doi.org/10.1109/JSSC.2002.806258 F. Serra-Graells et al., Sub-1V CMOS Proportional-To-Absolute-Temperature References, IEEE Journal of Solid-State Circuits, 38:1(84-8), Jan 2003 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 14 /43 Intro 5. Low-Power OpAmps Subthreshold Class-AB Rail-to-Rail Inverter-Based Specific Current Generator IS-based current reference: thermal compensated voltage M8 X M5 M XIbias Vref IS-based current M9 Y Vbias PTAT voltage M4 1 M3 1 Ibias MIbias M6 N M7 1 As a side effect, temperature compensated voltage references can be also obtained: Ibias M1 P M2 1 Vptat weak inversion sat. strong inversion sat. strong inversion cond. By using Ibias for biasing circuits, IC selection is independent from technology http://dx.doi.org/10.1109/JSSC.2002.806258 F. Serra-Graells et al., Sub-1V CMOS Proportional-To-Absolute-Temperature References, IEEE Journal of Solid-State Circuits, 38:1(84-8), Jan 2003 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 15 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 1 Low-Voltage vs Low-Current 2 Subthreshold Operation 3 Class-AB Output Stages 4 Rail-to-Rail Topologies 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 16 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Output Operation Class OpAmp power investment: noise performance driving capability Output stage operation modes: Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 17 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Output Operation Class OpAmp power investment: Class-A noise performance Class-B driving capability Output stage operation modes: Class-G/H Class-E/F Design of Analog and Mixed Integrated Circuits and Systems Class-C Class-AB Class-D F. Serra Graells 18 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Basic CMOS Topologies Inverter-like stage: MP Push-pull type stage: Class-AB modulation index MN MN MP MN and MP static bias current Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 19 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 20 /43 Basic CMOS Topologies Inverter-like stage: MP Push-pull type stage: Class-AB modulation index MN MN High voltage gain MP MN and MP static bias current Unity voltage gain Intrinsic high output impedance (1/gmd) Intrinsic low output impedance (1/gms) Suitable for capacitive loads only Suitable for any type of load impedance Optimized full-scale Reduced full-scale Biasing circuitry to control Ibias against PVT (CMOS process, supply voltage and temperature) corners and to reach high Class-AB m-values? Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Class-AB Stage Examples Translinear loops: M1 M2 M4 M3 M5 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 21 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Class-AB Stage Examples Translinear loops: weak inversion sat. strong inversion sat. M1 M2 CCW CW M4 M3 M5 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 22 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Class-AB Stage Examples Translinear loops: weak inversion sat. strong inversion sat. M1 M2 CCW CW M4 M8 M7 M3 M5 High supply voltage typically required... M1 M2 M3 M4 M5 M6 M9 Design of Analog and Mixed Integrated Circuits and Systems inverter based version M10 F. Serra Graells 23 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Class-AB Stage Examples Class-A + dynamic biasing: M3 M2 M1 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 24 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Class-AB Stage Examples Class-A + dynamic biasing: discrete time (e.g. SC OpAmps) M3 M2 AC response continuous time (e.g. RC OpAmps) high value M1 M2 M3 M2 M1 Area overhead Noise excess from biasing DC response Design of Analog and Mixed Integrated Circuits and Systems M1 F. Serra Graells 25 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Class-AB Stage Examples Telescopic topologies: Asymmetrical differential pairs M6 M4 M2 M1 Output range M1 M2 M1 Classic differential pair M5 M3 M2 Constant voltage bias so M3 PVT compensated by symmetry... Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 26 /43 5. Low-Power OpAmps Intro Class-AB Stage Examples Telescopic topologies: Asymmetrical differential pairs Subthreshold Class-AB Rail-to-Rail Inverter-Based Half-circuit analysis for strong inversion saturation M6 M5 M4 M2 M1 Full-circuit analysis for M1=M2 Classic diff. pair M3 Output range Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 27 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 1 Low-Voltage vs Low-Current 2 Subthreshold Operation 3 Class-AB Output Stages 4 Rail-to-Rail Topologies 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 28 /43 Intro 5. Low-Power OpAmps Subthreshold Class-AB Rail-to-Rail Inverter-Based Why Rail-to-Rail? Optimization of signal full-scale (VFS) and probably dynamic range (DR) Necessary at OpAmp input? Compatibility with low supply voltages (e.g. battery-powered, energy scavenging) Required by CMFB in fully differential signal processing Already available at OpAmp output when no cascode is used: inverter-like stage MP Required for certain feedback configurations! MN Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 29 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based OpAmp Input Transconductance Overall gain performance: input transconductance output resistance Input transconductor for rial-to-rail? NMOS differential pair PMOS differential pair Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 30 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based OpAmp Input Transconductance Complementary differential pair Overall gain performance: input transconductance output resistance Input transconductor for rial-to-rail? NMOS differential pair PMOS differential pair Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 31 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based OpAmp Input Transconductance Complementary differential pair Overall gain performance: input transconductance output resistance Non-constant transconductance (gain): NMOS N+PMOS PMOS Design of Analog and Mixed Integrated Circuits and Systems Specific OpAmp biasing techniques are required for rail-to-rail complementary differential pairs F. Serra Graells 32 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 3-Times Current Mirror Complementary differential pair raw input transconductance: Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 33 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 3-Times Current Mirror Complementary differential pair raw input transconductance: Equalization in strong inversion: Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 34 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 3-Times Current Mirror Equalization in strong inversion: 1 Design of Analog and Mixed Integrated Circuits and Systems 3 F. Serra Graells 35 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 3-Times Current Mirror Equalization in strong inversion: 3 not truly on/off operation 1 1 3 Compact bias control Non-exact solution Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 36 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 37 /43 Current Switch Equalization in weak inversion: Compact bias control Transconductance equalization sensitivity to reference voltage Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 1 Low-Voltage vs Low-Current 2 Subthreshold Operation 3 Class-AB Output Stages 4 Rail-to-Rail Topologies 5 Inverter-Based Pseudo-Differential Multi-Stages Architectures Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 38 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Cascade vs Cascode Low supply voltage by avoiding cascoding circuit structures cascode amplifier M2 M1 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 39 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Cascade vs Cascode Low supply voltage by avoiding cascoding circuit structures OpAmp gain drop may be compensated by multistage topologies cascode amplifier M2 M1 Increase in power consumption Multipole frequency compensation can be tricky! inverter amplifier M1 M2 Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 40 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 3-Stage Nested Miller OTA Inverter as transconductance basic building block M1 Design of Analog and Mixed Integrated Circuits and Systems M2 F. Serra Graells M3 41 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based 3-Stage Nested Miller OTA Inverter as transconductance basic building block Phase margin save design M1 M2 M3 10 9 8 7 6 5 4 3 Increase in power consumption 2 1 0 0 1 2 3 4 5 6 7 8 9 10 Bandwidth reduction Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 42 /43 5. Low-Power OpAmps Intro Subthreshold Class-AB Rail-to-Rail Inverter-Based Nested Gm-C Compensation Combination of nested loops involving: Pseudo-differential structures: Positive/negative transconductors Miller compensation capacitors e.g. 3-stage OTA Design of Analog and Mixed Integrated Circuits and Systems F. Serra Graells 43 /43