C - TUKE

advertisement

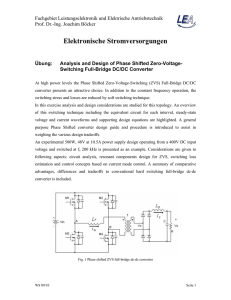

SCYR 2010 - 10th Scientific Conference of Young Researchers – FEI TU of Košice Novel Zero–Voltage and Zero–Current Switching Full-Bridge PWM Converter Using Simple Secondary Active Clamp Circuit 1 1 Ján PERDUĽAK, 2Marcel BODOR Dept. of Electrical Engineering, Mechatronics and Industrial Engineering, FEI TU of Košice, Slovak Republic 1 jan.perdulak@student.tuke.sk, 2marcel.bodor@tuke.sk Abstract —A novel zero-voltage and zero-current switching (ZVZCS) full-bridge phase shifted pulse-width modulation converter is presented in this paper. A simple auxiliary secondary circuit is used on the secondary side consist of capacitor, inductance, two rectifier diodes and unipolar MOSFET transistor, provides conditions for ZVZCS – soft switching of IGBT transistor on the primary side of the DC/DC converter. The turning off the MOSFET transistor located on the secondary side provides reset both secondary and primary current and thus the conditions for ZVZCS is achieved. This paper presents detail theoretical analysis and experimental results. The appropriateness of using the proposed new topology diagram for high power application is confirmed. Keywords— phase-shifted PWM, power converter, insulated gate bipolar transistor, soft switching,. I. INTRODUCTION Recently, the increasing demands for high performance load converters in power electronics are present. It also places great emphasis on increasing the switching frequency for reducing size and weight of the converters. However with increasing frequency the increasing switching losses occur mainly on the switching devices such as transistors. The power MOSFETs have many advantages such as very short switching times. It is one of the reasons why these switching devices are mainly used in ZCZVS FB PWM converters. However the MOSFETs are not suitable for high power applications. These days, IGBTs are replacing MOSFETs for high voltage, high power applications, since IGBTs have higher voltage rating, higher power density, and lower cost compared to MOSFETs [1]. On the other hand, the use of IGBTs is significantly reduced by their frequency switching, usually limited to 20 – 30 kHz because of their tail current characteristic [2]. To operate IGBTs at higher switching frequencies is required to significantly reduce turn – off switching losses. Many topologies have been developed to solve this problem [1] – [5]. This topology used auxiliary circuit on the secondary side to achieve ZCZVS and therefore to reduce the switching loss to zero. Generally the ZVS of the leading-leg switched is achieved by the similar manner as that of the ZVS FB PWM converters [3] – [4], [6] whereas ZCS of lagging-leg switches is achieved by resetting the primary current during the freewheeling period. The technical realization of auxiliary circuit which provides reset of primary current is realized in different ways. The converter proposed in [3] has simple auxiliary circuit which contains neither loss components nor active switches. Resetting of the primary current is achieved by using energy of leakage inductance and clamp capacitor placed on the secondary side. The converter [2] same as converter [3] contains neither loss components nor active switches. Resetting of the primary current is achieved using transformer auxiliary winding inserted into the secondary side what makes this auxiliary circuit more complex. The converter [7] contains active switch on the secondary side. This switch is used to control the clamping circuit. The clamp switch induces switching loss due to its hard switching, and the maximum output current is limited by the capacitance of holding capacitor [3]. The blocking capacitor on the primary side of the transformer winding is used in the converter [5]. The auxiliary circuit contains active switch and transformer auxiliary winding which make this circuit considerably complex and parameter design is complicated [2]. II. OPERATION PRINCIPLE The detail description of proposed converter is in [6]. This operation principle description below is abbreviated form of description in [6]. The proposed converter (Fig.1) has nine operating modes within each operating half cycle. The equivalent circuits and the corresponding operation waveforms are show in Fig.2 and Fig.3, respectively. Mode1- interval (t0–t1): The transistors T1, T2 are turned on with ZVS at t0 because only magnetizing current flows through diodes D1, D2. The collector current of the transistor TS, which is turned on at t0 too, starts to flow and the capacitor CC is discharged. The rise of the collector current is in resonant way with the resonant frequency ωR1 different at no-load and short circuit in a range: ( L0 + LCS ). C 0 .C C ≤ ω R1 ≤ C 0 + CC (L0 + LCS ).CC (1) SCYR 2010 - 10th Scientific Conference of Young Researchers – FEI TU of Košice T1 T3 During the commutation the energy stored in the leakage inductance is transferred to the clamp capacitor CC and consequently an over-voltage ∆US appears on secondary voltage. T2 Mode7- interval (t6–t7): Only small magnetizing current im flows through primary winding of transformer. The output current flows trough output freewheeling diode D0. D3 D1 Up TR U D5 T4 D6 D2 D4 - L0 D0 LS C0 R DS DC CC TS Clamp circuit Mode8 - interval (t7–t8): In this interval the transistors T1 and T2 are turned off with ZCS. Only small magnetizing current im is switched off by transistors T1 and T2. The magnetizing current charges or discharges the internal output capacitances COSS1 – COSS4 of the IBGT transistors T1 – T4 respectively. Mode9 - interval (t8–t9): At t8 the freewheeling diodes D3, D4 starts to lead primary current and thus conditions for the ZVS for the transistors T3 and T4 are set up. Fig.1. Circuit topology of the proposed converted Mode2-interval (t1–t2): The transformer leakage inductance LLP reflected to the primary side causes that primary current iP is linearly increased with the slope U/LLP while the secondary voltage uS is zero as a result of commutation between output freewheeling diode D0 and rectifier diode D5. T1 D1 Coss3 Coss1 T3 D3 T1 D1 T3 Coss3 Coss1 Up U U Coss4 T4 D5 D6 Coss2 D4 Coss4 T2 D2 - T4 L0 MODE1 D0 LS C0 D5 D6 DC D1 L0 MODE2 R T1 D3 D1 Coss3 Coss1 D6 Coss2 D4 Coss4 T2 D2 - T4 L0 D0 LS Mode5-interval (t4–t5): The primary current increases with the slope: CC T1 dt U − n.U 0 U + 2 LLP + n .L0 Lm D5 D6 C0 D1 Coss1 L0 DC Coss3 TS CC T3 D3 T1 D5 D6 D1 Coss2 T4 (5) T3 D3 D0 LS C0 L0 C0 R DS DC DC TS CC TS CC T3 Coss3 Coss1 D0 LS MODE7 R DS D1 T2 D2 - T1 D3 D1 T3 Coss3 Coss1 D3 Up U , for R0 = 0 . TS D6 Coss2 D5 D4 Up ω R 2 = ( L0 + LLS ).C C DC Coss3 Coss1 Coss4 T2 D2 L0 T1 (4) R Up D4 MODE6 C 0 .C C , for R0 = ∞. C0 + CC C0 U Coss4 T4 N Where n = P is power transformer turns ratio and Lm NS ω R 2 = ( L0 + LLS ). D0 LS DS - Mode6: interval (t5–t6): At t5 the secondary transistor TS turns off. At that time the commutation between transistor TS and clamp diode DC occurs and charging of the clamp capacitor CC starts. Afterwards the commutation between DC, D5 and output freewheeling diode D0 starts. In the mentioned commutation path the resonance occurs and rise of the current depends on the resonant frequency ωR2: T2 D2 MODE5 R U magnetizing inductance of the power transformer. T3 D3 Coss2 D4 Up (3) TS - DS = R U D5 MODE3-4 di p C0 Up U Coss4 (2) DC CC Up T4 i0 = i S + i LS D0 LS TS T3 Coss3 Coss1 T2 D2 DS CC T1 Coss2 D4 - DS Mode4-interval (t3–t4): Transistors T1 and T2 are conducting and the energy is delivered from the source to the load. The smoothing inductance current is a sum of the secondary current and inductance LS current: D3 Up U Coss4 T4 D5 D6 Coss2 D4 Coss4 T2 D2 - T4 L0 MODE8 D0 LS C0 DS D6 Coss2 R T2 D2 L0 MODE9 D0 LS C0 R DS DC CC D5 D4 - TS DC CC TS Fig.2. Equivalent circuit for each operation mode (Note–the blue color shows components among which commutations occur). SCYR 2010 - 10th Scientific Conference of Young Researchers – FEI TU of Košice UGS T1,T2 UGS Ts T3,T4 Ts Ts U uP iP td discharges the internal capacity of transistors T1 – T4, respectively and so the condition of ZVS is achieved. Fig.7. (bottom waveforms) shows the simulation waveforms of currents flows through clamp capacitor Cc, diode Ds and clamp diode Dc during cycle of operation Ts. D3,D4 T1,T2 uP U.(NS/NP) COSS1-COSS1 iD0 iD iD5 Us iD0 iD6 iD0 iTS Fig.4. Turn-on and turn-off waveforms of the leading-leg and legging-leg switch T4. iCc iDc t0 t1 t2 t3 t4 M1 M3 M2 M4 t7 t8 t9 t5 t6 M7 M5 M6 t M9 M8 Fig.3. Operation waveforms of the proposed converter III. SIMULATION RESULTS A simulation model in programme Orcad was created to verify the properties of the proposed converter. The simulations were made at input voltage U = 325V. Parameters: Transformer TR parameters: Turns ratio n = 4, Magnetizing inductance Lm = 1 mH, Leakage inductance LLP = 5 µH. Clamp circuit parameters: Clamp capacitor CC = 400 nF, Clamp inductance LS = 5 µH. Fig.4. shows the waveforms during turn-on and turn-off of the primary switch T4. The influences of secondary active clamp circuit insure that all switching devices are switched softly. As we can see the leading-leg for transistor T4 is switched softly and the switching loss is neglectable. Fig.5 shows the secondary voltage uDS and collector current iD of transistor Ts (upper waveforms) in compare with switch waveforms of voltage uCE and collector current iC of transistor T4 (bottom waveforms). It can be seen that influence of leakage inductance LLS of transformer and clamp inductance LS insure that turn-on of transistor Ts is under zero-current and just as in the previous case (Fig.4) the power losses can be neglectable, too. Fig.6 and Fig.7, respectively show simulation waveforms of voltage uDS and collector current iD of transistor Ts (upper waveforms) in compare with primary voltage uP and current iP (bottom waveforms of Fig.6). After turned-off of secondary transistor Ts only small magnetization current im flows through the primary winding. This current charges and Fig.5. Waveforms of voltage uDS and collector current iD of transistor Ts (upper waveforms) and switch voltage uCE and collector current iC of transistor T4 (bottom waveforms). Fig.6. Waveforms of voltage uDS and collector current iD of transistor Ts (upper waveforms) and primary voltage uP and current iP (bottom waveforms). Fig.7. Waveforms of voltage uDS and collector current iD of transistor Ts (upper waveforms) and currents waveforms of Dc, Cc and Ds (bottom waveforms). SCYR 2010 - 10th Scientific Conference of Young Researchers – FEI TU of Košice IV. CONCLUSION A novel zero-voltage and zero-current switching (ZVZCS) full bridge phase-shifted PWM converter is presented in this paper. The properties of the proposed converter topology were analyzed. Theoretical analysis was verified by simulation. It is shown that using of secondary active clamp circuit the soft switching conditions for all switching devices T1 - T4 located on the primary side is achieved. ACKNOWLEDGMENT This work was supported by Slovak Research and Development Agency under project APVV-0095-07 and by Scientific Grant Agency of the Ministry of Education of Slovak Republic under the contract VEGA No.1/0099/09. REFERENCES [1] [2] [3] [4] [5] [6] [7] [8] [9] H. -S. Choi, J. –W. Kim, B. H. Cho, “Novel Zero-Voltage and ZeroCurrent-Switching (ZVZCS) Full-Bridge PWM Converter Using Coupled Output Inductor,” IEEE Trans. Power Electron., vol. 17, No. 5, SEPTEMBER 2002, pp.641-648. J. G. Cho, J. W. Beak, D. W. Yoo, H. S. Lee and G. H. Rim, “Novel Zero-Voltage and Zero-Current-Switching (ZVZCS) Full-Bridge PWM Converter Using Transformer Auxiliary Winding,” in Conf. Rec. IEEE PESC`97,pp.227-232. T. –F. Chen, S. Cheng, “A Novel Zero-Voltage Zero-Current-Switching Full-Bridge PWM Converter Using Improved Secondary Active Clamp,” IEEE ISIE, July 9-12, 2006, Montreal, Québec, Canada, pp. 1683-1687 J. –G. Cho, J. –W. Baek, Ch. –Y. Jeong, and G. –H. Rim, “Novel ZeroVoltage and Zero-Current-Switching Full-Bridge PWM Converter Using a Simple Auxiliary Circuit,” IEEE Trans. Industry Applications., vol. 35, no. 1, January/February 1999, pp.15-20. A. Jangwanitlert, K.J. Olejniczak, J.C. Bala, “An Improved ZeroVoltage and Zero-Current-Switching PWM Full-Bridge DC-DC Converter,” IEEE 2003.227-232. J. Dudrík, V. Ruščin, “Voltage Fed Zero-Voltage and Zero-CurrentSwitching PWM DC-DC Converter,” In: EPE-PEMC 2008: 13th International Power Electronics and Motion Control Conference : 1 - 3 September 2008, Poznan - Poland. S.l.: IEEE, 2008. p. 295-300. ISBN 978-1-4244-1742-1 J. G. Cho, C. Y. Jeong, and F. C. Y. Lee. “Zero-Voltage Zero-CurrentSwitching Full-Bridge PWM Converter Using Secondary Active Clamp,” IEEE Trans on Power Electronics, 1998, 13(4): 601-607 J. Dudrík, V. Ruščin, “ZVZCS PWM DC-DC Converter with Controlled Output Rectifier,” Acta Electrotechnica et Informatica januar-march 2010. vol. 10, pp.12-17 Dudrik, J., Oetter, J.: Soft-Switching PWM DC-DC Converter for High Power Applications, EPE-PEMC 2006, Portorož, Slovenia, ISBN 14244-0121-6, CD, pp. 739-744