PhD in: Ingegneria Elettrica, Elettronica e delle

advertisement

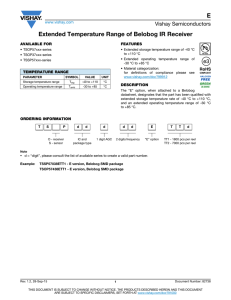

PhD in: Ingegneria Elettrica, Elettronica e delle Comunicazioni Research Title: Study of Material, Design and Technology Effect on High Power Diodes Electrical Overstress failures Funded by Vishay Semiconductor SpA Supervisor Contact Context of the research activity Rossano Carta (rossano.carta@vishay.com) Vishay Semiconductor Italiana S.p.A. Fabrizio Pirri (fabrizio.pirri@polito.it) Politecnico di Torino www.vishay.com This PhD program implies an Industrial collaboration with Vishay Semiconductor Company SpA. The PhD student is required, after an induction and safety trainings, to have majority of its Research activities at Vishay Production Plant in Borgaro (TO) and at Vishay Power Device Evaluation Lab inside Politecnico di Torino. Worldwide users, not only Automotive customers, are keeping requiring better and better reliability of the High Power components. The components lifetime is requested to be always increased and their failure rate in the Field has to be decreased in every new device generation. In addition to Standard Reliability, the devices are requested to withstand during critical conditions (not declared in device Data Sheets) in challenging ambients. To support these new and specific requirements, the historical reliability test and stress condition have to be revised and integrated with new Stress‐Test system and device behavior have to be experimentally studies and modeled using Simulation tools. These new approaches to understand and assure new advanced reliability Standards, represent an undiscovered Research Field in Power Semiconductor and the worldwide academic community began to be focused on it. Due to what described above, Vishay Italy needs to begin a research Project, in collaboration with Politecnico di Torino, focused on the deep study of its Diode families under new stressful reliability condition, with the aim to do: _ understand typical device weaknesses under several and critical Electrical and Thermal Overstresses _ Generate Physical Models using Finite Element Simulations to describe the devices under critical stress conditions and prevent their failures. _ Propose new Thermo/Electrical Test tool/System (to be implemented in Vishay Eval. Lab at Politecnico) to reproduce such critical reliability conditions on the devices under test _ Highlight potential device weaknesses and propose Design/Material/Technology solution to improve the device roughness Objectives The activities of PhD. Student can be divided by several task/objectives, linked each others: _ Focused on High Power diodes from 200V up to 1200V Blocking voltage: collect Failure analysis reports, Marketing, Field application feedback of the majority customer request and returns due to Electrical Overstress, to prepare a Data base, then a Pareto analysis of the stress types (working in avalanche conditions, high frequency switching conditions, ESD Electrical Discharge,..) _ Perform research on scientific literatures about the above phenomena, with focus on high power diodes, to find physical causes of the device behavior in the critical working conditions _ Perform Diode Competitor analysis, get the parts and prepare a benchmark report on their performances on typical device overstress condition. _ Develop Physical Device Modeling, using Finite Element Simulation tools, capable of describing and preventing device behaviors under defined and particular stress conditions, in line with critical device application in the Field. Special focus will be on Material and Metal interconnection effect, under high temperature conditions. _ Develop, in Team with Vishay Politecnico Evaluation Lab some Test Systems to stress and prove device reliability under Special Conditions, to support device analysis, modeling and their improvement _ Working in Team with R&D Development Group, as well interacting with Si/material suppliers, propose and follow up Experiments to perform at Vishay Borgaro Production Plant, to put in evidence device strongness/weakness and their correlation with specific Material/design/Technology aspects. _ Coordinate and Perform Device Failure analysis and reverse engineering at Vishay Failure analysis Lab as well at Politecnico Labs (SEM, EDX, XPS, FIB) to understand effect tested in Experiments on devices and compare them with competition _ After Data statistical analysis and comparison with competition benchmark, share the results with Team, to proceed on with the next Experiment learning cycles (iterative process) _ At the End of PhD research period, the student is requested to formulate Material/Design/Process solution to improve main diode device roughness for the most important and critical stress conditions To successfully complete the above tasks, the PhD student need to have or improve during its 3 year period, following skills and competences: _ Flexibility as well as scientific curiosity to understand and solve problems _ Good English language written and spoken, to interact with several functions inside Vishay Company, often based in other Worldwide Plants _Good knowledge on Power Semiconductor Devices (especially Skills and competencies for diodes), focus on their Physics, Material properties and the development of the Technologies as well as Device Finite Element Simulations activity _ Good attitude to Team Work, to interact with R&D Development Team, as well as with Manufacturing Organization during Experiments follow up in the Production lines _ Good knowledge on Design of Experiments and Problem Solving techniques, as well as Statistical data analysis, to better organize experiments and obtain the best from the results _ Knowledge of Failure analysis techniques for semiconductor devices _Knowledge of device characterization techniques and Test tool