ECE 349 Homework Assignment #5 Solutions 1. Is the set of

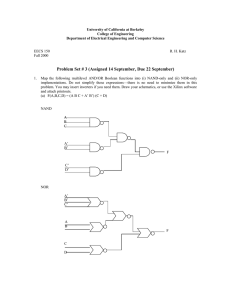

advertisement

ECE 349 Homework Assignment #5 Solutions 1. Is the set of operators Exclusive-OR and OR functionally complete? Justify your answer. Exclusive-OR and OR are functionally complete. A0 = 1 ⊕ A, and (A0 + B 0 )0 = AB. 2. Realize the function f = a0 bc0 + bd + ac + b0 cd0 using only 2-input NAND gates. A’ C’ B’ D’ B D’ F C A’ 3. The following equation is implemented using AND gates, OR gates, and inverters. Convert the circuit to use only NAND gates and inverters (do not manipulate the equation with Boolean algebra). f (a, b, c, d) = b(a(bc + d0 ) + c0 d) b c d’ f a c’ b d 4. Repeat problem (3), but this time convert the circuit to use only NOR gates and inverters. b’ c’ d’ f a’ c d’ b’ 5. Design a network of NAND gates and inverters that converts from 8-4-2-1 BCD code to 6-3-1-1 code (see Table 1-1 in your text). b c a’ w = a + bc a d b’ c d x = ad + bc’ + b’cd b c’ a d’ a’ c’ d z = ad’ + bc’ + bd + b’cd’ + a’c’d b d y = ad’ + b’cd’ + bc’d b’ c d’ b c’ d 6. Show how to build each of the following single-output logic functions using a 3-to-8 line decoder with inverted outputs and NAND gates: P (a) f (a, b, c) = m (3, 5, 6) Q (b) f (a, b, c) = M (3, 4, 5, 6, 7) 74LS138 +5 V G1 G2A G2B a b c C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 74LS138 +5 V G1 G2A G2B f a b c C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 f 7. Use an 8-to-1 multiplexer to realize the function f (a, b, c, d) = with b, c, and d as the control inputs. ab 00 cd 01 11 00 01 10 1 1 11 1 1 1 1 10 1 a D0 1 D1 0 D2 0 D3 0 D4 1 D5 a D6 a’ D7 Y f MUX C B A b c d 8. Use an 8-to-1 multiplexer to realize the function f (a, b, c, d) = with a, b, and c as the control inputs. ab 00 01 11 00 1 01 1 11 1 10 10 1 1 1 1 d D0 d D1 d D2 d’ D3 d’ D4 d D5 0 D6 d D7 m (1, 5, 7, 8, 9, 13, 14), 8-to-1 EN cd P P m (1, 3, 5, 6, 8, 11, 15), 8-to-1 Y f MUX EN C B A a b c 9. (Optional, 2 points) Use a 4-to-1 multiplexer and any extra logic gates you may need to implement the function of problem (8). Use variables c and d as the control inputs to the multiplexer. b’ a C0 C1 a’ b 4-to-1 Y C2 C3 G MUX B A c d f 10. An adder for Gray-coded decimal digits (see Table 1-1 in your text) is to be designed using a ROM. The adder should add two Gray-coded digits and give the Gray-coded sum and a carry. For example, 1011 + 1010 = 0010, with a carry of 1 (7 + 6 = 13). Draw a diagram showing the required ROM inputs and outputs. What size ROM is required? Indicate how the truth table for the ROM would be specified by giving two typical rows. x3 x2 x1 x0 ROM 256 Words x y3 y2 y1 y0 5 Bits s3 s2 s1 s0 x3 x2 x1 x0 y3 y2 y1 y0 s3 s2 s1 s0 c 1 0 0 1 1 0 0 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 0 0 0 1 carry 11. A PLA capable of implementing 6 product terms will be used to implement the following equations X = abd + a0 c0 + bc + c0 d0 , Y = a0 c0 + ad + c0 d0 , and Z = cd + a0 c0 + ab0 d. Give the PLA table. Notice that ad = ab0 d + abd. Product Terms abd a’c’ bc c’d’ ab’d cd Inputs Outputs abcd XYZ 11-1 110 0-0111 -11100 --00 110 10-1 011 --11 001