A Novel Substrate-Assisted RESURF Technology for Small

advertisement

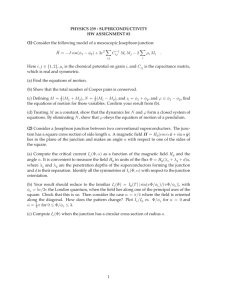

Proceedings of the 23rd International Symposium on Power Semiconductor Devices & IC's May 23-26, 2011 San Diego, CA A Novel Substrate-Assisted RESURF Technology for Small Curvature Radius Junction Ming Qiao, Xi Hu, Hengjuan Wen, Meng Wang, Bo Luo, Xiaorong Luo, Zhuo Wang, Bo Zhang and Zhaoji Li State Key Laboratory of Electronic Thin Films and Integrated Devices University of Electronic Science and Technology of China Chengdu, P.R.China E-mail:qiaoming@uestc.edu.cn Abstract—A novel substrate-assisted (SA) RESURF technology aiming at improving off-state breakdown voltage (BV) of PN junction with small curvature radius is proposed and experimentally demonstrated in this paper. The SA RESURF technology not only realizes small curvature radius in the fingertip region, but also reduces electric field concentration in the curved metallurgical junction. Low-doped P-substrate, which increases depletion of the small curvature radius junction and reduces electric field concentration in the curved metallurgical junction, is adopted in the source fingertip region. Owing to the existence of low-doped P-substrate, the abrupt PN junction with small curvature radius is adjusted to low-doped PN junction with large curvature radius. The SA RESURF technology can be widely applied to lateral high voltage devices with small curved junction, especially to lateral super junction devices. A CBSLOP-LDMOS with the proposed SA RESURF technology has been developed. The experimental results show that the CBSLOP-LDMOS exhibits off-state BV of 700 V and specific on-resistance (Ron,sp) of 142 mΩ·cm2. I. necessary for high voltage device to gain optimal breakdown characteristics, but small device area is a significant factor to obtain low Ron,sp. Therefore, a novel SA RESURF technology for small curvature radius junction, which can improve offstate BV characteristics through substrate-assisted depletion effect and reduce Ron,sp, is proposed and experimentally demonstrated in this study. II. Figure 1 shows schematic surface view of the proposed SA RESURF technology. Figure 2 shows three-dimensional view of the source fingertip region with the SA RESURF technology. In the curved junction, we adopted low-doped Psubstrate instead of partial high-doped N-well, by which abrupt P-well/N-well junction with small curvature radius is adjusted to low-doped P-substrate/N-well junction with large curvature radius. The depletion layer of P-substrate/N-well curved junction will sustain the applied high voltage. Due to low-doped concentration and large curvature radius of Psubstrate, the electric field concentration is efficiently reduced and the breakdown voltage can be improved. Premature breakdown, which may occur at high-doped P-well/N-well junction with small curvature radius, can be avoided. Based on the low-doped P-substrate which assists depletion of small curvature radius junction and reduces surface electric field concentration of the curved metallurgical junction, the substrate-assisted RESURF (SA RESURF) technology was proposed. INTRODUCTION Reduced surface field (RESURF) technology is widely used for the lateral devices with high breakdown voltage and low Ron,sp[1]-[3]. Since the depletion of vertical metallurgical junction is reinforced by the horizontal junction, the surface electric field of RESURF device is reduced at the same applied voltage. The surface electric field is far below the critical electric field and much higher applied voltage can be achieved before the avalanche breakdown occurs. The surface breakdown can be eliminated and the ideal bulk breakdown can be reached. However, the layout of lateral high voltage semiconductor device is occlusive. Curved source or drain junction will lead to premature breakdown. The curvature radius of the source or drain fingertip region, which even affects the device area and Ron,sp, has a crucial relationship with the off-state breakdown characteristics[4]. The avalanche breakdown can be expected to occur in the fingertip region rather than in the straight edge of the conventional RESURF LDMOS, on account of the abrupt PN junction with small curvature radius strengthening the concentration of electric field. The smaller the curvature radius of the source or drain fingertip region is, the lower the breakdown voltage will be. Large curvature radius is 978-1-4244-8423-2/11/$26.00 ©2011 IEEE SUBSTRATE-ASSISTED RESURF TECHNOLOGY Fig.1 Schematic surface view of the CBSLOP-LDMOS with the proposed SA RESURF technology. 16 Fig.2 Three-dimensional view of the source fingertip region with the proposed SA RESURF technology. (a) The source fingertip region with conventional RESURF technology (b) The source fingertip region with the proposed SA RESURF technology (small LP) (c) The source fingertip region with the proposed SA RESURF technology (optimal LP) (d) The source fingertip region with the proposed SA RESURF technology (large LP) (a) (b) Fig.3 The cross-section of the source fingertip region along (a) X and (b) Y direction. Figure 3 (a) shows schematic cross-sectional view along x direction. Figure 3 (b) shows schematic cross-sectional view along y direction. For straight edge part of the LDMOS, conventional RESURF structure is adopted. If we use this structure in the curved part, high-doped P-well with small curvature radius will lead to premature breakdown in curved junction. Low-doped P-substrate, which can introduce additional charges in the depletion region, can reduce the peak electric field at the P-well/N-well junction. These additional charges can create a new peak electric field at the Psubstrate/N-well junction. Due to low-doped P-substrate, the curvature radius of the curved junction is remarkably increased, thus the surface electric field concentration and the breakdown voltage of the LDMOS can be improved. Fig.4 Schematic electric field crowding effect for small curvature radius junction: (a) conventional RESURF technology, and (b)-(d) SA RESURF technology with various LP. large. Figure 4 (c) shows the source fingertip region with the proposed SA RESURF technology when LP is equal to an optimal value. The reduction of electric field concentration in the curved junction will eliminate the premature breakdown occurring in the low-doped P-substrate/N-well junction. At the same time, the optimal length of p/n columns will lead to a longer voltage sustain layer. Therefore, the breakdown voltage of the fingertip region with a small curvature radius can be improved. Figure 4 (a) shows schematic electric field crowding effect of the source fingertip region with conventional RESURF technology. LP is the distance between P-well and N-well in the fingertip region. When Lp is equal to 0 μm, electric field concentration occurs at high-doped P-well/N-well junction with the smallest curvature radius, leading to the lowest BV. Figure 4 (b)-(d) show schematic electric field crowding effect of source fingertip region using the proposed SA RESURF technology with various LP. In Fig.4 (b), small LP intensifies the electric field concentration of the curved junction and then causes premature breakdown in low-doped P-substrate/N-well junction. In Fig.4 (d), the length of p/n columns laid on N-well of the source fingertip region is cut down. Although large LP decreases the surface electric field concentration of curved junction, the decreased p/n columns will lead to low breakdown voltage due to the reduction of depletion layer length of p/n columns. Therefore LP can’t be too small or too III. RESULTS AND DISCUSSION A LDMOS with a charge-balanced surface low onresistance path (CBSLOP) layer is taken for example, as shown in Fig.1 [5]-[6]. A high-doped super junction region consisting of alternate P-type and N-type columns is located at the surface of N-well. High-doped CBSLOP layer supplies low on-resistance. And simultaneously, surface electric field is reduced by the assisted depletion of p/n columns, resulting in the improvement of breakdown characteristics. The CBSLOPLDMOS based on a super junction concept can not only provide low Ron,sp in on-state but also high breakdown voltage in off-state. By using three-dimensional and two-dimensional device simulations which are carried out by SILVACO, the CBSLOP-LDMOS with the proposed SA RESURF technology is optimized. 17 600 160 500 140 400 120 300 100 200 0 1 2 3 4 5 6 Off-state BV (V) 180 800 250 700 600 200 500 400 150 300 200 W=0.5 m W=1.0 m W=2.0 m 100 0 80 0 1 2 Fig.5 BV and Ron,sp of CBSLOP-LDMOS as a function of drift concentration(Wn=Wp=1 μm, NA=ND=3E16 cm-3, Xj=1.5 μm). 150 W=0.5 m W=1.0 m W=2.0 m 0.5 Off-state BV (V) 200 Ron,sp (mcm2) Off-state BV (V) 7 8 9 50 10 800 650 500 6 900 250 700 550 5 Fig.7 BV and Ron,sp as a function of p/n column concentration with different p/n column widths ( Ndrift=3E15 cm-3, Xj=1.5 μm, ND=NA). 750 600 4 ND (1016cm-3) N-drift (1015cm-3) 800 3 100 Ron,sp (mcm2) 700 300 900 200 Ron,sp (mcm2) Off-state BV (V) 800 700 600 500 W=0.5 m W=1.0 m 400 1.0 1.5 300 100 W=2.0 m -20% -10% 0% +10% +20% Charge imbalance Fig.8 BV as a function of charge imbalance with different p/n column widths (Ndrift=3E15 cm-3, Xj=1.5 μm, ND= 3E16 cm-3). Xj (m) Fig.6 BV and Ron,sp as a function of p/n column junction depth (Xj) with different p/n column widths (W) (Ndrift=3E15 cm-3, NA=ND=3E16 cm-3). at the condition that P-column concentration is slightly lower than N-column at W=0.5 μm. The maximum BV occurs at the condition that P-column concentration is slightly higher than N-column at W=2 μm. Figure 5 shows simulated off-state BV and Ron,sp of CBSLOP-LDMOS as a function of drift concentration at Wn=Wp=1 μm, NA=ND=3E16 cm-3, and Xj=1.5 μm. NA is the concentration of p column and ND is the concentration of n column. Ron,sp is obviously reduced with the increase of drift concentration. However, the drift concentration can not be too large for the reduction of the off-state breakdown voltage. The peak value of the off-state BV appears when drift concentration is equal to 3E15 cm-3. In considering of the continuity of electric field, it is necessary to optimize the fingertip region with the proposed SA RESURF technology, especially the conjunction between the source fingertip region and straight edge part of the CBSLOP-LDMOS. Mutation of the structure in this Figure 6 shows simulated off-state BV and Ron,sp as a conjunction will induce the radical change of surface electric function of p/n column junction depth (Xj) with different p/n field distribution at an applied voltage. Figure 9 shows surface column widths (W) at Ndrift=3E15 cm-3 and NA=ND=3E16 cm-3. electric field distribution of the fingertip region with the Although deep depth of p/n column can reduce Ron,sp, the off- proposed SA RESURF technology. In Fig.9 (a) and Fig.9 (c), state BV is reduced as the increase of Xj at W=2 μm due to semi-CBSLOP layer is placed in N-type drift region of the incomplete depletion of p/n columns. For Xj from 0.5 μm to source fingertip region and the difference is the p/n column 1.5 μm, high off-state breakdown voltage can be achieved at sequence of smei-CBSLOP layer. The initiative column of the W=0.5 μm and W=1 μm. source fingertip region in Fig.9 (a) is N-type column. The initiative column of the source fingertip region in Fig.9 (c) is Figure 7 shows simulated off-state BV and Ron,sp as a P-type column. Figure 9 (b)-(d) show the source fingertip function of p/n column concentration with different p/n region without smei-CBSLOP layer. Figure 9 (e) shows the column widths at Ndrift= 3E15 cm-3, Xj=1.5 μm, and ND=NA. surface electric field distribution along AA’, BB’, CC’, DD’ Ron,sp is obviously reduced with the increase of the p/n column and EE’ lines. With the assisted depletion of CBSLOP layer, concentration. Due to incomplete depletion of p/n column, off- new peaks of surface electric field between p/n columns state BV is reduced at W=1 μm and W=2 μm with the rising appear and the depletion region is visibly extended. When the p/n column concentration. Off-state BV is close to constant at initiative column of the straight edge part of the CBSLOPW=0.5 μm. Therefore, small W helps to complete depletion of LDMOS is N-type column, premature breakdown occurs due the p/n column. to imcomplete depletion of the N-type column. When the Figure 8 shows simulated off-state BV as a function of initiative column of the straight edge part is P-type column, charge imbalance with different p/n column widths at the breakdown voltage of the CBSLOP-LDMOS can be Ndrift=3E15 cm-3, Xj=1.5 μm and ND=3E16 cm-3. Charge improved. The optimal conjunction structure for the CBSLOPimbalance is one of the main issues for the super junction LDMOS with the proposed SA RESURF technology is shown concept implemented in LDMOS. The maximum BV occurs in Fig.9 (a). 18 Vg=5 V N P N P N P N P N X:1 V/div Y:2 mA/div Drain Drain NP P N PN P N P-sub P N P N N-well P N P N P N P N P N P-sub P N P N P N P N P N P N (b) (a) (b) (a) Fig.11 Experimental results of the CBSLOP-LDMOS with the proposed SA RESURF technology: (a)measured output characteristics and (b)measured off-state breakdown characteristics. IV. Drain N P N P N P N P N P PN PNP N P-sub P N P N P N N P N P P N P Electric Field (105 V/cm) (c) N P N P (d) 3.0 2.5 2.0 1.5 AA' BB' CC' DD' EE' 1.0 0.5 0.0 0 10 20 30 40 50 60 70 80 X distance (m) (e) Fig.9 Surface electric field distribution of source fingertip region with the proposed SA RESURF technology. ACKNOWLEDGMENT Gate Project supported by National Natural Science Foundation of China (Grant No.60906038) and the Science-Technology Foundation for Young Scientist of University of Electronic Science and Technology of China (Grant No.L08010301JX0830). Drain 35µm Super Junction Source (a) CONCOLUTION SA RESURF technology can be widely applied in lateral high voltage device, such as single RESURF, double RESURF LDMOS and super junction device, etc. The surface electric field at small curvature radius junction can be reduced and high breakdown voltage can be achieved by using the proposed SA RESURF technology. A CBSLOP-LDMOS with the proposed SA RESURF technology has been developed. Based on the simulated results, the optimal structure with the SA RESURF technology is obtained when the initiative column of the straight edge part of the CBSLOPLDMOS is P-type column. Compared with the previous work, the area of fingertip region is reduced on account of the reduction of the curvature radius. Finally the measured results prove that the CBSLOP-LDMOS with the proposed SA RESURF technology exhibits BV of 700 V and Ron,sp of 142 mΩ·cm2. Low cost, small area, low Ron,sp and high BV make the CBSLOP-LDMOS with the proposed SA RESURF technology a competitive device for high voltage power IC applications. Drain N-well PN P N P N P-sub N P N P X:300 V/div Y:5 µA/div (b) REFERENCES Fig.10 (a) Micrograph of the CBSLOP-LDMOS with the proposed SA RESURF technology, (b) Micrograph of the CBSLOP-LDMOS in previous work. [1] Figure 10 (a) shows micrograph of the CBSLOP-LDMOS with the proposed SA RESURF technology. Figure 10 (b) shows micrograph of the CBSLOP-LDMOS in previous work[6]. Compared with the previous work, the area of fingertip region is significantly reduced on account of the reduction of the curvature radius. [2] [3] [4] Figure 11 (a) shows measured output characteristics of the CBSLOP-LDMOS with the proposed SA RESURF technology. Figure 11(b) shows measured off-state breakdown characteristics of the CBSLOP-LDMOS with the proposed SA RESURF technology. The CBSLOP-LDMOS exhibits offstate BV of 700 V and Ron,sp of 142 mΩ·cm2, leading to power FOM, expressed as FOM=BV2/ Ron,sp, of 3.45 MW/cm2. 19 [5] [6] J. Appels, H. Vaes and J. Verhoeven, “High Voltage Thin Layer Devices (RESURF Devices),” IEDM, Washington, DC., USA, December 1979, pp. 238-241. H. Vaes and J. Appels, “High voltage, high current lateral devices,” IEDM, San Francisco, California, USA, December 1980, pp. 87-90. A.W. Ludikhuize, “A Review of RESURF Technology,” in Proc. of ISPSD, Toulouse, France, May 2000, pp. 11-18. S. H. Lee, C. K. Jeon, J. W. Moon and Y. C. Choi, “700V Lateral DMOS with New Source Fingertip Design,” in Proc. of ISPSD 2008, Orlando, Florida, USA, May. 2008, pp. 141-144. B. Zhang, L. Chen, J. Wu and Z. J. Li, “SLOP-LDMOS - A Novel Super-Junction Concept LDMOS and Its Experimental Demonstration,” in Proc. of ICCCAS, Hong Kong, China, May 2005, pp. 1399-1402. B. Zhang, W. L. Wang, W. J. Chen, Z. H. Li and Z. J. Li, “HighVoltage LDMOS with Charge-Balanced Surface Low On-Resistance Path Layer,” IEEE Electron Device Letters, vol.30, pp. 849-851, 2009.