A New Power Factor Correction and Ballast Control IC

advertisement

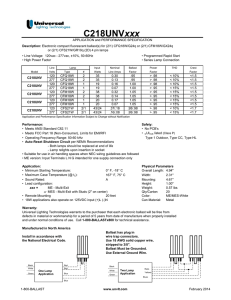

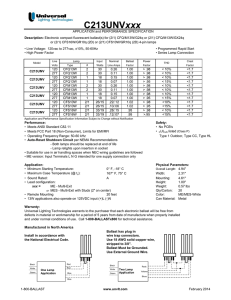

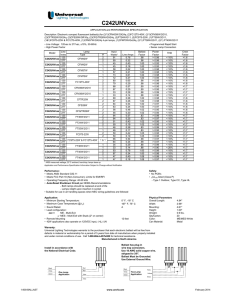

A New Power Factor Correction and Ballast Control IC Thomas J. Ribarich International Rectifier 233 Kansas St., El Segundo, CA, 90245-4382 tel. (310)726-8870, fax. (310)726-8846, email: tribari1@irf.com as presented to the IEEE Industry Applications Society Abstract: A new control IC has been developed which includes active power factor correction, ballast control, and a 600V halfbridge driver output. An improved control method has also been developed for power factor correction using a modulation technique to achieve low harmonic distortion. This new control IC has the following electronic ballast system implications: 1) 2) 3) 4) 5) 6) 7) 8) 9) 10) 11) 12) Single-chip electronic ballast solution Multi-lamp capability Universal Input Low THD and high PF Regulated DC bus voltage No PFC current-sensing resistor required Single +15V supply voltage Reduction of IC supply current End-Of-Life protection Complete lamp fault protection Reduction of PCB interconnects and IC pin requirements Reduction of ballast component count The result is a high-performance complete ballast solution with a significant cost reduction. A complete non-dimming ballast has been built that incorporates this new integrated circuit and verifies all of these features. I. INTRODUCTION The purpose of this paper is to present a new control IC which includes both power factor correction and ballast control. By combining these functions into a single IC the ballast system can be greatly simplified. II. OVERVIEW Most electronic ballasts for fluorescent lighting on the market today incorporate a two-stage architecture consisting of a boost converter running in critical-conduction mode for sinusoidal input current and a regulated DC bus, and a half-bridge driven resonant output stage for lamp control (Figure 1). Figure 1, Typical two -stage ballast architecture This architecture is typically controlled using a multi-chip solution that can contain up to three control ICs (Figure 2). These include a power factor correction (PFC) control IC, a ballast control IC or ASIC, and a half-bridge driver IC. +15V +5V PFC IC ASIC +15V Half-Bridge Driver IC Figure 2, Typical multi-chip ballast solution The new control IC is a combination of these functions into a single IC (Figure 3). This new IC contains the necessary functions for two independent control blocks including PFC control for regulating the line input current and ballast control for driving the fluorescent lamp. For this new IC to be commercially attractive to the electronic ballast market, the complete system cost must be the same or lower than existing multi-chip solutions. To meet this requirement, a simplified PFC control method has been developed which needs less silicon area, fewer external control pins and fewer external components. L2 R8 D2 R1 L1 L R4 C2 RV1 D1 R2 N BR1 R5 C8 GND 1 8 2 7 C1 R7 C3 3 C5 MC34262 4 R9 C6 M1 C7 6 5 R6 R3 C4 R10 Figure 4, Existing 8-pin PFC solution +15V PFC + Ballast + Half-Bridge Control IC Figure 3, New single-chip ballast solution III. SIMPLIFIED PFC CONTROL Existing critical-conduction mode PFC ICs compare the source current of the boost MOSFET against a threshold for controlling the on-time of the boost MOSFET. This on-time threshold is determined by the product of the instantaneous rectified line voltage and the error from the DC bus regulation. When the source current measured by a current sensing resistor exceeds the on-time threshold, the boost MOSFET turns off. The MOSFET remains off until the inductor current discharges to zero, as detected by a secondary winding on the boost inductor. At this time, the MOSFET turns on again and the cycle repeats itself. The result is a free-running frequency with the lowest frequency and maximum current occuring at the peak of the AC line input, and the highest frequency and minimum current occuring at the zero-crossings. This solution requires an external current-sensing resistor, an external voltage divider network and an internal multiplier (Figure 4). The new simplified control method is based on a constant on-time approach where the error between the DC bus measurement and a fixed reference voltage determines the on-time of the boost MOSFET. The off-time is also achieved using a secondary winding to detect the zerocrossing of the inductor current. The result is a much simpler solution which does not require an external current-sensing resistor, an external voltage divider network from the rectified line, nor an internal multiplier (Figure 5). The total IC control pin requirement (not including VCC and GND) is also reduced from six with existing PFC ICs to four with the improved method. L2 R8 D2 L1 L R4 C2 RV1 N D1 BR1 R5 C8 GND 1 8 C1 2 C3 3 C5 7 IR PFC 4 R9 C6 M1 C7 6 5 R6 Figure 5, Simplified 6-pin PFC solution This constant on-time approach gives a high power factor and good DC bus regulation over a wide input voltage range. The harmonic distortion of the line current, however, can exceed the limits given in the international standards and norms for electronic ballasts. The main cause of harmonic distortion is due to cross-over distortion of the line current at the zero-crossings of the line voltage. To reduce this, an additional on-time modulation has been included which increases the on-time during the zero-crossings of the AC line input voltage (Figure 6). frequency fStart ILPFC 0 fPH fRun fmin t PFC pin 0 5V V CPH ZX pin 2V V RPH 0 near peak region of rectified AC line near zero crossing region of rectified AC line 2V Figure 6, On-time modulation near zero crossing region V RUN Ignition Run mode Ramp mode Preheat mode IV. BALLAST CONTROL Figure 8, Ballast control sequence. The ballast control section includes a flexible oscillator for programming each ballast operating frequency, ballast and lamp fault logic, and endof-life detection logic (Figure 7). Preheat Timing High and Low -Side Driver Programmable Inputs Half -Bridge Driver Outputs Oscillator UVLO Low AC Line Over-Temp Detection Fault Logic End -of-Life Detection V. IR2167 SINGLE-CHIP SOLUTION The combination of all of the functions into a single chip allows for precise control of certain blocks depending on which mode the ballast is in. The PFC section is enabled, disabled or dynamically adjusted internally (Figure 9) as determined by the state machine of the ballast control section. Over --Current Lamp Out EOL Preheat Timing High and Low-Side Driver Programmable Inputs Half-Bridge Driver Outputs Oscillator UVLO Over-Temp Detection Figure 7, Ballast control section block diagram Fault Logic Low AC Line The ballast control sequence is best described by plotting the output frequency versus time (Figure 8). At initial start-up, the output frequency begins at a high-frequency and ramps quickly to the programmed preheat frequency. This internal soft-start prevents any flash from occuring across the lamp. The frequency then remains at the preheat frequency for the duration of the preheat time before ramping down to the minimum frequency for ignition. If necessary, the frequency can then be programmed to a higher run frequency once RUN mode has been reached. PFC Driver Output Zero-Crossing DC Bus Sensing Compensation PFC Control End-of-Life Detection Over-Current Lamp Out EOL Figure 9, IR2167 Ballast+PFC IC block diagram. The state machine (Figure 10) includes UVLO, Preheat, Ignition, Run and Fault modes. Several conditions must first be met in order to transition to each mode. Also, different protection blocks are activated at different times depending on which mode the ballast is in. The assymmetrical end-of-life protection, for example, is not activated until run mode to avoid a false detection during preheat or ignition. The PFC is also dynamically adjusted depending on the ballast mode. The gain of the PFC regulation loop is increased initially for a short quick start mode to increase the DC bus quickly, then increased again during ignition to reduce transients on the DC bus, then decreased during run mode for high power factor and low harmonic distortion. IR2167 control IC, and a half-bridge driven resonant output stage. L2 D1 R6 L1 C5 VDC CPH CPH CRAMP RPH C2 BR1 C4 RPH RT RT 4 RUN CT COC FAULT Mode Fault Latch Set 1 /2 -Bridge Off PFC Off COMP=0V I QCC ≅ 150µA CPH = 0V VCC = 15.6V 18 5 CT 6 RDT DT ROC M2 C10 VB R2 SD > 4.0V (Lamp Removal) or VCC < 9.5V (Power Turned Off) 19 3 RRUN R1 7 OC L3 C6 D2 17 R13 VCC C7 16 C8 COM C11 R14 15 LO R9 CS R10 M3 C12 D3 14 D5 EOL 8 13 9 12 10 11 R15 R12 R11 D4 C9 CCOMP 1/2-Bridge Off PFC Off COMP=0V I QCC ≅ 150µA CPH = 0V 20 2 VS C3 UVLO Mode 1 IR2167 C1 R8 HO RV1 N GND Power Turned On R SUPPLY R5 L COMP R7 PFC ZX RCS VBUS D6 R3 C13 D7 C13 R16 R4 M1 VCC > 11.4V (UV+) and VDC > 5.1V (Bus OK) and SD < 3.8V (Lamp OK) and TJ < 160C (Tjmax ) TJ > 160C (Over-Temperature) VCC < 9.5V ( or VDC < 3.0V or SD > 4.0V Note: Thick traces represent high-frequency, high-current paths. Lead lengths should be minimized to avoid high-frequency noise problems Figure 11, IR2167 Ballast Schematic. PREHEAT Mode 1 / 2 -Bridge @ fPH PFC Enabled CPH Charging @ I PH = 1µA RPH = 0V RUN = Open Circuit CS Disabled CS > OC Threshold (Failure to Strike Lamp or Hard Switching) or TJ> 160C (Over-Temperature) CS > OC Threshold (Over-Current or Hard Switching) or CS < 0.2V (No-Load or Below Resonance) or TJ > 160C (Over-Temperature) or SD < 1V or SD > 3V (End-of-Life) CPH > 4.0V (End of PREHEAT Mode) IGNITION RAMP Mode f PH ramps to fMIN CPH Charging @ I PH = 1µA RPH = Open Circuit RUN = Open Circuit CS OC Threshold Enabled The PCB layout (Figure 12) is greatly simplified with the new control IC. The IC pin locations have been selected for an optimum single-layer PCB board. Also, because the PFC solution does not require a current sense resistor, the layout is less critical as the PFC MOSFET can be placed away from the IC. CPH > 5.1V (End of IGNITION RAMP) RUN Mode f MIN Ramps to fRUN CPH Charges to 10V Clamp RPH = Open Circuit RUN = 0V CS 0.2V Threshold Enabled SD 1.0V and 3.0V Thresholds Enabled Figure 10, IR2167 state diagram VI. BALLAST DESIGN Figure 12, IR2167 Ballast PCB Layout. A fully-functional electronic ballast that incorporates the new control IC has been designed to the following specifications: • • • • • • • • • • • • • • • Ballast Type: T5 Universal Input Lamp Type: 35W/T5 Input Power: 14/21/28/35W Input Voltage: 90 to 265VAC Input Frequency: 0/50/60Hz Power Factor: > 0.95 THD: < 15% DC Bus: 400VDC+/-5% Ignition Voltage: 2KVpp Run Frequency: 42kHz Non-strike protection: yes Open filament(s) protection: yes End-of-Life protection: yes Over-temperature protection: yes Automatic restart: yes The ballast schematic includes (Figure 11) an EMI filter, a rectifier, a boost PFC circuit, the VII. RESULTS The ballast incorporating the new control IC was then evaluated for performance. The results verify (Figures 13 thru 20) a high power factor, low harmonics and a well regulated DC Bus over the line input voltage range. Also, good lamp control performance for preheat, ignition and running is also achieved as well as complete lamp fault protection. Figure 13, LO (upper) and PFC gate drive signals. Figure 17, Line input voltage and current (Vin=175VAC). 450 400 350 300 250 200 150 100 50 0 90 140 190 240 Line Input Voltage [VAC] Figure 14, Half-Bridge (upper) and CS waveforms. Figure 18, Line voltage versus DC bus voltage. 1 0.9 0.8 0.7 0.6 0.5 90 140 190 240 Line Input Voltage [VAC] Figure 15, Filament voltage during preheat. Figure 19, Line voltage versus power factor. 16 14 12 10 8 6 4 2 0 90 Figure 16, Lamp voltage during a non-strike. 140 190 240 Line Input Voltage [VAC] Figure 20, Line voltage versus DC bus voltage. VIII. CONCLUSIONS A new control IC has been developed which incorporates all of the necessary ballast functions. An improved PFC control method has been developed which gives good performance with a low component count. The complete ballast system which incorporates the new control IC is easier to manufacture, has a higher reliability and is reduced in cost. IX. REFERENCES [1] Elenbaas, W., ed., Fluorescent Lamps, Second Edition, Philips Technical Library, Eindhoven, The Netherlands 1971. [2] Paul R. Gray, Robert G. Meyer, Analysis and Design of Analog Integrated Circuits. Canada: John Wiley & Sons, Inc., 1984. [3] T. Ribarich, J. Ribarich, A New Model for High-Frequency Ballast Design, in IEEE-IAS Conf. Rec., 1997, pp. 2334-2339. [4] T. Ribarich, J. Ribarich, A New HighFrequency Fluorescent Lamp Model, in IEEE-IAS Conf. Rec., 1998. [5] International Rectifier, IR2167 Ballast Control IC, Data Sheet, 2001.