VMMK-3313

15 - 33 GHz Directional Detector in SMT Package

Data Sheet

Description

Features

The VMMK-3313 is a small and easy-to-use, broadband,

directional detector operating in various frequency bands

from 15 to 33 GHz with typical insertion loss of 0.5 dB. It is

housed in the Avago Technologies’ industry-leading and

revolutionary sub-miniature chip scale package (GaAsCap

wafer scale leadless package) which is small and ultra thin

yet can be handled and placed with standard 0402 pick

and place assembly equipment. The VMMK-3313 provides

a wide detecting power level from -5 to +30 dBm with

excellent input and output return losses. A typical of 15 dB

directivity is provided, and the detector requires only 1.5 V

DC biasing with small current drawn of 0.17 mA.

• 1 x 0.5 mm surface mount package

WLP0402, 1 mm x 0.5 mm x 0.25 mm

• Insertion Loss: 0.5 dB

• Ultrathin (0.25 mm)

• Wide frequency range: 15 to 33 GHz

• Wide dynamic range

• Low Insertion loss

• Directivity: 11-18 dB typ.

• In and output match: 50 ohm

Specifications (24 GHz, Vb = 1.5 V, Zin = Zout = 50 Ω)

• Bias Current: 0.17 mA typical

• Detector output offset voltage: 62 mV typical

• Detector Output voltage at +20 dBm: 1070 mV typical

TY

Applications

• Point-to-Point Radio

• Monitoring Power Amplifier Output Power

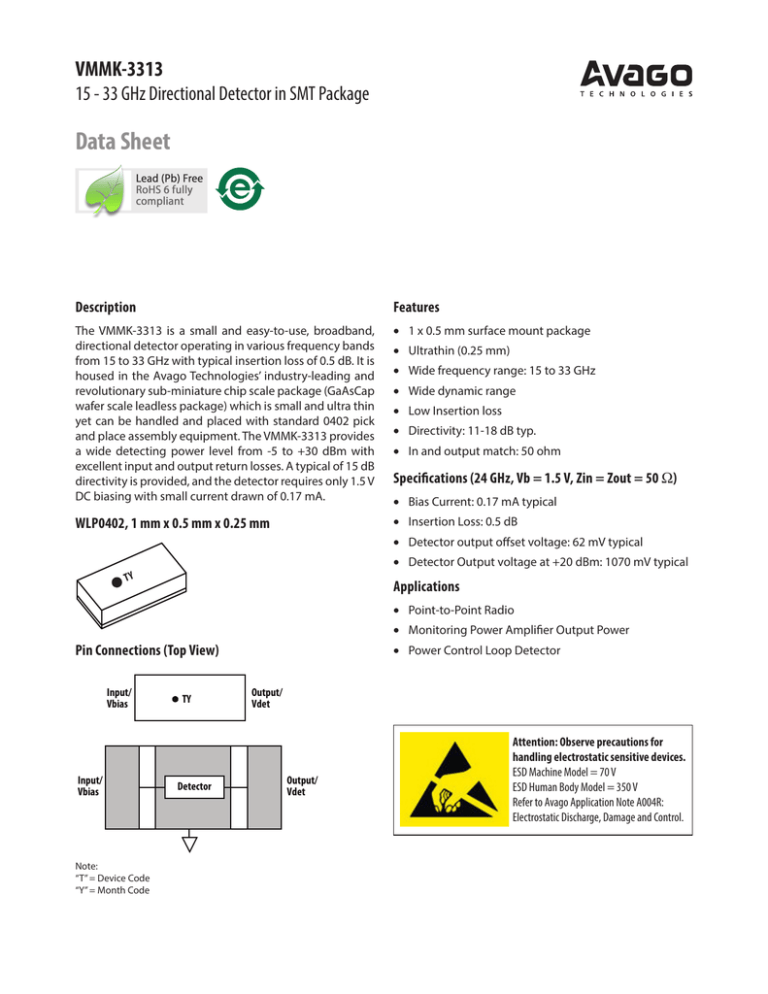

Pin Connections (Top View)

Input/

Vbias

Input/

Vbias

Note:

“T” = Device Code

“Y” = Month Code

TY

Detector

• Power Control Loop Detector

Output/

Vdet

Output/

Vdet

Attention: Observe precautions for

handling electrostatic sensitive devices.

ESD Machine Model = 70 V

ESD Human Body Model = 350 V

Refer to Avago Application Note A004R:

Electrostatic Discharge, Damage and Control.

Electrical Specifications

Table 1. Absolute Maximum Rating (1)

Sym

Parameters/Condition

Unit

Absolute Max

Vbias

Bias Voltage (RF Input)

V

2

Ibias

Bias Current

mA

1

Pin, max

CW RF Input Power (RF Input) (2)

dBm

+31

Tch

Max Channel Temperature

°C

+150

Tstg

Storage Temperature

°C

+150

Notes

1. Operation of this device above any one of these parameters may cause permanent damage

2. With the DC (typical bias) and RF applied to the device at board temperature, Tb = 25° C

Table 2. DC and RF Specifications

TA = 25° C, Freq = 24 GHz, Vb = 1.5 V, Zin = Zout = 50 Ω unless otherwise specified

Symbol

Parameters / Condition

Unit

Min

Typical

Max

Ibias (1)

Bias Current

mA

0.11

0.17

0.25

I.L. (1)

Insertion Loss

at 15 GHz

at 24 GHz

at 33 GHz

dB

IRL (1)

Input Return Loss

dB

20

ORL (1)

Output Return Loss

dB

20

Dir (2)

Directivity

at 15 GHz

at 24 GHz

at 33 GHz

dB

Voffset (1,3)

Detector Output Offset Voltage

mV

45

61

75

Vdet (4)

Detector Output Voltage at +20 dBm

mV

0.90

1.07

1.22

0.3

0.5

0.7

11

18

12

Notes

1. Measured data obtained from wafer-probing, losses from measurement system de-embedded from final data, Vbias = 1.5 V applied through a

broadband bias tee.

2. Measured by reversing the detector and applying RF power to the output port. Directivity is defined as the difference in dB between the power

applied in the forward direction and the power required in the reverse direction to produce the same Vdet voltage.

3. Voffset is measured with RF input power turned off.

4. Vdet is measured with +20 dBm RF input power at 22 GHz.

2

Product Consistency Distribution Charts at 24 GHz, Vbias = 1.5 V

LSL

0.11

USL

0.13

0.15

0.17

0.19

0.21

0.23

0.25

Ibias: Mean = 0.17 mA, LSL = 0.11 mA, USL = 0.25 mA

LSL

LSL

USL

50

60

70

Voffset: Mean = 61 mV, LSL = 45 mV, USL = 75 mV

USL

Notes:

Distribution data sample sized is based on at least 36 Kpcs taken from

MPV lots.

Future wafers allocated to this product may have nominal values

anywhere between the upper and lower limits.

900

1000

1100

1200

Vdet_On @ Pin = +20 dBm: Mean = 1.07 V, LSL = 0.9 V, USL = 1.22 V

3

VMMK-3313 Typical Performance

S-parameter data obtained using 300 mm G-S-G probe substrate; bias was brought in via broadband bias tees. Power vs.

Vdet data obtained using CPW PCB (Fig.8). Losses calibrated out to the package reference plane.

(TA = 25° C, Vbias = 1.5 V, Ibias = 0.14 mA, Zin = Zout = 50 Ω unless otherwise specified)

0.0

-0.2

1

S21 (dB)

Output DC Voltage (V)

10

0.1

-0.6

15 GHz

24 GHz

33 GHz

0.01

-10

-5

0

5

10

15

Pin (dBm)

20

25

-0.4

-0.8

30

Figure 1. Vdet vs. Input Power

10

15

20

25

Frequency (GHz)

30

35

30

35

Figure 2. Insertion Loss vs. Frequency

0

0

-5

-10

S22 (dB)

S11 (dB)

-10

-15

-20

-20

-30

-25

-30

10

15

20

25

Frequency (GHz)

30

-40

35

Figure 3. Input Return Loss

Output DC Voltage (V)

Output DC Voltage (V)

20

25

Frequency (GHz)

10

1

0.1

25° C

85° C

-40° C

-10

-5

0

5

10

15

Pin (dBm)

Figure 5. Pin vs. Vdet Over Temperature at 24 GHz

4

15

Figure 4. Output Return Loss

10

0.01

10

20

25

30

1

0.1

0.01

-10

1.5 V

1.2 V

1.8 V

-5

0

5

10

15

Pin (dBm)

Figure 6. Pin vs. Vdet Over Vbias at 24 GHz

20

25

30

Typical Scattering Parameters

Data obtained with 300 mm G-S-G probing on 0.016 inch thick PCB substrate, broadband bias tees, losses calibrated out

to the package reference plane. TA = 25° C, Zin = Zout = 50 Ω.

Freq

GHz

S11

dB

Mag

Phase

dB

Mag

Phase

dB

Mag

Phase

dB

Mag

Phase

2.0

-16.143

0.156

-90.494

-0.192

0.978

-0.747

-0.186

0.979

-0.679

-16.016

0.158

-93.644

3.0

-19.760

0.103

-96.650

-0.132

0.985

-8.728

-0.124

0.986

-8.670

-19.659

0.104

-105.358

4.0

-22.639

0.074

-100.139

-0.128

0.985

-15.231

-0.116

0.987

-15.156

-22.441

0.076

-116.420

5.0

-25.368

0.054

-99.264

-0.122

0.986

-21.092

-0.115

0.987

-21.017

-25.083

0.056

-130.972

6.0

-28.427

0.038

-93.825

-0.126

0.986

-26.725

-0.126

0.986

-26.669

-27.453

0.042

-151.611

7.0

-31.502

0.027

-78.538

-0.139

0.984

-32.188

-0.129

0.985

-32.126

-29.736

0.033

-178.623

8.0

-32.918

0.023

-48.363

-0.145

0.983

-37.503

-0.144

0.984

-37.516

-30.201

0.031

146.185

9.0

-31.634

0.026

-16.396

-0.169

0.981

-42.803

-0.155

0.982

-42.811

-29.020

0.035

115.496

10.0

-28.336

0.038

1.025

-0.174

0.980

-48.135

-0.171

0.981

-48.095

-26.897

0.045

90.525

11.0

-25.713

0.052

6.348

-0.191

0.978

-53.426

-0.185

0.979

-53.345

-24.672

0.058

75.623

12.0

-23.583

0.066

7.497

-0.204

0.977

-58.602

-0.208

0.976

-58.544

-23.312

0.068

62.771

13.0

-22.015

0.079

7.691

-0.225

0.974

-63.871

-0.226

0.974

-63.782

-21.841

0.081

52.793

14.0

-21.100

0.088

7.152

-0.247

0.972

-69.068

-0.240

0.973

-69.014

-21.002

0.089

44.150

15.0

-20.464

0.095

5.699

-0.261

0.970

-74.298

-0.261

0.970

-74.185

-20.612

0.093

34.963

16.0

-19.837

0.102

4.621

-0.288

0.967

-79.432

-0.279

0.968

-79.412

-20.070

0.099

26.214

17.0

-20.229

0.097

4.889

-0.302

0.966

-84.664

-0.300

0.966

-84.646

-20.473

0.095

19.684

18.0

-20.427

0.095

5.722

-0.311

0.965

-89.942

-0.308

0.965

-89.871

-21.130

0.088

12.443

19.0

-20.346

0.096

4.424

-0.331

0.963

-95.142

-0.334

0.962

-95.072

-21.190

0.087

3.542

20.0

-21.391

0.085

7.308

-0.346

0.961

-100.462

-0.345

0.961

-100.384

-22.651

0.074

-0.777

21.0

-22.441

0.076

10.427

-0.361

0.959

-105.667

-0.355

0.960

-105.641

-24.716

0.058

-5.533

22.0

-23.491

0.067

10.306

-0.377

0.958

-110.947

-0.376

0.958

-110.951

-25.900

0.051

-11.559

23.0

-25.304

0.054

23.895

-0.401

0.955

-116.285

-0.401

0.955

-116.288

-29.473

0.034

-2.535

24.0

-26.448

0.048

41.694

-0.416

0.953

-121.674

-0.419

0.953

-121.646

-34.943

0.018

31.366

25.0

-28.427

0.038

51.641

-0.453

0.949

-127.022

-0.455

0.949

-127.007

-35.189

0.017

74.893

26.0

-27.787

0.041

75.394

-0.472

0.947

-132.447

-0.476

0.947

-132.366

-29.168

0.035

83.707

27.0

-26.707

0.046

90.267

-0.505

0.944

-137.920

-0.505

0.944

-137.910

-25.547

0.053

87.920

28.0

-27.872

0.040

108.771

-0.517

0.942

-143.371

-0.519

0.942

-143.334

-25.161

0.055

86.868

29.0

-27.131

0.044

110.745

-0.550

0.939

-148.819

-0.546

0.939

-148.784

-22.722

0.073

68.734

30.0

-26.430

0.048

123.049

-0.576

0.936

-154.323

-0.582

0.935

-154.356

-21.650

0.083

61.896

31.0

-27.171

0.044

141.654

-0.614

0.932

-160.111

-0.612

0.932

-160.110

-21.300

0.086

51.421

32.0

-27.702

0.041

157.497

-0.643

0.929

-165.730

-0.640

0.929

-165.797

-20.211

0.098

37.365

33.0

-27.412

0.043

175.942

-0.665

0.926

-171.312

-0.664

0.926

-171.290

-19.404

0.107

18.402

34.0

-23.414

0.068

-159.594

-0.722

0.920

-177.364

-0.715

0.921

-177.358

-19.437

0.107

-1.031

35.0

-21.351

0.086

-142.243

-0.726

0.920

176.755

-0.724

0.920

176.769

-18.062

0.125

-17.686

36.0

-19.164

0.110

-145.966

-0.812

0.911

170.964

-0.814

0.911

171.148

-17.329

0.136

-32.214

37.0

-16.815

0.144

-142.957

-0.866

0.905

164.889

-0.887

0.903

165.274

-16.340

0.152

-48.123

38.0

-15.080

0.176

-138.352

-1.004

0.891

159.328

-0.935

0.898

159.556

-15.396

0.170

-62.771

39.0

-14.239

0.194

-142.217

-1.047

0.886

153.991

-1.022

0.889

154.016

-14.624

0.186

-72.930

40.0

-13.011

0.224

-143.357

-1.124

0.879

148.264

-1.084

0.883

148.305

-13.936

0.201

-85.368

5

S21

S12

S22

VMMK-3313 Biasing Information

Biasing and Operation

The VMMK-3313 is a 3 terminal device consisting of a

“through” 50 ohm line connecting directly between the RF

Input and RF Output ports and a directional coupler with a

full wave detector that provides a DC output proportional

to RF power input. As with any high frequency device,

good grounding is required on the common port under

the device for it to produce low loss in the “through” mode.

A suggested PCB layout with appropriate grounding will

be cover later in this application section.

values chosen for the frequency of operation. All SMT

components are recommended to be no larger than 0402

size. Nominal bias voltage of 1.5 V or 0.14 mA is required

for proper operation. Biasing on the input is by a way of a

large value resistor R1. Its value can be computed using

the following equation:

With only 3 terminals available, the DC bias and detected

voltage are internally DC coupled to the input and output

terminals respectively. The key to successful operation

of the VMMK-3313 is the use of low loss bias decoupling

networks connected to both the RF Input and the RF

Output ports. Figure 7 shows a simple biasing circuit.

Detected DC voltage is extracted on the output by a way

of a large value resistor R2, in the range of 10 kΩ. Bypassing

capacitors C3 and C4 are needed to prevent RF influence

on the dc lines. Suggested value for bypass capacitors is

1 pF.

The bias decoupling networks provide a low loss AC

coupled RF path to the device, a means of biasing the

device on the input, and a means of extracting the detected

voltage on the output of the device. The detector needs

2 DC blocking caps, C1 and C2, on the input and output

ports. This can be accomplished by printing coupled lines

on the PCB or using SMT capacitors (ATC 600 series) with

C1

C2

RFin

RFout

R1

where Vb is the supply voltage.

At zero RF input power, and at 1.5 V supply bias, a nominal

63 mV offset voltage appears at the detected output port.

The internal output source resistance for the detector is

approximately 20 kΩ. Resistor R3 can be used as an

external load resistor for the detector. Its value can be

optimized for the desired Vout vs. RF input curve.

Figure 8 shows a VMMK-3313 characterization PCB used

to obtain the Vdet vs. Input Power characterization data

from 15 to 33 GHz. For ease in broadband characterization, two external 45 MHz – 50 GHz Bias Networks (HP

11612B) were used.

R2

Vb

Vdet

detector

bias

C3

C4

Component

Description

C1, C2

0.2 pF to 0.4 pF

(ATC 600 or printed coupled lines)

R1

(Vb -1.5) / 0.00014 Ω

R2

10 kΩ

C3, C4

1 pF

R3

External load resistor (optional)

Figure 7. Biasing the VMMK-3313 Detector Module

6

R1 = (Vb -1.5)/0.00014

R3

Figure 8. VMMK-3313 Characterization Board

S Parameter Measurements

ESD Precautions

The S-parameters are measured on a 0.016 inch thick

RO4003 printed circuit test board, using 300 mm G-S-G

(ground signal ground) probes. Coplanar waveguide is

used to provide a smooth transition form the probes to

the device under test. The presence of the ground plane

on top of the test board results in excellent grounding

at the device under test. A combination of SOLT (Short –

Open – Load – Thru) and TRL (Thru – Reflect – Line) calibration techniques are used to correct for the effects of

the test board, resulting in accurate device S parameters.

Note: These devices are ESD sensitive. The following precautions are strongly recommended. Ensure that an ESD

approved carrier is used when die are transported from

one destination to another. Personal grounding is to be

worn at all times when handling these devices. For more

detail, refer to Avago Application Note A004R: Electrostatic Discharge Damage and Control.

Package and Assembly Notes

For detailed description of the device package and

assembly notes, please refer to Application Note 5378.

Ordering Information

Part Number

Devices Per

Container

Container

VMMK-3313-BLKG

100

Antistatic Bag

VMMK-3313-TR1G

5000

7” Reel

VMMK-3313-TR2G

1000

7” Reel

Package Dimension Outline

D

E

A

Dimensions

Symbol

Min (mm)

Max (mm)

E

0.500

0.585

D

1.004

1.085

A

0.225

0.275

Note:

All dimensions are in mm

Reel Orientation

Device Orientation

REEL

USER FEED DIRECTION

4 mm

Notes:

“T” = Device Code

“Y” = Month Code

• TY

TOP VIEW

• TY

7

CARRIER

TAPE

• TY

• TY

USER

FEED

DIRECTION

8 mm

END VIEW

Tape Dimensions

T

Do

Note: 1

Po

B

A

A

P1

Scale 5:1

Bo

W

Note: 2

F

E

5° (Max)

B

D1

BB SECTION

Note: 2

P2

Ao

R0.1

5° (Max)

Ko

Ao = 0.73±0.05 mm

Scale 5:1

Bo = 1.26±0.05 mm

AA SECTION

mm

Ko = 0.35 +0.05

+0

Unit: mm

Symbol

Spec.

K1

Po

P1

P2

Do

D1

E

F

10Po

W

T

–

4.0±0.10

4.0±0.10

2.0±0.05

1.55±0.05

0.5±0.05

1.75±0.10

3.50±0.05

40.0±0.10

8.0±0.20

0.20±0.02

Notice:

1. 10 Sprocket hole pitch cumulative tolerance is ±0.1 mm.

2. Pocket position relative to sprocket hole measured as true position

of pocket not pocket hole.

3. Ao & Bo measured on a place 0.3 mm above the bottom of the

pocket to top surface of the carrier.

4. Ko measured from a plane on the inside bottom of the pocket to

the top surface of the carrier.

5. Carrier camber shall be not than 1 m per 100 mm through a length

of 250 mm.

For product information and a complete list of distributors, please go to our web site:

www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries.

Data subject to change. Copyright © 2005-2012 Avago Technologies. All rights reserved.

AV02-2916EN - December 26, 2012