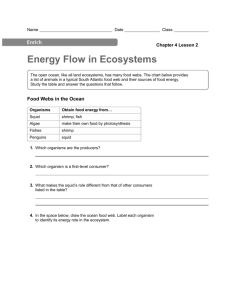

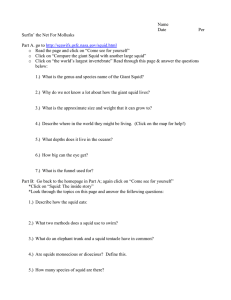

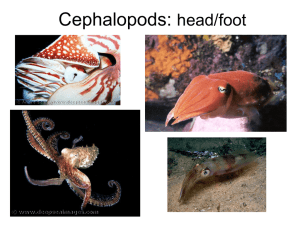

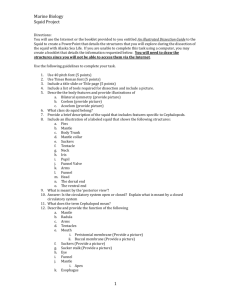

Document

advertisement