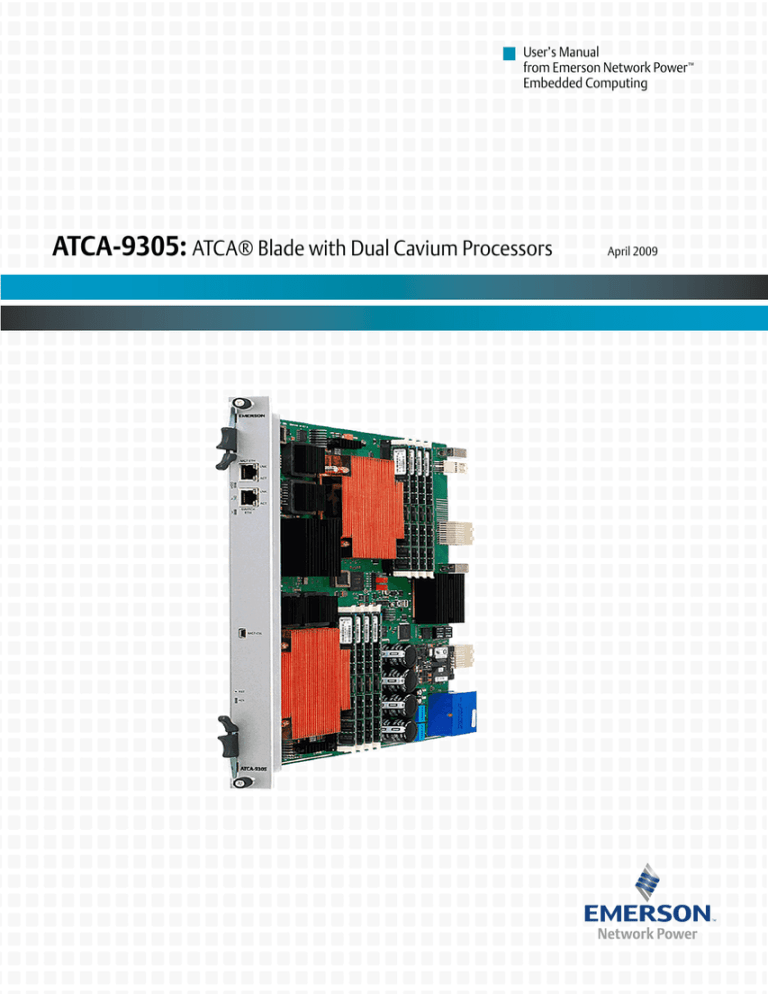

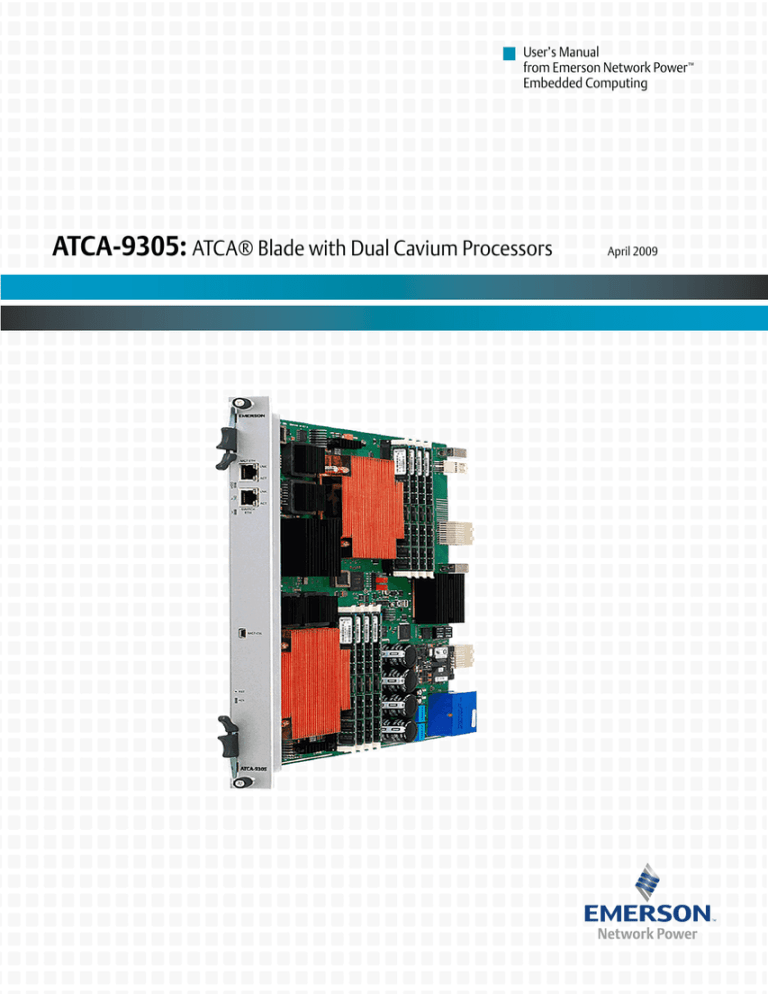

User’s Manual

from Emerson Network Power ™

Embedded Computing

ATCA-9305: ATCA® Blade with Dual Cavium Processors

April 2009

The information in this manual has been checked and is believed to be accurate and reliable.

HOWEVER, NO RESPONSIBILITY IS ASSUMED BY EMERSON NETWORK POWER, EMBEDDED

COMPUTING FOR ITS USE OR FOR ANY INACCURACIES. Specifications are subject to change

without notice. EMERSON DOES NOT ASSUME ANY LIABILITY ARISING OUT OF USE OR

OTHER APPLICATION OF ANY PRODUCT, CIRCUIT, OR PROGRAM DESCRIBED HEREIN. This

document does not convey any license under Emerson patents or the rights of others.

Emerson. Consider It Solved is a trademark, and Business-Critical Continuity, Emerson Network Power, and the Emerson Network Power logo are trademarks and service marks of

Emerson Network Power, Embedded Computing, Inc.

© 2009 Emerson Network Power, Embedded Computing, Inc.

Revision Level:

Principal Changes:

Date:

10009109-00

Original release

January 2009

10009109-01

Added “GR-1089-CORE Standard” on page -i

Updated “Product Certification” on page 1-4

April 2009

Copyright © 2009 Emerson Network Power, Embedded Computing, Inc. All rights reserved.

Regulatory Agency Warnings & Notices

The Emerson ATCA-9305 meets the requirements set forth by the Federal Communications

Commission (FCC) in Title 47 of the Code of Federal Regulations. The following information

is provided as required by this agency.

This device complies with part 15 of the FCC Rules. Operation is subject to the following two

conditions: (1) This device may not cause harmful interference, and (2) this device must

accept any interference received, including interference that may cause undesired operation.

FCC RULES AND REGULATIONS — PART 15

This equipment has been tested and found to comply with the limits for a Class A digital

device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses and can radiate radio frequency energy

and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely

to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

Caution: Making changes or modifications to the ATCA-9305 hardware without the explicit consent

of Emerson Network Power could invalidate the user’s authority to operate this equipment.

!

EMC COMPLIANCE

The electromagnetic compatibility (EMC) tests used an ATCA-9305 model that includes a

front panel assembly from Emerson Network Power.

Caution: For applications where the ATCA-9305 is provided without a front panel, or where the front

panel has been removed, your system chassis/enclosure must provide the required

!

electromagnetic interference (EMI) shielding to maintain EMC compliance.

GR-1089-CORE STANDARD

Caution: WARNING: The intra-building port(s) of the equipment or subassembly is suitable for

connection to intrabuilding or unexposed wiring or cabling only. The intra-building port(s)

!

of the equipment or subassembly MUST NOT be metallically connected to interfaces that

connect to the OSP or its wiring. These interfaces are designed for use as intra-building

interfaces only (Type 2 or Type 4 ports as described in GR-1089-CORE, Issue 4) and require

isolation from the exposed OSP cabling. The addition of Primary Protectors is not sufficient

protection in order to connect these interfaces metallically to OSP wiring.

10009109-01

ATCA-9305 User’s Manual

i

Regulatory Agency Warnings & Notices

(continued)

EC Declaration of Conformity

According to EN 45014:1998

Manufacturer’s Name:

Emerson Network Power

Embedded Computing

Manufacturer’s Address:

8310 Excelsior Drive

Madison, Wisconsin 53717

Declares that the following product, in accordance with the requirements of 2004/108/EEC, EMC

Directive and 1999/5/EC, RTTE Directive and their amending directives,

Product:

ATCA Blade

Model Name/Number:

ATCA-9305/10009986-xx

has been designed and manufactured to the following specifications:

EN55022:1998 Information Technology Equipment, Radio disturbance characteristics, Limits and

methods of measurement

EN55024:1998 Information Technology Equipment, Immunity characteristics, Limits and methods

of measurement

EN300386 V.1.3.2:2003-5 Electromagnetic compatibility and radio spectrum matters (ERM);

Telecommunication network equipment; EMC requirements

As manufacturer we hereby declare that the product named above has been designed to comply

with the relevant sections of the above referenced specifications. This product complies with the

essential health and safety requirements of the EMC Directive and RTTE Directive. We have an internal production control system that ensures compliance between the manufactured products and

the technical documentation.

Bill Fleury

Compliance Engineer

Issue date: April 7, 2009

ii

ATCA-9305 User’s Manual

10009109-01

Regulatory Agency Warnings & Notices

10009109-01

(continued)

ATCA-9305 User’s Manual

iii

Regulatory Agency Warnings & Notices

iv

ATCA-9305 User’s Manual

10009109-01

(continued)

Contents

1 Overview

Components and Features . . . . . . . . . . . 1-1

Functional Overview . . . . . . . . . . . . . . . . 1-3

Additional Information . . . . . . . . . . . . . . 1-4

Product Certification . . . . . . . . . . . . . 1-4

RoHS Compliance. . . . . . . . . . . . . . . . 1-5

Terminology and Notation . . . . . . . . 1-6

Technical References. . . . . . . . . . . . . 1-6

2 Setup

Electrostatic Discharge . . . . . . . . . . . . . . 2-1

ATCA-9305 Circuit Board . . . . . . . . . . . . 2-1

Connectors . . . . . . . . . . . . . . . . . . . . . 2-7

Configuration Header . . . . . . . . . . . . 2-8

ATCA-9305 Setup . . . . . . . . . . . . . . . . . . . 2-8

Power Requirements . . . . . . . . . . . . . 2-9

Environmental Considerations . . . . 2-9

Hot Swap . . . . . . . . . . . . . . . . . . . . . .2-10

Insert a board: . . . . . . . . . 2-11

Remove a board: . . . . . . . 2-11

Troubleshooting . . . . . . . . . . . . . . . . . . . 2-11

Technical Support . . . . . . . . . . . . . .2-11

Product Repair . . . . . . . . . . . . . . . . .2-12

Comments and Suggestions . . . . .2-13

3 Cavium Processor Complex

Cavium CN5860 Processor . . . . . . . . . . . 3-1

Cavium Memory Map . . . . . . . . . . . . 3-2

PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

CN5860 Boot Over PCI . . . . . . . . . . . 3-3

Cavium Reset . . . . . . . . . . . . . . . . . . . 3-4

Cavium Ethernet. . . . . . . . . . . . . . . . . . . . 3-5

Cavium Monitor . . . . . . . . . . . . . . . . . . . . 3-6

Start-up Display . . . . . . . . . . . . . . . . . 3-6

Power-up/Reset Sequence . . . . . . . . 3-6

Diagnostic Tests During Power-up and

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

POST Diagnostic Results . . . . . . 3-7

Cavium Environment Variables . . . . 3-8

Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

DDR2 SDRAM . . . . . . . . . . . . . . . . . . . 3-9

RLDRAM . . . . . . . . . . . . . . . . . . . . . . . . 3-9

I2C EEPROM. . . . . . . . . . . . . . . . . . . . . 3-9

Flash, 512 KB x 8 . . . . . . . . . . . . . . . .3-10

Flash, 4 MB x 16 . . . . . . . . . . . . . . . .3-10

10009109-01

StratixGX Interconnect . . . . . . . . . . . . . 3-10

PLD Registers . . . . . . . . . . . . . . . . . . 3-10

Data Registers . . . . . . . . . . . . . 3-10

Address Registers . . . . . . . . . . 3-12

Control Register. . . . . . . . . . . . 3-12

Version Register. . . . . . . . . . . . 3-13

Scratch Register . . . . . . . . . . . . 3-13

Headers and Connectors. . . . . . . . . . . . 3-14

COP/JTAG Headers . . . . . . . . . . . . . 3-14

Console Serial Ports (optional) . . . 3-15

4 Management Complex

MPC8548 Processor. . . . . . . . . . . . . . . . . .4-2

MPC8548 Memory Map . . . . . . . . . . 4-2

Chip Selects . . . . . . . . . . . . . . . . . . . . 4-5

Reset Diagram . . . . . . . . . . . . . . . . . . 4-6

Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

SDRAM. . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

512 KB x 8 (optional). . . . . . . . . 4-7

4M x 16 . . . . . . . . . . . . . . . . . . . . 4-7

1 GB x 16 . . . . . . . . . . . . . . . . . . . 4-8

64 MB x 16. . . . . . . . . . . . . . . . . . 4-8

PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

PCI Express . . . . . . . . . . . . . . . . . . . . . 4-8

I2C Interface . . . . . . . . . . . . . . . . . . . . . . . .4-9

Management Processor Header and Serial

Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

JTAG/COP Interface (optional) . . . . 4-9

Serial Debug Port. . . . . . . . . . . . . . . 4-10

5 Management Processor

CPLD

MPC8548 PLD Register Summary . . . . . .5-1

Product ID . . . . . . . . . . . . . . . . . . . . . . 5-2

Hardware Version . . . . . . . . . . . . . . . 5-2

PLD Version. . . . . . . . . . . . . . . . . . . . . 5-3

PLL Reset Configuration . . . . . . . . . . 5-3

Hardware Configuration 0 . . . . . . . . 5-3

Jumper Settings . . . . . . . . . . . . . . . . . 5-4

LED . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Reset Event . . . . . . . . . . . . . . . . . . . . . 5-5

Reset Command 1. . . . . . . . . . . . . . . 5-5

Reset Command 2. . . . . . . . . . . . . . . 5-6

Reset Command 3. . . . . . . . . . . . . . . 5-6

ATCA-9305 User’s Manual

v

Contents

(continued)

Reset Command 4 . . . . . . . . . . . . . . . 5-7

Reset Command 5 . . . . . . . . . . . . . . . 5-7

Reset Command Sticky #1 . . . . . . . . 5-7

Reset Command Sticky #2 . . . . . . . . 5-8

Boot Device Redirection . . . . . . . . . . 5-8

Miscellaneous Control. . . . . . . . . . . . 5-9

Low Frequency Timer 1 and 2 . . . . . 5-9

RTM GPIO State . . . . . . . . . . . . . . . .5-10

RTM GPIO Control . . . . . . . . . . . . . .5-10

RTM Status . . . . . . . . . . . . . . . . . . . .5-10

Cavium 1 C_MUL Clock Divisor Control

5-11

Cavium 2 C_MUL Clock Divisor Control

5-11

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . .5-12

Cavium GPIO Control . . . . . . . . . . .5-12

Cavium GPIO Data Out . . . . . . . . . .5-13

Cavium GPIO Data In . . . . . . . . . . . .5-13

IPMP/IPMC GPIO Control . . . . . . . .5-14

LPC Bus Control . . . . . . . . . . . . . . . .5-14

LPC Data. . . . . . . . . . . . . . . . . . . . . . .5-14

Serial IRQ Interrupt 1 . . . . . . . . . . .5-15

Serial IRQ Interrupt 2 . . . . . . . . . . .5-15

6 Ethernet Interface

Broadcom BCM56802 Switch . . . . . . . . .6-1

Ethernet Switching. . . . . . . . . . . . . . . . . . .6-1

Ethernet Transceivers . . . . . . . . . . . . 6-2

Ethernet Switch Ports . . . . . . . . . . . . 6-2

VLAN Setup . . . . . . . . . . . . . . . . . . . . . 6-3

MPC8548 Management Processor Ethernet

Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

Front Panel Ethernet Ports . . . . . . . . 6-4

7 System Management

IPMC Overview . . . . . . . . . . . . . . . . . . . . . .7-1

IPMI Messaging . . . . . . . . . . . . . . . . . . . . . .7-2

IPMI Completion Codes . . . . . . . . . . 7-4

IPMB Protocol . . . . . . . . . . . . . . . . . . . . . . .7-5

SIPL Protocol . . . . . . . . . . . . . . . . . . . . . . . .7-6

Message Bridging . . . . . . . . . . . . . . . . . . . .7-7

Standard Commands. . . . . . . . . . . . . . . . .7-9

OEM Boot Options . . . . . . . . . . . . . . . . . 7-11

IPMC Watchdog Timer Commands. . . 7-12

Watchdog Timer Actions . . . . . . . .7-12

vi

ATCA-9305 User’s Manual

10009109-01

Watchdog Timer Use Field and

Expiration Flags . . . . . . . . . . . . . . . . 7-12

Using the Timer Use Field and

Expiration Flags . . . . . . . . . . . . 7-13

Watchdog Timer Event Logging . . 7-13

Monitor Support for Watchdog

Timer . . . . . . . . . . . . . . . . . . . . . 7-13

Reset Watchdog Timer Command7-14

Set Watchdog Timer Command. . 7-14

Get Watchdog Timer Command . 7-16

FRU LEDs . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

Get FRU LED Properties Command7-19

Get LED Color Capabilities Command .

7-19

Set FRU LED State Command . . . . 7-21

Get FRU LED State Command . . . . 7-22

Vendor Commands . . . . . . . . . . . . . . . . 7-24

Get Status . . . . . . . . . . . . . . . . . . . . . 7-25

Get Serial Interface Properties . . . 7-27

Set Serial Interface Properties . . . . 7-28

Get Debug Level . . . . . . . . . . . . . . . 7-29

Set Debug Level . . . . . . . . . . . . . . . . 7-29

Get Hardware Address . . . . . . . . . . 7-30

Set Hardware Address . . . . . . . . . . 7-30

Get Handle Switch. . . . . . . . . . . . . . 7-31

Set Handle Switch . . . . . . . . . . . . . . 7-31

Get Payload Communication Time-Out

7-32

Set Payload Communication Time-Out

7-32

Enable Payload Control . . . . . . . . . 7-32

Disable Payload Control . . . . . . . . . 7-33

Reset IPMC . . . . . . . . . . . . . . . . . . . . 7-33

Hang IPMC . . . . . . . . . . . . . . . . . . . . 7-33

Bused Resource . . . . . . . . . . . . . . . . 7-34

Bused Resource Status . . . . . . . . . . 7-34

Graceful Reset . . . . . . . . . . . . . . . . . 7-35

Diagnostic Interrupt Results . . . . . 7-36

Get Payload Shutdown Time-Out. 7-36

Set Payload Shutdown Time-Out . 7-37

Set Local FRU LED State . . . . . . . . . 7-38

Get Local FRU LED State . . . . . . . . . 7-39

Update Discrete Sensor . . . . . . . . . 7-40

Update Threshold Sensor. . . . . . . . 7-40

Boot Device Redirection (BDR) . . . . . . 7-41

Message Listeners . . . . . . . . . . . . . . . . . 7-43

Add Message Listener. . . . . . . . . . . 7-44

Remove Message Listener . . . . . . . 7-44

Contents

(continued)

Get Message Listener List . . . . . . . .7-45

System Firmware Progress Sensor . . . 7-45

Entities and Entity Associations . . . . . . 7-46

Sensors and Sensor Data Records . . . . 7-48

FRU Inventory . . . . . . . . . . . . . . . . . . . . . 7-50

E-Keying . . . . . . . . . . . . . . . . . . . . . . . . . . 7-51

Base Point-to-Point Connectivity .7-52

HPM.1 Firmware Upgrade. . . . . . . . . . . 7-52

HPM.1 Reliable Field Upgrade

Procedure . . . . . . . . . . . . . . . . . . . . .7-53

IPMC Headers . . . . . . . . . . . . . . . . . . . . . 7-53

8 Back Panel Connectors

Zone 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

Zone 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

Zone 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-3

9 Management Processor

Monitor

Command-Line Features. . . . . . . . . . . . . .9-1

Basic Operation. . . . . . . . . . . . . . . . . . . . . .9-3

Power-up/Reset Sequence . . . . . . . . 9-3

POST Diagnostic Results . . . . . . . . . . 9-4

Monitor SDRAM Usage . . . . . . . . . . . 9-5

Monitor Recovery and Updates . . . . . . . .9-5

Recovering the Monitor . . . . . . . . . . 9-6

Resetting Environment Variables . . 9-6

Updating the Monitor via TFTP . . . . 9-6

Monitor Command Reference . . . . . . . . .9-7

Command Syntax. . . . . . . . . . . . . . . . 9-7

Command Help . . . . . . . . . . . . . . . . . 9-8

Typographic Conventions . . . . . . . . 9-8

Boot Commands. . . . . . . . . . . . . . . . . . . . .9-8

bootd . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

bootelf . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

bootm . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

bootp . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

bootv . . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

bootvx . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

dhcp . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

rarpboot. . . . . . . . . . . . . . . . . . . . . . .9-10

tftpboot . . . . . . . . . . . . . . . . . . . . . . .9-10

File Load Commands . . . . . . . . . . . . . . . 9-11

loadb . . . . . . . . . . . . . . . . . . . . . . . . .9-11

loads . . . . . . . . . . . . . . . . . . . . . . . . . .9-11

Memory Commands . . . . . . . . . . . . . . . 9-11

10009109-01

cmp . . . . . . . . . . . . . . . . . . . . . . . . . . 9-12

cp . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-12

find . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-12

md . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-12

mm. . . . . . . . . . . . . . . . . . . . . . . . . . . 9-13

nm . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-13

mw . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-13

Flash Commands . . . . . . . . . . . . . . . . . . 9-14

cp . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-14

erase . . . . . . . . . . . . . . . . . . . . . . . . . 9-14

flinfo. . . . . . . . . . . . . . . . . . . . . . . . . . 9-14

protect. . . . . . . . . . . . . . . . . . . . . . . . 9-15

EEPROM/I2C Commands . . . . . . . . . . . 9-15

eeprom . . . . . . . . . . . . . . . . . . . . . . . 9-15

icrc32 . . . . . . . . . . . . . . . . . . . . . . . . . 9-16

iloop . . . . . . . . . . . . . . . . . . . . . . . . . . 9-16

imd . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-16

imm . . . . . . . . . . . . . . . . . . . . . . . . . . 9-16

imw . . . . . . . . . . . . . . . . . . . . . . . . . . 9-16

inm . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-16

iprobe . . . . . . . . . . . . . . . . . . . . . . . . 9-17

IPMC Commands . . . . . . . . . . . . . . . . . . 9-17

bootdev. . . . . . . . . . . . . . . . . . . . . . . 9-17

fru . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-17

fruinit . . . . . . . . . . . . . . . . . . . . . . . . . 9-18

fruled . . . . . . . . . . . . . . . . . . . . . . . . . 9-18

ipmchpmfw . . . . . . . . . . . . . . . . . . . 9-18

sensor . . . . . . . . . . . . . . . . . . . . . . . . 9-18

Environment Parameter Commands . 9-19

printenv. . . . . . . . . . . . . . . . . . . . . . . 9-19

saveenv . . . . . . . . . . . . . . . . . . . . . . . 9-19

setenv . . . . . . . . . . . . . . . . . . . . . . . . 9-19

Test Commands . . . . . . . . . . . . . . . . . . . 9-20

diags. . . . . . . . . . . . . . . . . . . . . . . . . . 9-20

mtest . . . . . . . . . . . . . . . . . . . . . . . . . 9-20

um . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-20

Other Commands. . . . . . . . . . . . . . . . . . 9-20

autoscr. . . . . . . . . . . . . . . . . . . . . . . . 9-20

base . . . . . . . . . . . . . . . . . . . . . . . . . . 9-20

bdinfo . . . . . . . . . . . . . . . . . . . . . . . . 9-21

coninfo . . . . . . . . . . . . . . . . . . . . . . . 9-21

crc32 . . . . . . . . . . . . . . . . . . . . . . . . . 9-21

date . . . . . . . . . . . . . . . . . . . . . . . . . . 9-21

echo . . . . . . . . . . . . . . . . . . . . . . . . . . 9-21

enumpci . . . . . . . . . . . . . . . . . . . . . . 9-21

go . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-21

help . . . . . . . . . . . . . . . . . . . . . . . . . . 9-22

ATCA-9305 User’s Manual

vii

Contents

(continued)

iminfo . . . . . . . . . . . . . . . . . . . . . . . . .9-22

isdram . . . . . . . . . . . . . . . . . . . . . . . .9-22

loop. . . . . . . . . . . . . . . . . . . . . . . . . . .9-22

memmap . . . . . . . . . . . . . . . . . . . . . .9-22

moninit . . . . . . . . . . . . . . . . . . . . . . .9-22

pci . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-23

phy . . . . . . . . . . . . . . . . . . . . . . . . . . .9-23

ping. . . . . . . . . . . . . . . . . . . . . . . . . . .9-24

reset . . . . . . . . . . . . . . . . . . . . . . . . . .9-24

run. . . . . . . . . . . . . . . . . . . . . . . . . . . .9-24

script. . . . . . . . . . . . . . . . . . . . . . . . . .9-24

showmac . . . . . . . . . . . . . . . . . . . . . .9-24

showpci . . . . . . . . . . . . . . . . . . . . . . .9-24

viii

ATCA-9305 User’s Manual

10009109-01

sleep. . . . . . . . . . . . . . . . . . . . . . . . . . 9-25

switch_reg . . . . . . . . . . . . . . . . . . . . 9-25

version . . . . . . . . . . . . . . . . . . . . . . . . 9-25

vlan. . . . . . . . . . . . . . . . . . . . . . . . . . . 9-25

MPC8548 Environment Variables . . . . 9-26

Troubleshooting. . . . . . . . . . . . . . . . . . . 9-28

Download Formats. . . . . . . . . . . . . . . . . 9-28

Binary. . . . . . . . . . . . . . . . . . . . . . . . . 9-29

Motorola S-Record . . . . . . . . . . . . . 9-29

10 Acronyms

Figures

Figure 1-1:

General System Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Figure 2-1:

ATCA-9305 Front Panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2:

Component Map, Top (Rev. 01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Figure 2-3:

Component Map, Bottom (Rev. 01). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Figure 2-4:

LED, Fuse and Switch Locations, Top . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Figure 2-5:

LED and Switch Locations, Bottom. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Figure 2-6:

Configuration Header, J9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 2-7:

Air Flow Graph . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Figure 2-8:

Serial Number and Product ID on Top Side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Figure 3-1:

Cavium Processor Complex Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Figure 3-2:

CN5860 Reset Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Figure 3-3:

Example Cavium CN5860 Monitor Start-up Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Figure 3-4:

Power-up/Reset CN5860 Boot Sequence Flowchart. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Figure 4-1:

MPC8548 Management Processor Complex Block Diagram. . . . . . . . . . . . . . . . . . . . . 4-1

Figure 4-2:

MPC8548 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Figure 4-3:

MPC8548 Reset Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Figure 6-1:

Ethernet Switching Interface Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Figure 7-1:

IPMC Connections Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Figure 7-2:

Extension Command Request Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Figure 7-3:

Extension Command Response Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Figure 7-4:

Boot Device Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-42

Figure 7-5:

Boot Redirection Control Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-42

Figure 7-6:

IPMB Entity Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-47

Figure 8-1:

Zone 1 Connector, P10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

Figure 8-2:

Zone 2 and 3 Connectors; J23, J30-J31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

Figure 8-3:

Zone 3 Connector, J33 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

Figure 9-1:

Example MPC8548 Monitor Start-up Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

Figure 9-2:

Power-up/Reset Sequence Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

10009109-01

ATCA-9305 User’s Manual

ix

(blank page)

x

ATCA-9305 User’s Manual

10009109-01

Tables

Table 1-1:

Regulatory Agency Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Table 1-2:

Technical References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Table 2-1:

Circuit Board Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Table 2-2:

Typical Power Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Table 2-3:

Environmental Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Table 3-1:

CN5860 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Table 3-2:

Cavium Address Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table 3-3:

Ethernet Port Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Table 3-4:

POST Diagnostic Results–Bit Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Table 3-5:

Standard Cavium Environment Variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Table 3-6:

Cavium NVRAM Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Table 3-7:

CN5860 Processor COP/JTAG Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Table 3-8:

CN5860 Processor Debug Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Table 4-1:

MPC8548 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Table 4-2:

MPC8548 Address Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Table 4-3:

Device Chip Selects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Table 4-4:

PCI Device Interrupts and ID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Table 4-5:

I2C Device Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Table 4-6:

MPC8548 NVRAM Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Table 4-7:

Serial Debug Connector, P2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Table 4-8:

Serial Debug Connector, P7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

Table 5-1:

PLD Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Table 5-2:

Low Frequency Timer Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Table 6-1:

Ethernet Switch Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Table 6-2:

VLAN Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Table 6-3:

Ethernet Port Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

Table 6-4:

Front Panel Ethernet Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

Table 7-1:

Network Function Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Table 7-2:

Completion Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 7-3:

Format for IPMI Request Message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 7-4:

Format for IPMI Response Message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Table 7-5:

IPMC IPMI Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Table 7-6:

Emerson Boot Option Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

Table 7-7:

IPMC Watchdog Timer Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

Table 7-8:

Reset Watchdog Timer Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

Table 7-9:

Set Watchdog Timer Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

Table 7-10:

Get Watchdog Timer Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

Table 7-11:

FRU LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

Table 7-12:

Get FRU LED Properties Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

Table 7-13:

Get LED Color Capabilities Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

10009109-01

ATCA-9305 User’s Manual

xi

Tables

(continued)

Table 7-14:

xii

ATCA-9305 User’s Manual

Set FRU LED State Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

Table 7-15:

Get FRU LED State Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-22

Table 7-16:

Vendor Command Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-24

Table 7-17:

Get Status Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-25

Table 7-18:

Get Serial Interface Properties Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-27

Table 7-19:

Set Serial Interface Properties Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-28

Table 7-20:

Get Debug Level Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-29

Table 7-21:

Set Debug Level Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-29

Table 7-22:

Get Hardware Address Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-30

Table 7-23:

Set Hardware Address Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-30

Table 7-24:

Get Handle Switch Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-31

Table 7-25:

Set Handle Switch Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-31

Table 7-26:

Get Payload Communication Time-Out Command . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32

Table 7-27:

Set Payload Communication Time-Out Command . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32

Table 7-28:

Enable Payload Control Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32

Table 7-29:

Disable Payload Control Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-33

Table 7-30:

Reset IPMC Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-33

Table 7-31:

Hang IPMC Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-33

Table 7-32:

Bused Resource Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-34

Table 7-33:

Bused Resource Status Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35

Table 7-34:

Graceful Reset Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-36

Table 7-35:

Diagnostic Interrupt Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-36

Table 7-36:

Get Payload Shutdown Time-Out Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-37

Table 7-37:

Set Payload Shutdown Time-Out Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-37

Table 7-38:

Set Local FRU LED State Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-38

Table 7-39:

Get Local FRU LED State Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-39

Table 7-40:

Update Discrete Sensor Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-40

Table 7-41:

Update Threshold Sensor Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-40

Table 7-42:

Add Message Listener Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-44

Table 7-43:

Remove Message Listener Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-44

Table 7-44:

Get Message Listener List Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-45

Table 7-45:

Update System Firmware Progress Sensor Command . . . . . . . . . . . . . . . . . . . . . . . . . 7-46

Table 7-46:

IPMI Threshold Sensors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-48

Table 7-47:

IPMI Discrete Sensors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-48

Table 7-48:

Event Message Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-49

Table 7-49:

FRU Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-50

Table 7-50:

Link Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-52

Table 7-51:

IPMP CPLD JP1 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-53

Table 7-52:

IPMP EIA-232 P4 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-53

Table 8-1:

Zone 1 Connector, P10 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

Table 8-2:

Zone 2 Connector, J23 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

10009109-01

Tables

(continued)

Table 8-3:

Zone 3 Connector, J30 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

Table 8-4:

Zone 3 Connector, J31 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

Table 8-5:

Zone 3 Connector, J33 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

Table 9-1:

Debug LED Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

Table 9-2:

POST Diagnostic Results–Bit Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

Table 9-3:

Monitor Address per Flash Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

Table 9-4:

Static IP Ethernet Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

Table 9-5:

DHCP Ethernet Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

Table 9-6:

Standard Environment Variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-26

Table 9-7:

Optional Environment Variables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-28

10009109-01

ATCA-9305 User’s Manual

xiii

(blank page)

xiv

ATCA-9305 User’s Manual

10009109-01

Registers

Register 3-1:

Data 31:24 (0x0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Register 3-2:

Data 23:16 (0x1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Register 3-3:

Data 15:8 (0x2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Register 3-4:

Data 7:0 (0x3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Register 3-5:

Address 9:8 (0x4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Register 3-6:

Address 7:0 (0x5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Register 3-7:

Control (0x6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Register 3-8:

Version (0x7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

Register 3-9:

Scratch (0x8-0x3F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

Register 5-1:

Product ID (0x00) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Register 5-2:

Hardware Version (0x04) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Register 5-3:

PLD Version (0x08) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Register 5-4:

PLL Reset Configuration (0x0C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Register 5-5:

Hardware Configuration 0 (0x10). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Register 5-6:

Jumper Settings (0x18). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Register 5-7:

LED (0x1C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Register 5-8:

Reset Event (0x20) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Register 5-9:

Reset Command 1 (0x24) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Register 5-10: Reset Command 2 (0x28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Register 5-11: Reset Command 3 (0x2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Register 5-12: Reset Command 4 (0x30) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Register 5-13: Reset Command 5 (0x34) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Register 5-14: Reset Command Sticky #1 (0x38) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Register 5-15: Reset Command Sticky #2 (0x3C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Register 5-16: Boot Device Redirection (0x50) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Register 5-17: Miscellaneous Control (0x54) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Register 5-18: RTM GPIO State (0x60). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Register 5-19: RTM GPIO Control (0x64). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Register 5-20: RTM Control (0x68). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Register 5-21: Cavium 1 C_MULL Clock Divisor Control (0x70) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Register 5-22: Cavium 2 C_MULL Clock Divisor Control (0x74) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Register 5-23: JTAG (0x78). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Register 5-24: Cavium GPIO Control (0x80) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Register 5-25: Cavium GPIO Data Out (0x84) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Register 5-26: Cavium GPIO Data In (0x88) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Register 5-27: IPMP/IPMC GPIO Control (0x8C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

Register 5-28: LPC Bus (0xD0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

Register 5-29: LPC Data (0xD4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

Register 5-30: Serial IRQ Interrupts 1 (0xD8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

Register 5-31: Serial IRQ Interrupts 2 (0xDC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

10009109-01

ATCA-9305 User’s Manual

i

(blank page)

ii

ATCA-9305 User’s Manual

10009109-01

Section 1

Overview

The ATCA-9305 is an Advanced Telecom Computing Architecture (AdvancedTCA®, ATCA®)

blade based on dual Cavium OCTEON™ CN5860 processors and the Freescale™ Semiconductor MPC8548 management processor. This blade is targeted at security and packet-processing applications in the wireless and transport market segments. These markets include

data-plane packet-processor, security co-processor, video compression, and pattern matching.

The ATCA-9305 complies with the SCOPE recommended profile for central office ATCA systems, PICMG® 3.0 ATCA mechanical specifications, E-keying, and Hot Swap.

COMPONENTS AND FEATURES

The following is a brief summary of the ATCA-9305 hardware components and features:

Cavium Processor : The Cavium CN5860 processor is a highly programmable, high-performance 16-core architecture operating up to 800 MHz.

Management Processor:

The Freescale PowerQUICC™ III MPC8548 processor is a 32-bit enhanced e500 core operating at 1 GHz.

Ethernet Switch: The Broadcom® BCM56802 is a sixteen-port, 10 GbE switch which interconnects the processors using SPI to XAUI™ bridges. The functionality includes both 10-Gbps XAUI and 1Gbps SGMII PHY interfaces.

Stratix™ GX Bridge: There are two packet routing Altera® SPI-4.2 high-speed interconnect to XAUI bridges per

CN5860 processor.

Ethernet: 10/100/1000BASE-T Ethernet ports are accessible via the front panel RJ45 connectors and

through the base channel on the back panel. The 10 GbE ports route to the back panel

through the fabric and RTM connectors.

Serial Port: The front panel serial port (MGT CSL) connects to the MPC8548 management processor.

System Management: This product supports an Intelligent Platform Management Controller (IPMC) based on a

proprietary BMR-H8S-AMCc® reference design from Pigeon Point Systems. The IPMC has

an inter-integrated circuit (I2C) controller to support an Intelligent Management Platform

Bus (IPMB) that routes to the AdvancedTCA connector. The IPMB allows for features such as

remote shutdown, remote reset, payload voltage monitoring, temperature monitoring,

and access to Field Replaceable Unit (FRU) data.

PCI/PCIe: The PCI bus allows for read/write memory access between the MPC8548 processor, Ethernet switch, and Cavium processors. The four lane PCI Express® (PCIe) routes between the

MPC8548 and the optional RTM.

10009109-01

ATCA-9305 User’s Manual

1-1

Overview:

Components and Features

Real-time Clock: The STMicroelectronics M41T00S RTC provides counters for seconds, minutes, hours, day,

date, month, years, and century. The M41T00S serial interface supports I2C bus and has a

super-cap backup capable of maintaining the clock for a minimum of two hours.

Software: The Cavium CN5860 processor provides a GNU compiler that implements the MIPS64 Rel 2

instruction set in addition to the specialized instructions and a Linux® Board Specific Package (BSP) including the IP-stack optimization. The CN5860 also provides libraries that take

advantage of the chip’s hardware acceleration for certain security protocols.

RTM (optional): This blade supports a custom Rear Transition Module (RTM) with the following I/O:

• Either two or six 10GbE connections

• One x4 PCI Express port from the MPC8548

• Connections for an MMC to control Hot Swap

• MPC8548 console port

For more detailed information, see the ATCA-9305 Rear Transition Module User’s Manual.

1-2

ATCA-9305 User’s Manual

10009109-01

Overview:

Functional Overview

FUNCTIONAL OVERVIEW

The following block diagram provides a functional overview for the ATCA-9305:

Figure 1-1: General System Block Diagram

Console

RJ45

RJ45

Mag

Mag

Socketed

ROM

512KB

x8

KSL

CPLD

Console

(ENG use only)

Latched Adrs

BCM5461S BCM5461S

NAND

Flash

1GB

x 16

Adrs/Data

COP/JTAG

MPC8548

Management

Processor

P1 DDR

SDRAM

COP/

JTAG

NOR

Flash

512Mb or

64MB x 16

PQ DDR2

SDRAM

I2C

EEPROM

(ENG use only)

NOR

Flash

4M

x 16

A/D

I2C

EEPROM

Console

PCIe x4

COP/

JTAG

RTC

P2 DDR2

SDRAM

BCM5461S

I2C

I2C

EEPROM

RLDRAM

64MB

RLDRAM

64MB

RLDRAM

64MB

RLDRAM

64MB

D1_DDR2 Serial 0 PCI

Bus

I2C

IDSEL11

Cavium

SPI-0

Octeon

CN5860

Processor 1

SPI-1

Local Bus

Addr/Data

Serial 1

Socketed

ROM

512K

x8

NOR

Flash

4M

x8

PCI Bus

Serial CFG

EEPROM

3

SGMII

Stratix II GX

#1

6 XAUI

Stratix II GX

#2

5 XAUI

4

SGMII

PCI Serial 0 D1_DDR2

Bus

I2C

IDSEL12

PCI Bus

IDSEL13

XAUI 13

BCM56802

XAUI 10 Gb

Switch

SGMII

2

SGMII

1

XAUI 14

To RTM

XAUI

XAUI

8 7 11-12 15 -18

SPI-0

Stratix II GX

#4

SPI-1

Local Bus

Addr/Data

1

2

Base

P10

10G - 2 PORTS

Mag

3 2 1 0 3 2 1 0

FC2

FC1

10G Fabric

J23

10009109-01

RLDRAM

64MB

RLDRAM

64MB

Socketed

ROM

512K

x8

10G - 4 PORTS

Mag

I2C

EEPROM

Serial 1

BCM5482

IPMB

Cavium

Octeon

CN5860

Processor 2

Stratix II GX

#3

I2C

NOR

Flash

4M

x8

RLDRAM

64MB

RLDRAM

64MB

RTM RST

12V Hot Swap

RTM Console

PQ I2C

J30

J31

J33

ATCA-9305 User’s Manual

1-3

Overview:

Additional Information

ADDITIONAL INFORMATION

This section lists the ATCA-9305 hardware’s regulatory certifications and briefly discusses

the terminology and notation conventions used in this manual. It also lists general technical

references.

Mean time between failures (MTBF) has been calculated at 439,924 hours using the Telcordia SR-332, Issue 1 (Reliability Prediction for Electronic Equipment), method 2 at 30° C.

Product Certification

The ATCA-9305 hardware has been tested to comply with various safety, immunity, and

emissions requirements as specified by the Federal Communications Commission (FCC),

Underwriters Laboratories (UL), and others. The following table summarizes this compliance:

Table 1-1: Regulatory Agency Compliance

Type:

Specification:

Safety

IEC60950/EN60950 – Safety of Information Technology Equipment

(Western Europe)

UL60950, CSA C22.2 No. 60950 – Safety of Information Technology

Equipment, including Electrical Business Equipment (BI-National)

GR1089-CORE

Global IEC – CB Scheme Report IEC 60950, all country deviations

Environmental

1-4

ATCA-9305 User’s Manual

NEBS: Telecordia GR-63 –

Section 4.1.1 Transportation and Storage Environmental Criteria;

Section 4.1.2 Operating Temperature and Humidity;

Section 4.1.3 Altitude;

Section 4.1 4 Temperature Margins;

Section 4.4.1 Earthquake Environment;

Section 4.4.4 Office Vibration:

Section 4.4.5 Transportation Vibration

10009109-01

Overview:

Additional Information

(continued)

Type:

Specification:

EMC

FCC Part 15, Class A– Title 47, Code of Federal Regulations, Radio

Frequency Devices

ICES 003, Class A – Radiated and Conducted Emissions, Canada

NEBS: Telecordia GR-1089 level 3 – Emissions and Immunity (circuit pack

level testing only)

EN55022 – Information Technology Equipment, Radio Disturbance

Characteristics, Limits and Methods of Measurement

EN55024 – Information Technology Equipment, Immunity

Characteristics, Limits and Methods of Measurement

ETSI EN300386 – Electromagnetic Compatibility and Radio Spectrum

Matters (ERM), Telecommunication Network Equipment,

Electromagnetic Compatibility (EMC) Requirements

AS/NZS 3548 003, Class A – Standard for radiated and conducted

emissions for Australia and New Zealand

Emerson maintains test reports that provide specific information regarding the methods

and equipment used in compliance testing. Unshielded external I/O cables, loose screws, or

a poorly grounded chassis may adversely affect the ATCA-9305 hardware’s ability to comply

with any of the stated specifications.

The UL web site at ul.com has a list of Emerson’s UL certifications. To find the list, search in

the online certifications directory using Emerson’s UL file number, E190079. There is a list

for products distributed in the United States, as well as a list for products shipped to Canada. To find the ATCA-9305, search in the list for 10009986-xx, where xx changes with each

revision of the printed circuit board.

The Ethernet connection of the equipment or subassembly must be connected with

shielded cables that are grounded at both ends.

RoHS Compliance

The ATCA-9305 is compliant with the European Union’s RoHS (Restriction of use of Hazardous Substances) directive created to limit harm to the environment and human health by

restricting the use of harmful substances in electrical and electronic equipment. Effective

July 1, 2006, RoHS restricts the use of six substances: cadmium (Cd), mercury (Hg), hexavalent chromium (Cr (VI)), polybrominated biphenyls (PBBs), polybrominated diphenyl ethers

(PBDEs) and lead (Pb). Configurations that are RoHS compliant are built with lead-free solder.

To obtain a certificate of conformity (CoC) for the ATCA-9305, send an e-mail to

sales@artesyncp.com or call 1-800-356-9602. Have the part number(s)

(e.g., C000####-##) for your configuration(s) available when contacting Emerson.

10009109-01

ATCA-9305 User’s Manual

1-5

Overview:

Additional Information

Terminology and Notation

Active low signals: An active low signal is indicated with an asterisk * after the signal name.

Byte, word: Throughout this manual byte refers to 8 bits, word refers to 16 bits, and long word refers to

32 bits, double long word refers to 64 bits.

PLD: This manual uses the acronym, PLD, as a generic term for programmable logic device (also

known as FPGA, CPLD, EPLD, etc.).

Radix 2 and 16: Hexadecimal numbers end with a subscript 16. Binary numbers are shown with a

subscript 2.

Technical References

Further information on basic operation and programming of the ATCA-9305 components

can be found in documents listed in Table 1-2.

Table 1-2: Technical References

Device /

Interface:

ATCA

Document: 1

AdvancedTCA® Base Specification

(PICMG® 3.0 Revision 2.0 March 18, 2005)

Engineering Change Notice 3.0-1.0-001

(PICMG® 3.0 R2.0: ECN 3.0-2.0-001 June 15, 2005)

Ethernet/Fibre Channel for AdvancedTCA™ Systems

(PICMG® 3.1 Revision 1.0 January 22, 2003)

http://www.picmg.org

CPU

CN5860

MPC8548

Cavium Networks OCTEON™ Plus CN58XX Hardware Reference Manual

(Cavium Networks, CN58XX-HM-1.2 Sept. 2008)

http:/www.caviumnetworks.com

MPC8548E PowerQUICC™ III Integrated Processor Family Reference Manual

(Freescale™ Semiconductor, Inc. MPC8548ERM Rev.2, 02/2007

http://www.freescale.com

DRAM

576Mb: x9, x18, x36 2.5V VEXT, 1.8C VDD, HSTL, CIO,RLDRAM II Data Sheet

(Micron Technology, Inc. 576Mb_RLDRAM_II_CIO_D1.fm - Rev C 9/07 EN)

http://www.micron.com

EEPROM

Atmel® 2-Wire Serial EEPROM 64K (8192 x 8) Preliminary Data Sheet

(Atmel Corporation, 5174C-SEEPR-6/07)

http://www.atmel.com

Ethernet

BCM5461S

BCM5482

10/100/1000BASE-T Gigabit Ethernet Transceiver Data Sheet

(Broadcom® Corporation, Document 5461S-DS17-R 5/12/08)

10/100/1000BASE-T Gigabit Ethernet Transceiver Data Sheet

(Broadcom® Corporation, Document 5482-DS04-R 10/18/07)

http://www.broadcom.com

1-6

ATCA-9305 User’s Manual

10009109-01

Overview:

Additional Information

Device /

Interface:

Flash

Document: 1

(continued)

32 Mbit (x8/x16) Concurrent SuperFlash Data Sheet

(Silicon Storage Technology, Inc., S71270-01-000 9/05)

http://www.sst.com

mDOC H3 Embedded Flash Drive (EFD) featuring Embedded TrueFFS® Flash Management

Software Preliminary Data Sheet

(msystems 92-DS-1205-10 Rev. 0.2 June 2006)

http://www.m-systems.com/mobile

StrataFlash® Embedded Memory (P33) Data Sheet

(Intel®, Order Number: 314749-004 November 2007)

http://www.intel.com

4. Serial Configuration Devices (EPCS1, EPCA4, EPCS16, & EPCS64)

(Altera® Corporation CS1014-2.0 April 2007)

http://www.altera.com

IPMI

IPMI — Intelligent Platform Management Interface Specification v2.0

(Intel Hewlett-Packard NEC Dell, Rev. 1.0, Feb. 12, 2004)

IPMI — Intelligent Platform Management Bus Communications Protocol Specification v1.0

(Intel Hewlett-Packard NEC Dell, Rev. 1.0, November 15, 1999)

IPMI — Platform Management FRU Storage Definition v1.0

(Intel Hewlett-Packard NEC Dell, Rev. 1.1, September 27, 1999)

http://www.intel.com/design/servers/ipmi/

Hardware Platform Management IPM Controller Firmware Upgrade Specification v1.0

(PICMG HPM.1 R1.0 May 4, 2007)

http://www.picmg.org

RTC

M41T00S

Serial Access Real-Time Clock Data Sheet

(STMicroelectronics December 2004)

Switch

BCM56802

BCM56800 Series 20-Port 10-Gigabit Ethernet Multilayer Switch Preliminary Data Sheet

(Broadcom® Corporation, Document 56800-DS03-R 12/28/07)

http://www.broadcom.com

1. Frequently, the most current information regarding addenda/errata for specific documents may be

found on the corresponding web site.

10009109-01

ATCA-9305 User’s Manual

1-7

(blank page)

1-8

ATCA-9305 User’s Manual

10009109-01

Section 2

Setup

This chapter describes the physical layout of the boards, the setup process, and how to

check for proper operation once the boards have been installed. This chapter also includes

troubleshooting, service, and warranty information.

ELECTROSTATIC DISCHARGE

Before you begin the setup process, please remember that electrostatic discharge (ESD) can

easily damage the components on the ATCA-9305 hardware. Electronic devices, especially

those with programmable parts, are susceptible to ESD, which can result in operational failure. Unless you ground yourself properly, static charges can accumulate in your body and

cause ESD damage when you touch the board.

Caution: Use proper static protection and handle ATCA-9305 boards only when absolutely

necessary. Always wear a wriststrap to ground your body before touching a board. Keep

!

your body grounded while handling the board. Hold the board by its edges–do not touch

any components or circuits. When the board is not in an enclosure, store it in a staticshielding bag.

To ground yourself, wear a grounding wriststrap. Simply placing the board on top of a staticshielding bag does not provide any protection–place it on a grounded dissipative mat. Do

not place the board on metal or other conductive surfaces.

ATCA-9305 CIRCUIT BOARD

The ATCA-9305 circuit board is an ATCA blade assembly and complies with the PICMG 3.0

ATCA mechanical specification. It uses a 16-layer printed circuit board with the following

dimensions:

Table 2-1: Circuit Board Dimensions

Width:

Depth:

Height:

Weight (typical):

12.687 in.

(322.25 mm)

11.024 in.

(280.01 mm)

< .84 in.

(<21.33 mm)

4.2 lb.

(1.91 kg)1

1. This is the typical weight for the ATCA-9305. Board weight varies slightly per configuration; contact

Technical Support if you require a specific configuration weight.

The following figures show the front panel, component maps, and LED locations for the

ATCA-9305 circuit board.

10009109-01

ATCA-9305 User’s Manual

2-1

Setup:

ATCA-9305 Circuit Board

Figure 2-1: ATCA-9305 Front Panel

MGT ETH

SPD

Red/Amber = Out of Service (OOS)

O

O

S

Green = In Service (2)

2

LINK

ACT

SPD

Amber = User Defined (3)

3

SWITCH

ETH

Management Console

Reset

Blue Hot Swap

LINK

ACT

Ethernet Speed (top LED)

Off = 10 Mbps

Yellow = 100 Mbps

Port 1

Green = 1000Mbps

Port 2 Ethernet Link/Activity (bottom LED)

Off = No Link

On= Link, No Activity

Blink = Link/Activity

MGT CSL

RST

H/S

ATCA-9035

Note: The electromagnetic compatibility (EMC) tests used an ATCA-9305 model that includes a front panel assembly from Emerson Network Power, Embedded Computing.

Caution: For applications where the ATCA-9305 is provided without a front panel, or where the front

panel has been removed, your system chassis/enclosure must provide the required

!

electromagnetic interference (EMI) shielding to maintain CE compliance.

2-2

ATCA-9305 User’s Manual

10009109-01

Setup:

ATCA-9305 Circuit Board

Figure 2-2: Component Map, Top (Rev. 01)

CR4

C21

C22

C19

C20

C17

C16

C15

CR3

C7

U1

C18

C2

R4

R5

R3

C6

C84

C83

C178

U15

CN58x0

Processor 2

R83

C212

R332

R84

R85

R86

R87

C238

C211

C225

C239

CR11

C242

CR12

R1060

C213

C199

C215

C214

J3

C226

C200

R67

R81

C164

L8

C201

C216

J4

J5

J6

C243

C244

C245

R93

R94

R95

C251

C252

C253

C267

C268

C269

C300

C302

C304

C299

C301

C303

C305

R92

R73

R80

C162

C227

C228

C240

C241

C247

C248

C255

C256

C271

C272

C306

C349

R104

C347

C348

R103

C346

C343

U16

C2113

C187

C208

C203

C205

C207

C209

C217

C219

C221

C223

C220

C222

C231

C233

C235

C234

C236

C218

C229

C230

C232

C224

C257

C259

C261

C263

C258

C260

C262

C264

C273

C275

C277

C279

C274

C276

C278

C280

C291

C293

C295

C292

C294

C296

C307

C309

C311

C308

C310

C297

C298

C313

C312

C314

C323

R105

R106

R110

C385

C384

R117

R118

C395

C396

C394

R120

C428

C430

C431

C446

C448

C427

C429

C445

C444

C447

C425

C426

C442

C443

C424

C433

U22

L36

C458

L40

L41

L43

L45

L58

L62

C604

C607

C608

C664

C670

C671

C672

C656

C643

C666

C667

R248

R249

C665

C673

C637

L65

C675

J11 J12 J13 J14

C681

C682

R259

R260

R261

C687

C688

C689

C693

C694

C695

C696

C683

C555

C556

C557

C571

C569

C568

C566

CR49

R252

C680

R254

R253

C678

R255

R1059

R258

C570

C565

U58

R247

C674

R251

CR48

J23

80-pin

Zone 2

ATCA

Connector

U55

12V

Power Supply

C2118

C677

C2106

C684

R262

C690

C691

C2111

C685

C697

R256

C669

CR47

CR46

CR44

R231

R229

C641

C642

C660

R246

C668

C567

C564

C550

C548

C552

C553

C554

C549

C551

C561

C563

C559

C562

U51 U52

R220

C686

C692

R264

C698

U59

U60

R263

C655

C663

C529

C531

R257

C654

C653

C662

C640

C639

C657

C652

C651

C638

C658

C647

C650

C648

C646

C645

U57

C649

C659

R245

C528

R221

+

U56

CN58x0

Processor 1

C527

R226

+

C644

C526

L59

U50

PHY

C599

R217

C603

L63

R214

C598

C610

R213

C591

C597

R238

C634

C633

C500

C501

R210

C590

C609

R1057

C581

R208

C617

CR42

R1056

U48

Microcontroller

C560

C558

L57

L55

L56

L54

L53

L52

L51

U44

R225

R230

U54

C625

C499

L48

L47

L49

R202

R204

R203

R201

R98

U47

CR43

CR41

CR40

CR38

CR39

CR37

CR35

L39

R194

R1049

R222

CR36

C616

C632

L38

L44

R243

R205

U49

C601

C606

L37

L42

L50

R180

JP1

C530

C546

U43

C547

C544

C545

C542

C543

C540

C541

C539

C537

C538

C536

C535

C533

C534

C532

R223

R224

R215

L35

R242

C676

C484

C490

R1050

R219

L64

U34

BCM5680x

Switch

L33

P4

SW1

U39

C635

R250

C471

C485

C488

L34

R241

C661

C470

C469

L32

L46

U46

R212

C636

R244

L23

C459

L22

L21

C456

L20

L16

L14

U30

Y5

R211

C615

C614

L15

R1034

U28

U29

C580

C589

C588

C586

C579

C595

C594

R179

C493

C522

C525

C523

C520

C521

C524

C518

C517

C519

C515

C516

C514

C513

C511

C512

C510

C509

C508

C507

C506

C505

C504

C503

C502

R198

R199

F3

C621

C631

C441

R1036

R1035

R1039

C492

CR34

R216

R237

C630

C629

R236

Polar Key

ATCA Guide

C482

U36 U37 U38

Y7

C578

C577

C576

R207

C574

C573

C572

C592

C593

C600

C436

C483

U32

C494

U40

Y6

C602

C613

C612

C423

C434

C468

C495

U33

R765

R235

C360

L29

R218

C611

C417

C422

C624

C628

C355

C359

C358

R116

C416

C626

R234

C353

C357

L26

Y8

C575

R206

C584

C582

C583

C354

L25

C496

R189

R188

R187

R186

R185

U31

R192

C605

R761

C336

C489

RN12

RN11

R183

C620

C619

C712

C335

C334

C352

CR31

R196

R228

C324

C333

CR21

R200

R227

J31

80-pin

Zone 3

ATCA

Connector

J30

80-pin

Zone 3

ATCA

Connector

CR18

R193

R197

C618

C702

C704

C706

C703

C705

C707

C700

C699

C708

C718

C717

R267

C716

C715

C714

C711

C713

C701

C709

F4

C723

F5

C719

R265

C2149

R266

R757

C186

CR22

R195

CR29

CR28

R176

C487

C486

CR27

R175

R178

CR25

CR23

CR24

U27 Y4

U53

R759

C172

L24

R184

U42

SPI-XAUI

Bridge

R190

R191

P5

P6

R233

C197

C206

C491

R182

R232

C195

C204

CR32

R181

R240

C193

C202

C435

CR16

CR19

CR33

U41

SPI-XAUI

Bridge

C421

CR14

J9

C467

RN10

R177

CR26

C466

R1032

C477

C479

C478

C476

C475

R174

L31

L28

R171

R173

CR30

R172

C473

C472

R170

CR20

C480

L30

R166

Y3

R165

CR17

R168

R169

C481

L27

U23S

C463

CR15

R163

R164

C420

Y9

C2103

U24

KSL

CPLD

RN9

RN8

C455

C462

C474

C419

C596

R1041

C461

C465

C464

R239

C171

C184

C437

C418

R144

R143

R142

R159

R158

R157

C452

C453

C451

C450

C460

R167

C622

C169

C170

C185

L11

U21

RN7

RN6

R156

R154

R155

R152

R150

R151

R149

R153

R147

R148

C432

R140

R139

R138

R136

R134

R133

R135

R132

R137

R130

R131

R129

R126

R127

R128

R125

R124

C439

C438

L13

L12

R145

R146

C440

C454

C449

R162

C623

C196

C191

L18

C415

RN5

R160

R161

C627

C194

L19

C414

CR13

U45

C192

R115

C393

L17

C390

C402

C406

C410

C408

C413

C345

C411

C404

R141

L61

C154

C155

C183

C398

R121

C403

C392

Y2

U20

C405

C400

C409

C399

C391

C389

C388

C401

C387

R119

C382

C381

C380

C377

U17

R114

RN4

C383

C412

L60

C140

C182

C370

C375

C379

C378

R111

R112

R123

P7

Mini-B

USB

C139

C152

C153

C168

R107

RN2

C374

C407

C397

R109

RN3

U19

MPC8548

Processor

C386

R108

C373

C376

R113

U18

SO-CDIMM

U35S

C137

C138

C167

C368

C369

C372

U26

C151

C190

C322

C2104

RN1

C365

C338

R101

C366

C364

C367

C332

C350

C356

C331

C342

C341

C371

U25

C150

C180

C351

Y1

C330

R100

C329

C340

C328

R99

C339

C337

C270

C288

C285

C286

C287

C283

C284

C327

C325

C320

C326

C363

C361

C254

C290

C319

R2

C362

L9

C289

R97

C136

C165

C166

C321

R819

C316

C315

C317

C318

R102

L10

C282

C281

C265

R96

C135

C134

C148

C149

C246

C249

C250

C133

C181

C457

R334

CR10

C198

R72

R70

C177

R71

C176

C147

C161

C146

C160

C145

C144

C174

R82

C237

C143

C173

C175

CR45

C188

C158

R460

R91

C159

C163

C157

R462

C210

C141

C142

U13

SPI-XAUI

Bridge

CR9

R90

R89

R66

C130

C131

U14

R88

C129

C132

P2

P3

RJ45

R65

C2110

C128

C156

R79

R39

C105

C104

C125

C124

R64

C123

C122

C121

R63

R62

R61

C120

C2147

R69

R77

C119

C2145

U12

R68

R75

R15

C28

C27

C43

C44

C56

R42

R40

R41

C66

C67

C65

C64

C62

C63

C61

C59

C126

C117

C118

C179

R58

R57

R59

R56

R54

R60

CR6

F2

R78

R46

C85

C106

CR8

R76

M2

R45

R44

C2116

C116

CR7

R74

R43

C75

C115

C114

C113

CR5

C112

U11

J33

24-pin ATCA

Connector

R25

U9

C2119

C92

R52

R55

P1

RJ45

C68

C2108

R51

L7

C103

C96

C95

C94

C97

C109

C110

C111

C108

C98

U8

C54

R53

L5

C90

R50

M1

C69

C102

C81

C89

C87

C88

C80

C86

C101

C79

C78

L6

C100

R1010

C77

L4

R49

R27

C50

C49

C48

C51

C47

C46

C53

R26

R38

C58

C74

C82

R24

R23

R22

C52

R37

C99

R48

C76

C93

C107

U6

C33

U7

C344

R28

C42

L1

R10

R9

C26

R8

C24

C25

R7

R21

C41

R36

C60

C72

C73

L3

C57

C71

R47

C10

C14

R19

R17

R18

C32

R16

C31

R20

R35

U10

SPI-XAUI

Bridge

Polar Key

ATCA Guide

C9

C8

C13

R6

C30

C29

C40

C38

C37

C36

C35

L2

C34

F1

C39

R13

C12

U5

R14

R11

R12

J1

R34

C45

R32

R33

R31

C55

R29

R30

C5