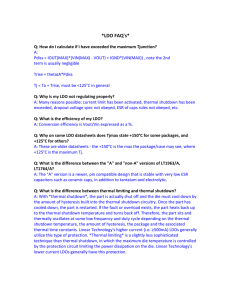

Any-Cap Low Dropout Voltage Regulator

advertisement