Digital Logic: Three-State Buffers, Multiplexers, and Shifters

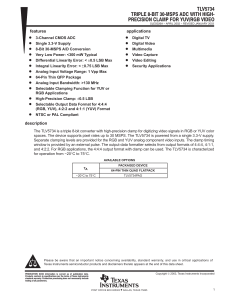

advertisement

Three-state buffers • Output = LOW, HIGH, or Hi-Z – High-impedance – Wire can be considered disconnected • Can tie multiple outputs together if at most one at a time is enabled CMOS three-state buffer Different flavors Three-state drivers Driver application Three-state transceiver Transceiver application CMOS NAND gate Open-drain CMOS Open-drain CMOS gate driving a load Driving an LED Wired-AND Multiple sources sharing BUS Switching equivalent Multiplexers Switches Switch ON OFF Combining S·D D 0 + S'+D D 1 · D Hi-Z Wired-OR D Hi-Z Wired-OR Tranx Gate Sharing a wire (8-1 MUX) SDATA mayy be Hi-Z 2-1 multiplexer 4-1 Multiplexer 74x153 • 4-input, 2-bit-wide • Two 4-1 4 1 MUXs • Shared select signals p enable signals g • Separate 74x157: 2-input 4-bit multiplexer Four 2-1 MUXs with ith shared h d enable bl andd select l t signals i l 74x157 Logic diagram 74x151 8-input multiplexer 74x151 logic diagram Implement an 8-1 MUX with 2-1 MUX • Several ways D7 S0 I1 S D6 D5 D4 D3 I0 I1 S I0 I1 S I0 I1 S I0 I1 S I0 S1 S2 I1 S I0 D2 D1 D0 I1 S I0 D7 S2 I1 S D3 D5 D2 D6 I0 I1 S I0 I1 S I0 I1 S I0 I1 S I0 S1 S0 I1 S I0 D2 D4 D0 I1 S I0 Build a 32-to-1 multiplexer with 74x151s • Use a decoder to enable one of the 8-1 multiplexers • Consider each 8-1 multiplexer as a switch Implement any 3-variable with 74-x151 Can we do it with a 4-1 multiplexer and an inverter? F(x, y, z) = x′ · y′ · F(0, 0, z) + x′ · y · F(0, ( , 1,, z)) + x · y′ · F(0, 1, z) + x · y · F(1, 1, z) One variable function f(z): 0 1 z z′ Example: a 4-1 multiplexer and an inverter Demultiplexer • Demultiplexers route the bus data to one of m destinations – Manyy different types yp of demultiplexers p All outputs except the selected one are 0 All outputs except the selected one are 0 All outputs except the selected one are Hi Hi-Z Z 1-bit n-output demultiplexer: one data input and s select inputs to select one of n = 2s outputs Decoder working as a demultiplexer 1-4 demux Selected output = SRCDATA Other outputs = 0 Shifter design example • • • • n data inputs, n data outputs Control inputs: number of positions to rotate or shift data inputs Many possible solutions, all based on multiplexers Example: n = 8 – D [7:0], Y[7:0], S[2:0] (shift amount) Eight-bit shifter Data input: D[7:0] = A B C D E F G H Control: S[2:0] O Output: Y[7 Y[7:0] 0] S[2:0] Y[7:0] 0 A B C D E F G H 1 B C D E F G H 0 2 C D E F G H 0 0 3 D E F G H 0 0 0 4 E F G H 0 0 0 0 5 F G H 0 0 0 0 0 6 G H 0 0 0 0 0 0 7 H 0 0 0 0 0 0 0 Eight-bit rotator Data input: D[7:0] = A B C D E F G H Control: S[2:0] O Output: Y[7 Y[7:0] 0] S[2:0] Y[7:0] 0 A B C D E F G H 1 B C D E F G H A 2 C D E F G H A B 3 D E F G H A B C 4 E F G H A B C D 5 F G H A B C D E 6 G H A B C D E F 7 H A B C D E F G Implementation • 8-1 MUXs • Do the shift (rotation) in multiple stages Eight-bit rotator with 2-1 MUXes D6 S0 I1 S D7 D5 D6 D4 I0 I1 S I0 I1 S W7 W5 S1 I1 S W6 W4 W6 W3 I0 I1 S I0 I1 S X3 S2 I1 S X6 X2 X6 X1 I0 I1 S I0 I1 S Y6 I1 S W5 I0 I0 D2 D3 D1 D2 D0 I1 S I0 I1 S I0 I1 S W2 I1 S W3 W4 I0 I0 X0 I1 S I0 W0 W2 W7 I1 S I0 I1 S I0 I1 S X2 X3 X6 X2 X5 I1 S I0 I1 S I0 I1 S Y2 I0 D7 I0 W0 W1 I0 W6 W0 I1 S I0 X0 X1 I0 Y1 D0 I1 S X1 X7 Y3 D1 W1 W3 X3 X4 Y4 W2 W1 X4 X5 Y5 D4 W4 X5 X7 Y7 I0 D3 W5 W7 X7 D5 X4 X0 I1 S I0 Y0 Other things • Rotate to right – To righ i bits == To left n – i bits • Shift or rotate 16 16-to-1 muxes 16-to-1 mux = Two 8-to-1 mux + NAND gate (OR gate) S3 decides d id which hi h 75x151 is enabled Disabled one outputs Y = 0 (Y_L = 1) 4 16-bit 2-to-1 muxes 16-bit 16 bit 22-to-1 to 1 mux = Four 44-bit bit 2 2-to-1 to 1 mux (74x157) X[15:0] = S0 ? DIN[14:0, 15] : DIN[15:0]; Y[15:0] [ ] = S1 ? X[14:0, [ , 15:14]] : X[15:0]; [ ]; Z[15:0] = S2 ? Y[11:0, 15:12] : Y[15:0]; DOUT[15:0] = S3 ? Z[7:0, 15:8] : Z [15:0]; Properties of different approaches Multiplexer Component Data Loading Data Delay Control Loading Total ICs 74x151 16 2 32 36 74 251 74x251 16 1 32 32 74x153 4 2 8 16 74x157 2 4 4 16