11 - Logical Efforts

advertisement

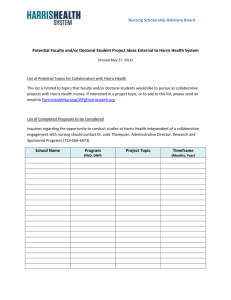

Topic 11 Logical Effort: Outline Designing for Speed on the Back of an Envelope David Harris David_Harris@hmc.edu Harvey Mudd College Claremont, CA o o o o o o o o Introduction Delay in a Logic Gate Multi-stage Logic Networks Choosing the Best Number of Stages Example Asymmetric & Skewed Logic Gates Circuit Families Summary Logical Effort Introduction How large should the transistors be? How many stages of logic give least delay? Decoder specification: Uses a very simple model of delay Back of the envelope calculations and tractable optimization Gives new names to old ideas to emphasize remarkable symmetries Who cares about logical effort? o o o Circuit designers waste too much time simulating and tweaking circuits High speed logic designers need to know where time is going in their logic CAD engineers need to understand circuits to build better tools Logical Effort David Harris Ben Bitdiddle is the memory designer for the Motoroil 68W86, an embedded processor for automotive applications. Help Ben design the decoder for a register file: 32 bits a<3:0> a<3:0> Page 3 of 56 o o o o o 16 word register file Each word is 32 bits wide 16 Register File Each bit presents a load of 3 unit-sized transistors True and complementary inputs of address bits a<3:0> are available Each input may drive 10 unit-sized transistors Ben needs to decide: o o o How many stages to use? How large should each gate be? How fast can the decoder operate? Logical Effort David Harris Page 4 of 56 16 words What is the best circuit topology for a function? 4:16 Decoder ? ? ? Logical Effort is a method of answering these questions: o o o Page 2 of 56 Example Chip designers face a bewildering array of choices. o o o David Harris Outline Let us express delays in a process-independent unit: Introduction d abs d = ---------τ Delay in a Logic Gate Multi-stage Logic Networks Choosing the Best Number of Stages τ ≈ 12 ps in 0.18 μm technology Delay of logic gate has two components: Example effort delay, a.k.a. stage effort Asymmetric & Skewed Logic Gates parasitic delay d = f+p Circuit Families Summary Effort delay again has two components: f = gh Logical Effort David Harris Page 5 of 56 Logical effort describes relative ability of gate topology to deliver current (defined to be 1 for an inverter) o Electrical effort is the ratio of output to input capacitance Logical Effort David Harris g= p= d= effort delay 6 How about a 2-input NOR? 1 parasitic delay 4 3 2 AN D g = 4/3 p=2 d = (4/3)h + 2 g=1 p=1 d=h+1 inp ut N 5 2- AN D Page 6 of 56 Delay Plots Normalized delay: d 2 in ve rte r 3 g= p= d= inp ut N 4 2- Normalized delay: d 5 electrical effort is sometimes called “fanout” o Delay Plots 6 logical effort electrical effort = Cout/Cin in ve rte r o o o o o o o o Delay in a Logic Gate effort delay 1 parasitic delay 1 2 3 4 5 Electrical effort: h = Cout / Cin 1 2 3 4 5 Electrical effort: h = Cout / Cin o d = f + p = gh + p o Delay increases with electrical effort o More complex gates have greater logical effort and parasitic delay o d = f + p = gh + p o Delay increases with electrical effort o More complex gates have greater logical effort and parasitic delay Logical Effort Logical Effort David Harris Page 7 of 56 David Harris Page 45 of 56 Computing Logical Effort A Catalog of Gates Table 1: Logical effort of static CMOS gates DEF: Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. o o Measured from delay vs. fanout plots of simulated or measured gates inverter Or estimated, counting capacitance in units of transistor width: a b 2 4 2 2 a Inverter: Cin = 3 g = 1 (def) 2 2 NAND2: Cin = 4 g = 4/3 a b 3 4 4/3 5/3 6/3 7/3 (n+2)/3 NOR 5/3 7/3 9/3 11/3 (2n+1)/3 multiplexer 2 2 2 2 2 XOR, XNOR 4 12 32 Table 2: Parasitic delay of static CMOS gates Gate type 1 1 Parasitic delay pinv inverter n-input NAND npinv n-input NOR npinv n-way multiplexer 2npinv p inv ≈ 1 parasitic delays depend on diffusion capacitance 2-input XOR, XNOR 4npinv Logical Effort David Harris Page 8 of 56 Logical Effort David Harris Example Logical Effort: g = Electrical Effort: h = Parasitic Delay: p = Stage Delay: d = Estimate the frequency of an N-stage ring oscillator: Oscillator Frequency: F = Logical Effort: g≡1 Electrical Effort: out h = --------= 1 Parasitic Delay: p = p inv ≈ 1 Stage Delay: d = gh + p = 2 C C in 1 2Nd abs 1 4N τ Oscillator Frequency: F = ------------------- = ----------- David Harris Page 9 of 56 Example Estimate the frequency of an N-stage ring oscillator: Logical Effort n 5 1 x 2 1 NOR2: Cin = 5 g = 5/3 1 NAND 4 x x Number of inputs Gate type Page 10 of 56 Logical Effort David Harris A 31 stage ring oscillator in a 0.18 μm process oscillates at about 670 MHz. Page 46 of 56 Example Example Estimate the delay of a fanout-of-4 (FO4) inverter: Estimate the delay of a fanout-of-4 (FO4) inverter: d Logical Effort: g = Electrical Effort: h = Parasitic Delay: p = Stage Delay: d = d Logical Effort: g≡1 Electrical Effort: out h = --------= 4 Parasitic Delay: p = p inv ≈ 1 Stage Delay: d = gh + p = 5 C C in The FO4 inverter delay is a useful metric to characterize process performance. 1 FO4 delay = 5τ This is about 60 ps in a 0.18 μm process. Logical Effort David Harris Page 11 of 56 Logical Effort David Harris Outline o o o o o o o o Page 47 of 56 Multi-stage Logic Networks Logical effort extends to multi-stage networks: Introduction Delay in a Logic Gate 10 Multi-stage Logic Networks Choosing the Best Number of Stages g1 = 1 h1 = x/10 Example Asymmetric & Skewed Logic Gates x y g2 = 5/3 h2 = y/x g3 = 4/3 h3 = z/y z 20 g4 = 1 h4 = 20/z Circuit Families o Summary ∏ gi Path Logical Effort: G = o Path Electrical Effort: C out (path) H = --------------------C in (path) o Path Effort: F = ∏ fi = ∏ g i h i Don’t define H = ∏ hi because we don’t know hi until the design is done Can we write F = GH ? Logical Effort David Harris Page 12 of 56 Logical Effort David Harris Page 13 of 56 Branching Effort Branching Effort No! Consider circuits that branch: 15 G = H = GH = h1 = h2 = F = 90 5 15 No! Consider circuits that branch: 90 15 90 5 15 = GH? G =1 H = 90 / 5 = 18 GH = 18 h1 = (15+15) / 5 = 6 h2 = 90 / 15 = 6 F = 36, not 18! 90 Introduce new kind of effort to account for branching within a network: C on path + C o Branching Effort: off path b = --------------------------------------------- o Path Branching Effort: B = C on path ∏ bi Now we can compute the path effort: o Logical Effort David Harris Page 14 of 56 Path Effort: Logical Effort Delay in Multi-stage Networks Path Effort Delay: o Path Parasitic Delay: o Path Delay: David Harris ∏ hi = BH ≠ H in circuits that branch Page 48 of 56 Determining Gate Sizes We can now compute the delay of a multi-stage network: o F = GBH Note: Gate sizes can be found by starting at the end of the path and working backward. o ∑ fi PF = ∑ pi DF = ∑ di = D F + P DF = At each gate, apply the capacitance transformation: C out • g i i C in = ---------------------ˆf i o We can prove that delay is minimized when each stage bears the same effort: Check your work by verifying that the input capacitance specification is satisfied at the beginning of the path. ˆf = g h = F 1 ⁄ N i i Therefore, the minimum delay of an N-stage path is: NF o 1⁄N +P This is a key result of logical effort. Lowest possible path delay can be found without even calculating the sizes of each gate in the path. Logical Effort David Harris Page 15 of 56 Logical Effort David Harris Page 16 of 56 Example Example z Select gate sizes y and z to minimize delay from A to B A Logical Effort: G = Electrical Effort: H = Branching Effort: y C y 9C z z from A to B A 9C B z Select gate sizes y and z to minimize delay 3 y C 9C z y z 9C B Logical Effort: G = (4 ⁄ 3) B = Electrical Effort: C out H = --------= 9 C in Path Effort: F = Branching Effort: B = 2•3 = 6 Best Stage Effort: ˆf = Path Effort: F = GHB = 128 Delay: D = Best Stage Effort: ˆf = F 1 ⁄ 3 ≈ 5 Work backward for sizes: Delay: D = 3 • 5 + 3 • 2 = 21 • ( 4 ⁄ 3) y = 3z ---------------------------- = 1.92 C Work backward for sizes: z = y = Logical Effort 9C Page 17 of 56 Logical Effort Outline o o o o o o o o 9C • (4 ⁄ 3) z = ----------------------------- = 2.4 C 5 5 David Harris David Harris Page 49 of 56 Choosing the Best Number of Stages Introduction How many stages should a path use? Delay in a Logic Gate o o Multi-stage Logic Networks Choosing the Best Number of Stages Example Delay is not always minimized by using as few stages as possible Example: How to drive 64 bit datapath with unit-sized inverter 1 1 1 1 Initial driver 8 4 2.8 Asymmetric & Skewed Logic Gates 16 Circuit Families N: f: D: D = NF Logical Effort 8 22.6 Summary Datapath load David Harris Page 18 of 56 Logical Effort 64 64 1 64 65 1⁄N + P = N ( 64 ) 64 2 8 18 1⁄N 9C 64 Fastest 3 4 15 4 2.8 15.3 + N assuming polarity doesn’t matter David Harris Page 19 of 56 Derivation of the Best Number of Stages Suppose we can add inverters to the end of a path without changing its function. N-n1 extra inverters Logic Block: n1 stages Path effort F p inv + ρ ( 1 – ln ρ ) = 0 has no closed form solution. o o Neglecting parasitics (i.e. pinv = 0), we get the familiar result that ρ = 2.718 (e) For pinv = 1, we can solve numerically to obtain ρ = 3.59 How sensitive is the delay to using exactly the best number of stages? D(N) / D(N) n1 D = NF 1⁄N + ∑ p i + ( N – n 1 ) p inv 1 .6 1 .4 1 .2 1 .0 1 .5 1 1 .1 5 1 .2 6 I like to use ρ=4 1 (ρ = 2 .4 ) 1⁄N 1⁄N 1⁄N ∂D ------- = – F ln ( F )+F + p inv = 0 ∂N Define ρ ≡ F ˆ 1⁄N 0 .0 to be the best stage effort. Substitute and simplify: p inv + ρ ( 1 – ln ρ ) = 0 Logical Effort David Harris 1 .0 1 .4 2 .0 2.4 < ρ < 6 gives delays within 15% of optimal -> we can be sloppy Logical Effort Outline o o o o o o o o 0 .7 N /N o Page 20 of 56 0 .5 David Harris Page 21 of 56 Example Let’s revisit Ben Bitdiddle’s decoder problem using logical effort: 32 bits a<3:0> a<3:0> Introduction Delay in a Logic Gate Multi-stage Logic Networks Choosing the Best Number of Stages Decoder specification: Example o o o o o Asymmetric & Skewed Logic Gates Circuit Families Summary 4:16 Decoder o (ρ = 6 ) 16 word register file Each word is 32 bits wide 16 Register File Each bit presents a load of 3 unit-sized transistors True and complementary inputs of address bits a<3:0> are available Each input may drive 10 unit-sized transistors Ben needs to decide: o o o Logical Effort David Harris Page 22 of 56 How many stages to use? How large should each gate be? How fast can the decoder operate? Logical Effort David Harris Page 23 of 56 16 words o ˆ How many stages should we use? Let N be the value of N for least delay. Best Number of Stages (continued) Example: Number of Stages Example: Number of Stages How many stages should Ben use? How many stages should Ben use? o o o o Effort of decoders is dominated by electrical and branching portions o Electrical Effort: o Branching Effort: Effort of decoders is dominated by electrical and branching portions Electrical Effort: Branching Effort: H = B = 32 • 3- = 9.6 H = -------------10 B = 8 because each address input controls half the outputs If we neglect logical effort (assume G = 1), o F = Path Effort: If we neglect logical effort, o Remember that the best stage effort is about ρ = 4 o Hence, the best number of stages is: N = Remember that the best stage effort is about ρ = 4 o o Logical Effort David Harris Page 24 of 56 Hence, the best number of stages is: N = log 476.8 = 3.1 Let’s try a 3-stage design Logical Effort Example: Gate Sizes & Delay z y o o o o Actual path effort is: Therefore, stage effort should be: Gate sizes: Path delay: Logical Effort z F = f = z = D = David Harris David Harris Page 50 of 56 Example: Gate Sizes & Delay Lets try a 3-stage design using 16 4-input NAND gates with G = a0a0 a1a1 a2a2 a3a3 10 unit input capacitance y F = GBH = 8 • 9.6 = 76.8 Path Effort: Lets try a 3-stage design using 16 4-input NAND gates with G = 1 • 2 • 1 = 2 a0a0 a1a1 a2a2 a3a3 10 unit input capacitance out0 y z 96 unit wordline capacitance y out15 o Actual path effort is: z out0 96 unit wordline capacitance out15 F = 2 • 8 • 9.6 = 154 1⁄3 o Therefore, stage effort should be: f = ( 154 ) = 5.36 o z = 96 • 1 ⁄ 5.36 = 18 y = 18 • 2 ⁄ 5.36 = 6.7 o D = 3f + P = 3 • 5.36 + 1 + 4 + 1 = 22.1 y = Page 25 of 56 Logical Effort David Harris Close to 4, so f is reasonable Page 51 of 56 Example: Alternative Decoders Outline Table 3: Comparison of Decoder Designs Design Stages G P D NAND4; INV 2 2 5 29.8 INV; NAND4; INV 3 2 6 22.1 INV; NAND4; INV; INV 4 2 7 21.1 NAND2; INV; NAND2; INV 4 16/9 6 19.7 INV; NAND2; INV; NAND2; INV 5 16/9 7 20.4 NAND2; INV; NAND2; INV; INV; INV 6 16/9 8 21.6 INV; NAND2; INV; NAND2; INV; INV; INV 7 16/9 9 23.1 NAND2; INV; NAND2; INV; INV; INV; INV; INV 8 16/9 10 24.8 o o o o o o o o Introduction Delay in a Logic Gate Multi-stage Logic Networks Choosing the Best Number of Stages Example Asymmetric & Skewed Logic Gates Circuit Families Summary We underestimated the best number of stages by neglecting the logical effort. o o o Logical effort facilitates comparing different designs before selecting sizes Using more stages also reduces G and P by using multiple 2-input gates Our design was about 10% slower than the best Logical Effort David Harris Page 26 of 56 Logical Effort Asymmetric Gates David Harris Page 27 of 56 Asymmetric Gates Asymmetric logic gates favor one input over another. Asymmetric logic gates favor one input over another. Example: suppose input A of a NAND gate is most critical. Example: Suppose input A of a NAND gate is most critical: o o o o Select sizes so pullup and pulldown still match unit inverter Place critical input closest to output 2 Select sizes so pullup and pulldown still match unit inverter Place critical input closest to output 2 2 x x a o o o Logical Effort on input A: gA = Logical Effort on input B: gB = Total Logical Effort: g tot = g A + g B Logical Effort a 4/3 4 David Harris 2 4/3 4 b o o o Page 28 of 56 b Logical Effort on input A: g A = 10 ⁄ 9 Logical Effort on input B: gB = 2 Total Logical Effort: g tot = g A + g B = 28 ⁄ 9 Logical Effort David Harris Effort on A goes down at expense of effort on B and total gate effort Page 52 of 56 Symmetry Factor Skewed Gates In general, consider gates with arbitrary symmetry factor s: o o s = 1/2 in symmetric gate with equal sizes Skewed gates favor one edge over the other. 2 s = 1/4 in previous example Example: suppose rising output of inverter is most critical. 2 x a o Downsize noncritical NMOS transistor to reduce total input capacitance 1/(1-s) 2 b 1/s Logical effort of inputs: gA o o 1 ------------ + 2 1 –s = ---------------------3 a gB 1 --- + 2 s = ------------3 g tot 1 -------------------- + 4 s (1 – s) = -----------------------------3 o o o x a 1 1/2 Page 29 of 56 Logical Effort for rising (up) output: gu = Logical Effort for falling (down) output: gd = Average Logical Effort: g avg = ( g u + g d ) ⁄ 2 Logical Effort Skewed Gates David Harris Page 30 of 56 HI- and LO-Skewed Gates Skewed gates favor one edge over the other. Example: suppose rising output of inverter is most important. o a Unskewed w/ Unskewed w/ equal rise equal fall Compare with unskewed inverter of the same rise/fall time to compute effort. But total logical effort is higher for asymmetric gates David Harris 1/2 1 x HI-Skewed inverter Critical input approaches logical effort of inverter = 1 for small s Logical Effort 2 x Downsize noncritical NMOS transistor to reduce total input capacitance DEF: Logical effort of a skewed gate for a particular transition is the ratio of the input capacitance of that gate to the input capacitance of an unskewed inverter delivering the same output current for the same transition. Skew gates by reducing size of noncritical transistors. 2 2 x a 1/2 1 x a 1 x a 1/2 Skewed inverter Unskewed w/ Unskewed w/ equal rise equal fall Critical rising Compare with unskewed inverter of the same rise/fall time effort goes down o Logical Effort for rising (up) output: gu = 5 ⁄ 6 at expense of noncritical and o Logical Effort for falling (down) output: g d = 5 ⁄ 3 average effort o HI-Skewed gates favor rising outputs by downsizing NMOS transistors LO-Skewed gates favor falling outputs by downsizing PMOS transistors Logical effort is smaller for the favored input due to lower input capacitance Logical effort is larger for the other input g avg = ( g u + g d ) ⁄ 2 = 5 ⁄ 4 Average Logical Effort: Logical Effort o o o o David Harris Page 53 of 56 Logical Effort David Harris Page 31 of 56 Catalog of Skewed Gates Inverter NAND2 4 2 2 ½ 4 gu = 5/6 gd = 5/3 gavg = 5/4 1 1 gu = 1 gd = 2 gavg = 3/2 LO-Skew 1 ½ 1 2 gu = 4/3 gd = 2/3 gavg = 1 Logical Effort 2 2 gu = 2 gd = 1 gavg = 3/2 gu = 3/2 gd = 3 gavg = 9/4 ½ 2 1 1 o o o o o o o o NOR2 2 HI-Skew Outline Introduction Delay in a Logic Gate Multi-stage Logic Networks Choosing the Best Number of Stages Example Asymmetric & Skewed Logic Gates Circuit Families Summary gu = 2 gd = 1 gavg = 3/2 1 1 David Harris Page 32 of 56 Logical Effort Pseudo-NMOS David Harris Page 33 of 56 Pseudo-NMOS Pseudo-NMOS gates replace fat PMOS pullups on inputs with a resistive pullup. Pseudo-NMOS gates replace fat PMOS pullups on inputs with a resistive pullup. o o o o o o o o o o Resistive pullup must be much weaker than pulldown stack (e.g. 4x) Reduces logical effort because inputs must only drive the NMOS transistors However, NMOS current reduced by contention with pullup Unequal rising and falling efforts Quiescent power dissipation when output is low 2/3 Example: Pseudo-NMOS inverter o o o x Logical Effort for falling (down) output: gd = Logical Effort for rising (up) output: gu = Average Logical Effort: g avg = ( g u + g d ) ⁄ 2 Logical Effort David Harris a Page 34 of 56 4/3 Resistive pullup must be much weaker than pulldown stack (e.g. 4x) Reduces logical effort because inputs must only drive the NMOS transistors However, NMOS current reduced by contention with pullup Unequal rising and falling efforts Logical effort can be applied to domino, pseudo-NMOS, and other logic families 2/3 Example: Pseudo-NMOS inverter o o o x Logical Effort for falling (down) output: gd = 4 ⁄ 9 Logical Effort for rising (up) output: gu = 4 ⁄ 3 Average Logical Effort: g avg = ( g u + g d ) ⁄ 2 = 8 ⁄ 9 Logical Effort David Harris a Page 54 of 56 4/3 Pseudo-NMOS Gates Dynamic Logic Dynamic logic replace fat PMOS pullups on inputs with a clocked precharge. Inverter NAND2 NOR2 2/3 2/3 2/3 x a 4/3 gd = 4/9 gu = 4/3 gavg = 8/9 x a 8/3 b 8/3 o o o o x a 4/3 4/3 b Reduces logical effort because inputs must only drive the NMOS transistors Eliminates pseudo-NMOS contention current and power dissipation Only the falling (“evaluation”) delay is critical Downsize noncritical precharge transistors to reduce clock load and power φ Example: Footless dynamic inverter gd = 8/9 gu = 8/3 gavg = 16/9 o gd = 4/9 gu = 4/3 gavg = 8/9 x gd = Logical Effort for falling (down) output: 1 a 1 Robust gates may require keepers and clocked pulldown transistors (“feet”). o o Tradeoffs exist between power and effort by varying P/N ratio. Logical Effort David Harris Page 35 of 56 Feet prevent contention during precharge but increase logical effort Weak keepers prevent floating output at cost of slight contention during eval Logical Effort David Harris Dynamic Logic Dynamic Gates Dynamic logic replace fat PMOS pullups on inputs with a clocked precharge. o o o o Inverter Reduces logical effort because inputs must only drive the NMOS transistors Footless Critical pulldown (“evaluation”) delay independent of precharge size φ Logical Effort for falling (down) output: gd = 1 ⁄ 3 a 1 1 x 2 b 2 φ 1 x a 1 1 b gd = 1/3 gd = 2/3 x a 1 φ Footed Page 55 of 56 1 a a 2 2 gd = 2/3 b φ Logical Effort φ 1 x x φ Weak keepers prevent floating output at cost of slight contention during eval David Harris a NOR2 φ 1 x 1 Feet prevent contention during precharge but increase logical effort Logical Effort NAND2 φ 1 gd = 1/3 Robust gates may require keepers and clocked pulldown transistors (“feet”). o o φ Eliminates pseudo-NMOS contention current and power dissipation Example: Footless dynamic inverter Page 36 of 56 3 x a 3 gd = 1 3 David Harris φ 2 2 b gd = 2/3 2 Page 37 of 56 Domino Gates Domino Gates Dynamic gates require monotonically rising inputs. Dynamic gates require monotonically rising inputs. o o o o o o However, they generate monotonically falling outputs Alternate dynamic gates with HI-skew inverting static gates Dynamic / static pair is called a domino gate However, they generate monotonically falling outputs Alternate dynamic gates with HI-skew inverting static gates Dynamic / static pair is called a domino gate Example: Domino Buffer Example: Domino Buffer o o o o o o o o o o o o o o o o Constraints: maximum input capacitance = 3, load = 54 Logical Effort: G= Branching Effort: B = Electrical Effort: H= Path Effort: F= Stage Effort: f= φ 3 p HI-Skew a 3 n g1 g2 54 HI-Skew Inverter: size = Transistor Sizes: n = p = Logical Effort David Harris Page 38 of 56 Constraints: maximum input capacitance = 3, load = 54 Logical Effort: G = (1/3) * (5/6) = 5/18 Branching Effort: B = 1 Electrical Effort: H = 54/3 = 18 Path Effort: F = (5/18) * 1 * 18 = 5 Stage Effort: f= 5 = 2.2 HI-Skew Inverter: size =54 * (5/6) / 2.2 = 20 Transistor Sizes: n = 4 p = 16 Logical Effort Comparison of Circuit Families PMOS transistors have half the drive of NMOS transistors Skewed gates downsize noncritical transistors by factor of two Pseudo-NMOS gates have 1/4 strength pullups Table 4: Summary of Logical Efforts Circuit Style Inverter g gd gu Static CMOS n-input NAND g gu 1 gd n-input NOR g gu (n+2)/3 3 p HI-Skew a 3 n 54 g1 = 1/3 g2 = 5/6 Page 56 of 56 Outline Assumptions: o o o David Harris φ gd (2n+1)/3 HI-Skew 5/6 5/3 (n/2+2)/3 (n+4)/3 (2n+.5)/3 (4n+1)/3 LO-Skew 4/3 2/3 2(n+1)/3 (n+1)/3 2(n+1)/3 (n+1)/3 Pseudo-NMOS 4/3 4/9 4n/3 4n/9 4/3 o o o o o o o o Introduction Delay in a Logic Gate Multi-stage Logic Networks Choosing the Best Number of Stages Example Asymmetric & Skewed Logic Gates Circuit Families Summary 4/9 Footed Dynamic 2/3 (n+1)/3 2/3 Footless Dynamic 1/3 n/3 1/3 Adjust these numbers as you change your assumptions. Logical Effort David Harris Page 39 of 56 Logical Effort David Harris Page 40 of 56 Summary Method of Logical Effort Table 5: Key Definitions of Logical Effort Term Logical effort Electrical effort Branching effort Stage expression g (seeTable 1) C C in out h = --------n/a Logical effort helps you find the best number of stages, the best size of each gate, and the minimum delay of a circuit with the following procedure: Path expression ∏ gi G = C C in (path) out (path) H = --------------------- B = ∏ bi o Compute the path effort: o Estimate the best number of stages: F = GBH ˆ ≈ log F N o Estimate the minimum delay: D = N̂F +P F = GBH o Sketch your path using the number of stages computed above ∑ fi Compute the stage effort: Number of stages 1 N o o Parasitic delay p Delay d = f+p Effort delay (seeTable 2) Logical Effort DF = P = ∑ ˆf = F 1 ⁄ N Starting at the end, work backward to find transistor sizes: C out • g i i C in = ---------------------ˆf i pi D = DF + P David Harris Page 41 of 56 Logical Effort Limitations of Logical Effort David Harris Page 42 of 56 Conclusion Logical effort is not a panacea. Some limitations include: Logical effort is a useful concept for thinking about delay in circuits: o Chicken & egg problem how to estimate G and best number of stages before the path is designed o Simplistic delay model neglects effects of input slopes o ˆ 1⁄N f = gh f Effort o 4 Interconnect iteration required in designs with branching and non-negligible wire C or RC o o o o o o Facilitates comparison of different circuit topologies Easily select gate sizes for minimum delay Circuits are fastest when effort delays of each stage are equal and about 4 Path delay is insensitive to modest deviations from optimal sizes Logic gates can be skewed to favor one input or edge at the cost of another Logical effort can be applied to domino, pseudo-NMOS, and other logic families same convergence difficulties as in synthesis / placement problem Logical effort provides a language for engineers to discuss why circuits are fast. Maximum speed only optimizes circuits for speed, not area or power under a fixed speed constraint o Like any language, requires practice to master A book on Logical Effort is available from Morgan Kaufmann Publishers o http://www.mkp.com/Logical_Effort o Discusses P/N ratios, gate characterization, pass gate logic, forks, wires, etc. Logical Effort David Harris Page 43 of 56 Logical Effort David Harris Page 44 of 56 Delay Plots Estimate the frequency of an N-stage ring oscillator: AN D g=1 p=1 d=h+1 in ve rte r 3 g = 4/3 p=2 d = (4/3)h + 2 inp ut N 5 2- Normalized delay: d 6 4 Example effort delay 2 1 parasitic delay 1 2 3 4 5 Electrical effort: h = Cout / Cin o d = f + p = gh + p o Delay increases with electrical effort o More complex gates have greater logical effort and parasitic delay Logical Effort David Harris Page 45 of 56 Logical Effort: g≡1 Electrical Effort: out h = --------= 1 Parasitic Delay: p = p inv ≈ 1 Stage Delay: d = gh + p = 2 C C in 1 2Nd abs Logical Effort David Harris Example No! Consider circuits that branch: d 15 15 Electrical Effort: out h = --------= 4 C C in Parasitic Delay: p = p inv ≈ 1 Stage Delay: d = gh + p = 5 Logical Effort David Harris The FO4 inverter delay is a useful metric to characterize process performance. G =1 H = 90 / 5 = 18 GH = 18 h1 = (15+15) / 5 = 6 h2 = 90 / 15 = 6 F = 36, not 18! 90 5 g≡1 Page 46 of 56 Branching Effort Estimate the delay of a fanout-of-4 (FO4) inverter: Logical Effort: 1 4N τ Oscillator Frequency: F = ------------------- = ----------- A 31 stage ring oscillator in a 0.18 μm process oscillates at about 670 MHz. 90 Introduce new kind of effort to account for branching within a network: C on path + C o Branching Effort: off path b = --------------------------------------------- 1 FO4 delay = 5τ o Path Branching Effort: B = This is about 60 ps in a 0.18 μm process. Now we can compute the path effort: Page 47 of 56 o Path Effort: Logical Effort C on path ∏ bi F = GBH David Harris Note: ∏ hi = BH ≠ H in circuits that branch Page 48 of 56 Example Example: Number of Stages z Select gate sizes y and z to minimize delay from A to B A 3 y C 9C z y 9C z B How many stages should Ben use? o Effort of decoders is dominated by electrical and branching portions o Electrical Effort: o Branching Effort: Logical Effort: G = (4 ⁄ 3) Electrical Effort: C out H = --------= 9 C in Branching Effort: B = 2•3 = 6 If we neglect logical effort, Path Effort: F = GHB = 128 o Best Stage Effort: ˆf = F 1 ⁄ 3 ≈ 5 Delay: 9C Work backward for sizes: 9C • (4 ⁄ 3) z = ----------------------------- = 2.4 C 5 D = 3 • 5 + 3 • 2 = 21 • ( 4 ⁄ 3) y = 3z ---------------------------- = 1.92 C 5 Logical Effort David Harris Page 49 of 56 controls half the outputs Path Effort: Hence, the best number of stages is: N = log 476.8 = 3.1 Let’s try a 3-stage design Logical Effort y o Actual path effort is: z Example: Suppose input A of a NAND gate is most critical: o o Select sizes so pullup and pulldown still match unit inverter Place critical input closest to output 2 96 unit wordline capacitance 2 x a 4/3 4 out15 F = 2 • 8 • 9.6 = 154 David Harris Page 50 of 56 Asymmetric logic gates favor one input over another. out0 o Therefore, stage effort should be: f = ( 154 )1 ⁄ 3 = 5.36 o z = 96 • 1 ⁄ 5.36 = 18 y = 18 • 2 ⁄ 5.36 = 6.7 o D = 3f + P = 3 • 5.36 + 1 + 4 + 1 = 22.1 Logical Effort David Harris Asymmetric Gates Lets try a 3-stage design using 16 4-input NAND gates with G = 1 • 2 • 1 = 2 a0a0 a1a1 a2a2 a3a3 10 unit input capacitance z F = GBH = 8 • 9.6 = 76.8 Remember that the best stage effort is about ρ = 4 o o Example: Gate Sizes & Delay y 32 • 3- = 9.6 H = -------------10 B = 8 because each address input Close to 4, so f is reasonable Page 51 of 56 o o o b Logical Effort on input A: g A = 10 ⁄ 9 Logical Effort on input B: gB = 2 Total Logical Effort: g tot = g A + g B = 28 ⁄ 9 Logical Effort David Harris Effort on A goes down at expense of effort on B and total gate effort Page 52 of 56 Skewed Gates Pseudo-NMOS Skewed gates favor one edge over the other. Pseudo-NMOS gates replace fat PMOS pullups on inputs with a resistive pullup. Example: suppose rising output of inverter is most important. o o o o o o Downsize noncritical NMOS transistor to reduce total input capacitance 2 2 x a 1 x a 1/2 x a 1 Reduces logical effort because inputs must only drive the NMOS transistors However, NMOS current reduced by contention with pullup Unequal rising and falling efforts Logical effort can be applied to domino, pseudo-NMOS, and other logic families 1/2 Skewed inverter Unskewed w/ Unskewed w/ equal rise equal fall Critical rising Compare with unskewed inverter of the same rise/fall time effort goes down o Logical Effort for rising (up) output: gu = 5 ⁄ 6 at expense of noncritical and o Logical Effort for falling (down) output: g d = 5 ⁄ 3 average effort o Resistive pullup must be much weaker than pulldown stack (e.g. 4x) 2/3 Example: Pseudo-NMOS inverter o o o x Logical Effort for falling (down) output: gd = 4 ⁄ 9 Logical Effort for rising (up) output: gu = 4 ⁄ 3 Average Logical Effort: g avg = ( g u + g d ) ⁄ 2 = 8 ⁄ 9 David Harris Page 53 of 56 Logical Effort David Harris Dynamic Logic Dynamic gates require monotonically rising inputs. o o o o o o Reduces logical effort because inputs must only drive the NMOS transistors Eliminates pseudo-NMOS contention current and power dissipation Critical pulldown (“evaluation”) delay independent of precharge size φ Example: Footless dynamic inverter Logical Effort for falling (down) output: gd = 1 ⁄ 3 x a 1 Feet prevent contention during precharge but increase logical effort Weak keepers prevent floating output at cost of slight contention during eval David Harris Page 55 of 56 However, they generate monotonically falling outputs Alternate dynamic gates with HI-skew inverting static gates Dynamic / static pair is called a domino gate Example: Domino Buffer 1 Robust gates may require keepers and clocked pulldown transistors (“feet”). Logical Effort Page 54 of 56 Domino Gates Dynamic logic replace fat PMOS pullups on inputs with a clocked precharge. o o 4/3 g avg = ( g u + g d ) ⁄ 2 = 5 ⁄ 4 Average Logical Effort: Logical Effort o a o o o o o o o o Constraints: maximum input capacitance = 3, load = 54 Logical Effort: G = (1/3) * (5/6) = 5/18 Branching Effort: B = 1 Electrical Effort: H = 54/3 = 18 Path Effort: F = (5/18) * 1 * 18 = 5 Stage Effort: f= 5 = 2.2 HI-Skew Inverter: size =54 * (5/6) / 2.2 = 20 Transistor Sizes: n = 4 p = 16 Logical Effort David Harris φ 3 p HI-Skew a 3 n 54 g1 = 1/3 g2 = 5/6 Page 56 of 56