AD8019 - USBid

advertisement

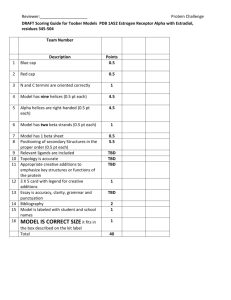

PRELIMINARY TECHNICAL DATA a DSL Line Driver With Power Down PRELIMINARY TECHNICAL DATA FEATURES L o w d i s t o r t i o n , h i g h o u t p u t c u r r e n t a m p l i f ie r s operate from +12V to +/-12V power supplies, i d e a l f o r h i g h p e r f o r m a n c e ADSL or G. L i t e CPE xDSL modems. Low Power Operation +1 2 V t o ± 1 2 V V o l t a g e S u p p l y 9.0m A / A m p ( t y p ) S u p p l y C u r r e n t Digital (1- b i t ) p o w e r d o w n Voltage Feedback Amplifiers L o w Distortion Out of Band SFDR - 70dBc @ 200k Hz High Spe e d 135 M H z B a n d w i d t h ( - 3dB) , G=+1 800 V/µS Slew Rate High dynamic range Vout to within 2V of power supply APPLICATIONS ADSL, VDSL, HDSL and Proprietary xDSL USB, PCI, PCMCIA modems and Cus tomer Premise Equipment Home Networking NIC Cards Power Line Data Transmission AD8019 Out1 -In1 +In1 -Vs AD8019AR nc +Vs Out1 -In1 Out2 +In1 -In2 -Vs +In2 PWDN nc 8 Pin SOIC (‘Thermal Coastline’ ) - nc +Vs Out2 -In2 +In2 nc DGND AD8019ARU 14 Pin TSSOP (Thermal Coastline) MTPR/SFDR Vs=+/-12V Vs=+12V AD8019 Transformer 1:1.2 Transformer = 1:2.2 -73dBc/-86dBc -69dBc/-85dBc AD8016 Transformer 1:1.4 Transformer 1:1.4 -72dBc/-83dBc -68dBc/-83dBc AD8017 N/A Transformer 1:2 -66dBc/-75dBc Figure 1. Performance comparison table of ADI line drivers under ADSL CPE (upstream) conditions- Out of Band SFDR is measured while driving 13dBm ADSL DMT signal upstream into 100Ω line. The AD8019 is compared to the AD8017 at +12V and the AD8016 at +/-12V. Note that the AD8019 duplicates AD8016 CPE performance- at lower cost and smaller package. PRODUCT DESCRIPTION The AD8019 DSL low cost xDSL line driver is optimized to drive minimum 13dBm into low impedance loads while delivering outstanding distortion performance. The highly efficient amplifier architecture delivers 200ma minimum output current into low impedance loads, enabling single +12V designs with a 1:2 transformer turns ratio. The AD8019 is built on a 24V high speed bipolar process which also allows the AD8019 to drive low distortion signals close to +/-12V power supply rails. Hybrid designs using the +/-12V power supply range of the AD8019 enable the use of 1:1 turns ratio transformer, minimizing attenuation of the receive signal. The AD8019 provides a one bit digital down feature (outputs high impedance). The AD8019 draws 9ma/amplifier static current. The AD8019 comes in thermally enhanced 8L SOIC and 14L TSSOP, and is pin compatible with the 8L SOIC AD8017 +12V line driver, and the AD8018 +5V xDSL CPE driver. 1 Rev PrB 11-08-00 This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing. PRELIMINARY TECHNICAL DATA AD8019 SPECIFICATIONS (@25°C, Vs=+/-12, RL=100Ω ,RF=500Ω , RS=50Ω , Tmin = -45C, Tmax = +85C unless otherwise noted) Parameter DYNAMIC PERFORMANCE Conditions Min Typ -3dB Bandwidth G= +1, VOUT<0.4V p-p, RL=100 Ω G= +2, VOUT<0.4V p-p, RL=100Ω VOUT<0.4V p-p, RL=100Ω VOUT=4V p-p Non-Inverting,VOUT= 4Vp-p Non-Inverting, VOUT= 2Vp-p 0.1%, VOUT= 2Vp-p TBD TBD 135 90 5.5 50 800 5.5 20 0.1dB Bandwidth Large Signal Bandwidth Slew Rate Rise & Fall Time Settling Time NOISE / HARMONIC PERFORMANCE Distortion, nd 2 Harmonic rd 3 Harmonic Out of Band SFDR Input Noise Voltage Input Noise Current Crosstalk DC PERFORMANCE Input Offset Voltage VOUT= 3Vp-p (differential) 100kHz, RL=200 Ω 500kHz, RL=200 Ω 100kHz, RL=200 Ω 500kHz, RL=200 Ω 144kHz to 500kHz, Differential Rl=200 Ω f=100kHz f=100kHz f = 1MHz, G=+2 INPUT CHARACTERISTICS Input Resistance Input Capacitance +Input Bias Current -Input Bias Current +Input Bias Current Match -Input Bias Current Match CMRR Input CM Voltage Range OUTPUT CHARACTERISTICS Output Resistance Output Voltage Swing Output Current Short-Circuit Current POWER SUPPLY Supply Current/Amp Supply Current/Amp Operating Range Power Supply Rejection Ratio VOUT= 2Vp-p, Rl = 200 Ohms Tmin-Tmax -TBD dBc nV√Hz pA√Hz dB 1 20 2 TBD TBD TBD 15 mV mV mV MΩ MΩ 10 0.5 1 1 1 1 58 MΩ pF µA µA µA µA dB V TBD TBD TBD TBD TBD Vs-2 Vs-2 Ω V mA mA TBD TBD TBD TBD +/-4 56 TBD mA mA mA V dB 0.2 Vs+2 100 TBD TBD 8 +/-2.0 dBc -70 4 1 -85 Vs+2 PWDN = ‘High’ Tmin - Tmax PWDN = ‘Low’ Dual Supply dBc dBc dBc -TBD TMIN to TMAX TMIN to TMAX TMIN to TMAX TMIN to TMAX Vin –1V to 1V SFDR –TBD dBc into 100Ω at 100kHz Units MHz MHz MHz MHz V/µs ns ns -TBD -TBD Tmin-Tmax Input Offset Voltage Match Open Loop Gain Max 2 This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Rev PrB 11-08-00 Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing. PRELIMINARY TECHNICAL DATA AD8019 SPECIFICATIONS (@25°C, Vs=+/-6, RL=25Ω ,RF=500Ω , RS=50Ω , Tmin = -45C, Tmax = +85C unless otherwise noted) Parameter DYNAMIC PERFORMANCE Conditions Min Typ -3dB Bandwidth G= +1, VOUT<0.4V p-p, RL=100 Ω G= +2, VOUT<0.4V p-p, RL=100Ω VOUT<0.4V p-p, RL=100Ω VOUT=4V p-p Non-Inverting,VOUT= 4Vp-p Non-Inverting, VOUT= 2Vp-p 0.1%, VOUT= 2Vp-p TBD TBD 140 85 6 50 800 5.5 0.1dB Bandwidth Large Signal Bandwidth Slew Rate Rise & Fall Time Settling Time NOISE / HARMONIC PERFORMANCE Distortion, nd 2 Harmonic rd 3 Harmonic Out of Band SFDR Input Noise Voltage Input Noise Current Crosstalk VOUT= 3Vp-p (differential) 100kHz, RL=50 Ω 500kHz, RL=50 Ω 100kHz, RL=50 Ω 500kHz, RL=50 Ω 144kHz to 500kHz, Differential Rl=50 Ω f=100kHz f=100kHz f = 1MHz, G=+2 Tmin-Tmax INPUT CHARACTERISTICS Input Resistance Input Capacitance +Input Bias Current -Input Bias Current +Input Bias Current Match -Input Bias Current Match CMRR Input CM Voltage Range VOUT= 2Vp-p, Rl = 200 Ohms Tmin-Tmax Units MHz MHz MHz MHz V/µs ns 20 DC PERFORMANCE Input Offset Voltage Input Offset Voltage Match Transimpedance Max -TBD -TBD -TBD -TBD -70 4 1 -80 dBc dBc dBc dBc dBc nV√Hz pA√Hz dB 1 10 2 10 TBD TBD 15 mV mV mV MΩ MΩ 10 0.5 1 1 1 1 58 MΩ pF µA µA µA µA dB V TBD TMIN to TMAX TMIN to TMAX TMIN to TMAX TMIN to TMAX Vin –1V to 1V ns Vs+2 TBD TBD TBD TBD Vs-2 OUTPUT CHARACTERISTICS Output Resistance Output Voltage Swing Output Current Short-Circuit Current POWER SUPPLY Supply Current/Amp Supply Current/Amp Supply Current/Amp Operating Range Power Supply Rejection Ratio Vs-2 Ω V mA mA TBD TBD TBD TBD TBD TBD +/-12 TBD mA mA mA mA V dB 0.2 SFDR –TBD dBc into 25 Ω at 100kHz PWDN = ‘High’ Tmin - Tmax PWDN = ‘Low’ PWDN = ‘High Impedance’ Dual Supply Vs+2 200 TBD TBD 8 +/-4.0 56 Rev PrB 11-08-00 This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing. Patents pending. 3 PRELIMINARY TECHNICAL DATA AD8019 near the supply terminals to supply current for fast, large signal changes at the AD8019 outputs. GENERAL INFORMATION THEORY OF OPERATION The AD8019 is a voltage feedback amplifier with high output current capability. It is fabricated on Analog Devices' proprietary High Voltage eXtra Fast Complimentary Bipolar Process (XFCB-HV), which enables the construction of PNP and NPN transistors with similar fT's in the 4 GHz region. The process is dielectrically isolated to eliminate the parasitic and latchup problems caused by junction isolation. These features enable the construction of high frequency, low-distortion amplifiers. LAYOUT CONSIDERATIONS As is the case with all high-speed applications, careful attention to printed circuit board layout details will prevent associated board parasitics from becoming problematic. Proper RF design technique is mandatory. The PCB should have a ground plane covering all unused portions of the component side of the board to provide a low-impedance return path. Removing the ground plane on all layers from the area near the input and output pins will reduce stray capacitance, particularly in the area of the inverting inputs. Signal lines connecting the feedback and gain resistors should be as short as possible to minimize the inductance and stray capacitance associated with these traces. Termination resistors and loads should be located as close as possible to their respective inputs and outputs. Input and output traces should be kept as far apart as possible to minimize coupling (crosstalk) though the board. Adherence to stripline design techniques for long signal traces (greater than about 1 inch) is recommended. Following these generic guidelines will improve the performance of the AD8019 in all applications. PWDN FEATURE A digitally programmable logic pin (PWDN) is available on the TSSOP-14 package. It allows the user to select between two operating conditions, on and shutdown. The DGND pin is the logic reference. The threshold for the PWDN pin is 3 volts above DGND. If the user does not wish to use the power feature, both the PWDN and DGND pins can be left to float, although it is highly recommended that no pin be left unconnected. It is better to tie the DGND pin to the lowest potential that the AD8019 is tied to and place the PWDN pin at a potential at least 3 volts higher than that of the DGND pin, but lower that the positive supply voltage, VCC. To optimize the AD8019’s performance as an ADSL differential line driver, locate the transformer hybrid near the AD8019 drivers and as close to the RJ11 jack as possible. Maintain differential circuit symmetry into the differential driver and from the output of the drivers through the transformer coupled output of the bridge circuit as much as possible. POWER SUPPLY AND DECOUPLING The AD8019 can be powered with a good quality (i.e. low-noise) supply anywhere in the range from +12V to +/12V. In order to optimize the ADSL upstream drive capability of +13dBm and maintain the best Spurious Free Dynamic Range (SFDR), the AD8019 circuit should be supplied with a well-regulated supply. STABILITY ENHANCEMENTS Whenever using a high-speed amplifier, care must be taken in order to ensure that the amplifier is operating in a stable environment. Parasitic capacitance in combination with the high impedance of the inverting input can create a pole that can dramatically decrease the phase margin of the AD8019. In the case of the AD8019, it may be necessary to place 10-20pF in parallel with the feedback resistor in order to cancel out any parasitic capacitance that may be present at the inverting input. The inclusion of a capacitor in the feedback path may or may not be necessary at higher gains. Careful attention must be paid to decoupling the power supply. High quality capacitors with low equivalent series resistance (ESR) such as multi-layer ceramic capacitors (MLCC's) should be used to minimize supply voltage ripple and power dissipation. A large, usually tantalum, 10 to 47µF capacitor located in proximity to the AD8019 is required to provide good decoupling for lower frequency signals. In addition, 0.1µF MLCC decoupling capacitors should be located as close to each of the power supply pins as is physically possible, no more than 1/8 inch away. An additional large (4.7 to 10 µF) tantalum capacitor should be placed on the board Rev PrB 11-08-00 This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing. Patents pending. 4 PRELIMINARY TECHNICAL DATA AD8019 Rev PrB 11-08-00 This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing. Patents pending. 5 PRELIMINARY TECHNICAL DATA AD8019 Rev PrB 11-08-00 This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing. Patents pending. 6