Application Note 1719

HS-OP470ARHEV1Z Evaluation Board User’s Guide

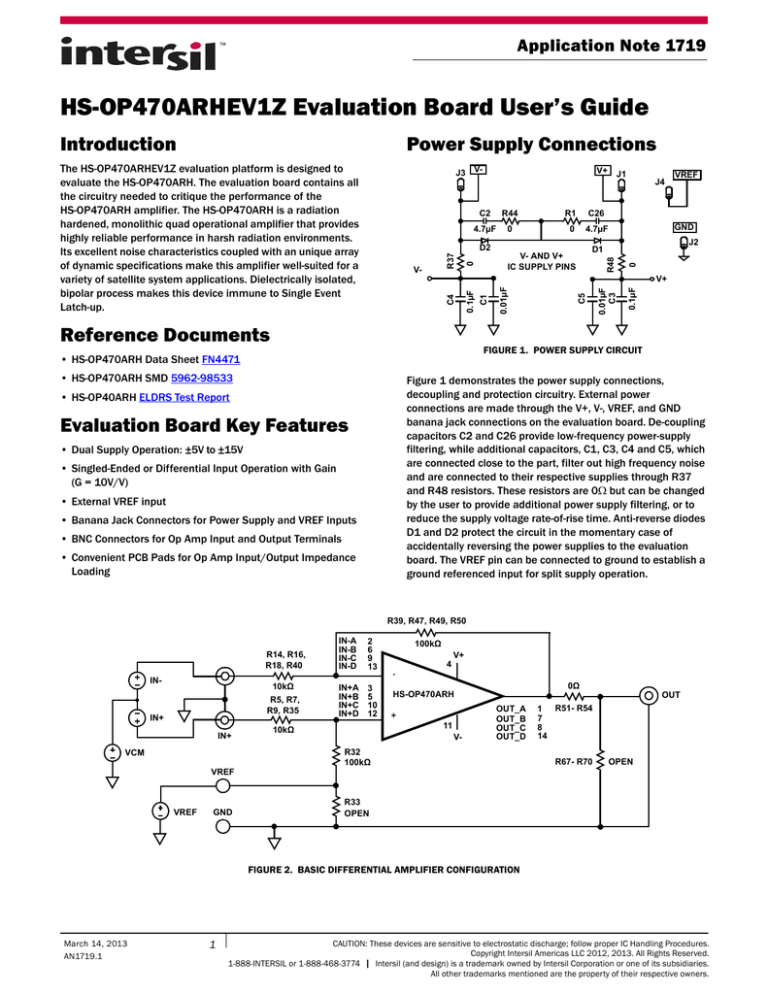

Power Supply Connections

J3 V-

V+

C2

R44

R1

C26

4.7µF

0

0

4.7µF

VREF

GND

J2

0

D1

V- AND V+

IC SUPPLY PINS

R48

0

J4

Reference Documents

C5

0.01µF

C1

0.1µF

V+

C4

V-

R37

D2

J1

0.1µF

The HS-OP470ARHEV1Z evaluation platform is designed to

evaluate the HS-OP470ARH. The evaluation board contains all

the circuitry needed to critique the performance of the

HS-OP470ARH amplifier. The HS-OP470ARH is a radiation

hardened, monolithic quad operational amplifier that provides

highly reliable performance in harsh radiation environments.

Its excellent noise characteristics coupled with an unique array

of dynamic specifications make this amplifier well-suited for a

variety of satellite system applications. Dielectrically isolated,

bipolar process makes this device immune to Single Event

Latch-up.

0.01µF

C3

Introduction

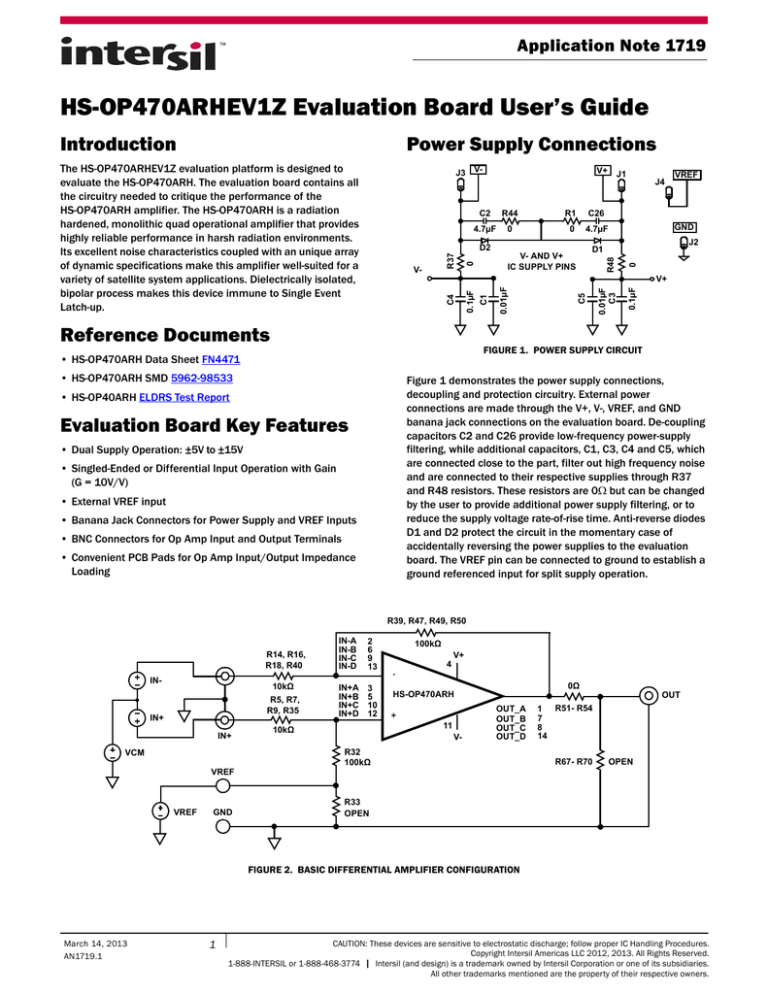

FIGURE 1. POWER SUPPLY CIRCUIT

• HS-OP470ARH Data Sheet FN4471

• HS-OP470ARH SMD 5962-98533

Figure 1 demonstrates the power supply connections,

decoupling and protection circuitry. External power

connections are made through the V+, V-, VREF, and GND

banana jack connections on the evaluation board. De-coupling

capacitors C2 and C26 provide low-frequency power-supply

filtering, while additional capacitors, C1, C3, C4 and C5, which

are connected close to the part, filter out high frequency noise

and are connected to their respective supplies through R37

and R48 resistors. These resistors are 0 but can be changed

by the user to provide additional power supply filtering, or to

reduce the supply voltage rate-of-rise time. Anti-reverse diodes

D1 and D2 protect the circuit in the momentary case of

accidentally reversing the power supplies to the evaluation

board. The VREF pin can be connected to ground to establish a

ground referenced input for split supply operation.

• HS-OP40ARH ELDRS Test Report

Evaluation Board Key Features

• Dual Supply Operation: ±5V to ±15V

• Singled-Ended or Differential Input Operation with Gain

(G = 10V/V)

• External VREF input

• Banana Jack Connectors for Power Supply and VREF Inputs

• BNC Connectors for Op Amp Input and Output Terminals

• Convenient PCB Pads for Op Amp Input/Output Impedance

Loading

R39, R47, R49, R50

R14, R16,

R18, R40

IN-

10kΩ

R5, R7,

R9, R35

IN+

IN+

IN-A

IN-B

IN-C

IN-D

2

6

9

13

IN+A

IN+B

IN+C

IN+D

3

5

10

12

100kΩ

-

4

V+

+

11

10kΩ

0Ω

HS-OP470ARH

V-

OUT_A

OUT_B

OUT_C

OUT_D

R32

100kΩ

VCM

OUT

1 R51- R54

7

8

14

R67- R70

OPEN

VREF

VREF

GND

R33

OPEN

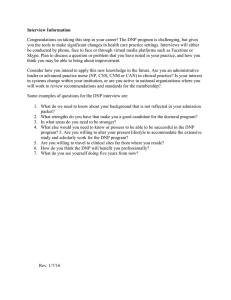

FIGURE 2. BASIC DIFFERENTIAL AMPLIFIER CONFIGURATION

March 14, 2013

AN1719.1

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

Copyright Intersil Americas LLC 2012, 2013. All Rights Reserved.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

Application Note 1719

Amplifier Configuration

The outputs (Figure 4) also have additional resistor and capacitor

placements for filtering and loading.

A simplified schematic of the evaluation board is shown in

Figure 2. The input stage with the components supplied is shown

in Figure 3. The circuit implements a Hi-Z differential input with

unbalanced common mode impedance. The differential

amplifier gain is expressed in Equation 1:

NOTE: Operational amplifiers are sensitive to output capacitance

and may oscillate. In the event of oscillation, reduce output

capacitance by using shorter cables, or add a resistor in series

with the output.

R6

0Ω

10kΩ

100kΩ

R11

DNP

R2

IN-A

DNP

FROM OUT_A

TO IN-A

R5

R15

10kΩ

C7

0Ω

TO IN+A

R21

IN+A

DNP

For single-ended input with an inverting gain G = -10V/V, the IN+

input is grounded and the signal is supplied to the IN- input. VREF

must be connected to a reference voltage between the V+ and Vsupply rails. For non-inverting operation with G = 11V/V, the

negative input (IN-) is grounded and the signal is supplied to the

positive input (IN+). The non-inverting gain is strongly dependent

on any resistance from IN- to GND. For good gain accuracy, a 0

resistor should be installed on the empty R11 pad.

DNP

C23

OPEN

R39

R20

C6

OPEN

R14

(EQ. 1)

V OUT = V IN+ – V IN- R F R IN + V REF

OPEN

User-selectable Options

FIGURE 3. INPUT STAGE

DNP

J13 OUT A

R67

DNP

0Ω

OPEN DNP

R59

R63

0Ω

R55

R51

C15

A voltage divider can be added to establish a power

supply-tracking common mode reference using the VREF input.

The inverting and non-inverting inputs have additional resistor

and capacitor placements for adding input attenuation or

feedback capacitors (Figure 3).

OPEN

OUT_A

C14

Component pads are included to enable a variety of

user-selectable circuits to be added to the amplifier inputs, the

VREF input, outputs and the amplifier feedback loops.

FIGURE 4. OUTPUT STAGE

TABLE 1. HS-OP470ARHEV1Z COMPONENTS PARTS LIST

DEVICE #

DESCRIPTION

COMMENTS

C1, C5

CAP, SMD, 0805, 0.01µF, 50V, 10%, X7R, ROHS

Power Supply Decoupling

C2, C26

CAP, SMD, 1210, 4.7µF, 50V, 10%, X7R, ROHS

Power Supply Decoupling

C3, C4

CAP, SMD, 0805, 0.1µF, 25V, 10%, X7R, ROHS

Power Supply Decoupling

C6-C26

CAP, SMD, 0603, Open Place Holder, ROHS

User Selectable Capacitors - Not Populated

D1, D2

40V Schottky Barrier Diode

Reverse Power Protection

J1-J4

Johnson Components Standard Type Banana Jack, 108-0740-001

Power Supply and Reference Voltage Connector

J5-J16

AMPHENOL BNC Connector, 31-5329-52RFX

Connections for Input and Output

Resistor, SMD, 0603, 100kΩ, 1%, ROHS

VREF Resistor Divider

R5, R7, R9, R14, R16, R18,

R35, R40

Resistor, SMD, 0603, 10kΩ, 1%, 1/16W, ROHS

Gain Setting Resistor

R39, R47, R49, R50

Resistor, SMD, 0603, 100kΩ, 1%, 1/16W, ROHS

Gain Setting Feedback Resistor

Resistor, SMD, 0603, DNP-Place Holder, ROHS

User Selectable Resistors - Not Populated

R32

R2, R3, R4, R11, R12, R13,

R20, R21, R22, R23, R25,

R26, R28, R30, R31, R33,

R34, R38, R42, R43, R46,

R55, R56, R57, R58, R59,

R60, R61, R62, R62, R67,

R68, R69, R70

U1

Submit Document Feedback

HS-OP470ARH, Radiation Hardened, Very Low Noise Quad Operational

Amplifier

2

AN1719.1

March 14, 2013

Application Note 1719

HS-OP470ARHEV1Z Top View

Submit Document Feedback

3

AN1719.1

March 14, 2013

Application Note 1719

HS-OP470ARHEV1Z Top Layer

Submit Document Feedback

4

AN1719.1

March 14, 2013

Application Note 1719

HS-OP470ARHEV1Z Bottom Layer

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is

cautioned to verify that the document is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com

Submit Document Feedback

5

AN1719.1

March 14, 2013

R64

0

0

C12

R46

0

OPEN

DNP

OPEN

0

R19

0

IN+C

RGA+

RINA1+

RREFA+

R35

J12

10K

1

C13

OPEN

R45

RINA+

2

0

R41

0

IN+D

DNP

C11

RINA+

DNP

10K

IN1+

R43

R29

R9

R68

R60

OUT

J16

OUT

DNP

J15

C25

DNP

R69

DNP

R61

R57

0

R66

0

0

RGA+

R62

DNP

R54

R70

R50

100K

DNP

DNP

RREFA+

R26

J10

8

R65

0

C20

R36

D

RINA1+

9

IN+C

IN-C

OUTC

R53

C19

OUT 3

IN-D

RREFA-

DNP

J11

10K

R42

IN-

R38

R13

R31

DNP

C

IN1+

R40

RINA2-

DNP

OPEN

-IN3

OUT 2

RINA-

IN-C

RREFA-

R25

C10

0

DNP

R10

RINA2-

DNP

R4

J9

7

RGA+

RINA-

10K

IN-

+IN3

-IN2

10

VM

R49

100K

OPEN

R34

R18

+IN2

6

IN+B

DNP

0

5

HS9-OP470ARH

R17

OPEN

V+

IN

OPEN

RINA+

C9

11

DNP

0

12

V-

R58

10K

-IN4

+IN4

OPEN

C21

R27

-IN1

+IN1

C24

OUTD

IN-D

IN+D

OPEN

R7

R23

J8

IN1+

RREFA+

IN+B

IN-B

OUTB

14

13

OPEN

RINA1+

3

OUT 4

C18

B

2

OPEN

VP

OUT 1

4

IN

DNP

R12

RINA2-

DNP

DNP

OPEN

R22

0

DNP

C8

DNP

R3

R30

R8

1

Application Note 1719

J7

IN-

U1

OUTA

IN-A

IN+A

DNP

R52

DNP

OPEN

RINA-

IN-B

RREFA-

OUT

DNP

R59

0

C22

DNP

R39

100K

R47

R16

J14

VP

100K

10K

R67

R55

DNP

C15

J1

C14

OPEN

OPEN

R33

DNP

OPEN

RGA+

OUT

0.01UF

DNP

OPEN

J13

OUT

0.1UF

C5

C23

IN+A

DNP

0

C3

VM

R56

R15

2

CLOSE TO PART

OUT

0.01UF

0

C17

RINA+

C7

1

1UF

D1

CLOSE TO PART

0.1UF C1

R63

0

OPEN

0

0

R51

C26

C16

10K

0

D2

V+

OPEN

R24

R1

0

R37

R5

R21

6

IN1+

RREFA+

RINA1+

R44

R48

1UF

RREF

C4

A

J6

J2

J3

J4

R32

DNP

100K

2

OPEN

C2

R28

DNP

DNP

1

0

RINA2-

R11

R2

IN-

C6

R20

R6

V-

IN-A

RREFA-

10K

J5

REF1

RINA-

R14

DNP

Submit Document Feedback

HS-OP470ARHEV1Z Schematic Diagram

AN1719.1

March 14, 2013