Reading 2

advertisement

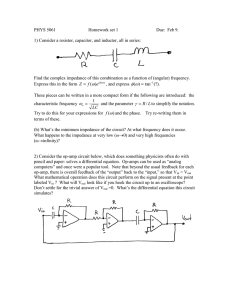

INTRODUCTION

Rarely does one get through a day in Canada without encountering an

electronic device. Since the discovery of the transistor in 1947 by Bardeen,

Brattain and Shockley electronics have transformed our world

http://www.pbs.org/transistor/. It especially important for scientists to

understand electronics as they play a larger role in our lives.

The field of electronics is rapidly evolving and it easy to feel it is impossible

to keep up with the “state of the art”. In fact, the study of electronics can

be split into four parts:

1. Basic physical laws of electricity

2. Circuit analysis techniques

3. Vocabulary to describe electronics

4. Application of electronics

Clearly the underlying physical laws are not changing – so studying them is

worthwhile for understanding the current and future state of the art. The

theory of circuit analysis was developed decades ago and the main new

development is the use of computers to solve more complex circuits. This

area is changing slowly and is required for quantitatively understanding the

state of the art. The vocabulary is always evolving to encompass the new

devices being developed everyday. Twenty years ago terms such as

“Photonics” and “data bus” existed only in science fiction novels. Fortunately

each new generation of terminology builds upon the previous one (e.g. gate ⇒

optical gate) so knowledge of the current terminology will be useful for many

years. Applications of electronics evolve rapidly and many of the details we

will learn in this class will be obsolete in a few years, however, the reasons

for studying the current state of the art are that it is currently useful, it

will help us understand electronics better and it is fun.

ELECTRIC FORCE AND FIELD

General Information:

• The basic unit of Charge is the Coulomb (C).

• The smallest magnitude of charge that can occur outside of a nucleon is

the charge on a single electron = 1.602 × 10 -19 C. (Millikan Oil Drop Exp.)

• Charge can be either positive or negative. Charges of the same sign repel

and charges of opposite sign attract.

r

• A charge, q, generates an electric field, E .

ELECTRIC FORCE - COULOMB’S LAW:

q1

NB: Equal and opposite force on EACH charge!

r

F12

r

r12

r

F21

q2

The direction of the electric force, F12, on q1 due to q2, is given by the signs

r

of the charges and the direction of the position vector r12 , which connects

them. The magnitude is given by Coulomb’s law:

r

kq1q 2

F12 =

2

(r12 )

where the constant k = 8.988 × 109 Nm2C-2 is a related to the permittivity of

free space, ε0, by the relationship : k =(4πε0)-1. This means that Coulomb’s

law as written above, applies only to charges in the vacuum. If the charges

are not in a vacuum then Coulomb’s law takes the form:

kq1q 2

F12 =

2

K (r12 )

where K is the (unitless) dielectric constant for the medium in which the

charges are immersed. For example:

For water

K= 80.4

For air

K=1.007 (WE WILL USE 1.0)

For wood

K=5.0

Example 1

In an evacuated experimental chamber, an α particle (positive charge, Qα = 2

× (1.602 × 10 –19 C) = 3.204 × 10 –19 C) approaches to within 10 nanometers (1

nm = 10-9 m) of an electron (negative charge, Qe = -1.602 × 10 –19 C). What is

the force the particles exert on one another? Is it an attractive or

repulsive force?

Solution The particles attract one another with a force of magnitude,

kQα Q e

F=

2

K (r )

(9.0 × 10 )(3.204 × 10 )(1.602 × 10 )

=

1.0(10 × 10 )

9

−19

−19

−9 2

= 4.619 × 10 −12 N

In vacuum so we use dielectric constant K = 1

ELECTRIC FIELDS:

The reason why a pair of charges experience equal and opposite forces at a

r

distance is that each charge individually creates an electric field, E around

itself. The interaction of a second charge with this electric field gives rise

to the electric force it experiences. For example, a point negative charge

creates straight field lines…

for +ve charge would point outward

The magnitude of the electric field around a point charge, q, is given by:

r

kq

E= 2

Kr

•

•

•

.

k and K have the same values as in Coulomb’s Law.

r is the distance from the charge to the position in question.

units are Newtons/Coulomb, N/C.

E.G. Electric field for a pair of oppositely charged point charges:

A few points about these sketches

r

• E is tangent to the field line at each point

r

• the number of lines per unit cross sectional area (⊥ to E ) is

r

proportional to E the magnitude of the electric field, which is

•

sometimes denoted E, but should not be confused with the energy.

The lines never intersect

For a charge distribution the field is calculated by writing Coulomb’s law for

each small element of charge and summing over the distribution. For a

simple charge distribution such as a pair of parallel plates with equal and

opposing charges separated by a distance, d:

top plate

+ +

+

+

+

+

E = 0

+

+

+

d

E = CONSTANT

- -

-

-

-

-

-

-

-

lower plate

Assuming the plate separation is small compared to their area the resulting

electric field takes a simple form: constant everywhere inside plates and

zero outside.. The magnitude of the field between 2 parallel plates with

voltage, V is:

E = V/d

So, Volts/meter is another unit for electric field. Actual field lines between

plates look like:

Distortion near plate edges caused by finite area of plates…

The direction of the field is that which a small positive test charge would

experience if placed at the same position (try this on diagrams above).

If a charge q1 is brought into an electric field E, then the resulting force on

that charge is,

r

r

F = qE .

The electric field at and the force on a charge point in the same direction

for positive charges and in opposite directions for negative charges.

SUPERPOSITION OF THE ELECTRIC FIELD

If electric fields from different sources are present then the total electric

field is the VECTORIAL SUM of the fields due to each source.

Example 2

A set of plates 10.0 cm apart has 200 V across them. What is the electric

field inside the plates? What is the force on an electron within them?

+

200 V

10.0 cm

0V

electron

Solution

Electric field is constant, V =Ed, for parallel plates: E = V/d = 200/(0.10) =

2000 N/C (or Volts/meter).

The field is straight down. Force on the electron, we use F = qE. Therefore,

F = (1.602 × 10-19) × 2000 = 3.204 × 10-16 N straight down.

ELECTRIC POTENTIAL

Consider a pair of charged plates separated by a distance d with a small

positive charge placed right next to the negatively charged plate.

Final position of q

+ +

+

+

+

+

+

+

+

d

- -

-

-

-

-

-

-

-

Initial position of q

The charge will experience a force with magnitude equal to qE pulling it

straight towards the negative plate (assuming the gravitiational force is

negligible). To lift it at constant velocity an upwards force with magnitude

qE must be applied. The work done against the constant electric force =

force × distance Therefore the work, W, required to move the charge all the

way to the positive plate at the top is,

W = F × d = qEd

This is the electric potential energy acquired by the charge, which clearly

depends on the magnitude of the charge between the plates. Therefore we

define the electric potential, V, which like the electric field does not

depend on the "test charge" placed in between the plates. That is,

V = W/q

The equation above can be considered a definition of the electric potential

and can be rearranged to yield an equation we have seen earlier,

Energy = W = qV.

Also one can infer, since W = qV = qEd that,

V = E d.

for constant fields

For parallel plates it is commonly assumed that the negative plate is a t

potential of zero and therefore the positive plate is at +V. For reference

the electric field near the surface of the Earth is typically E ≈ 100-200 V/m

in fair weather. During thunderstorms E ≈ 104 V/m!

Electric Force is Conservative. The work done moving from A to B depends

only on the position of the end points (not the path between the endpoints).

Corollary: the work done over any closed path is zero.

Potential around a Point Charge

kq

V=

Kr

where K is the dielectric constant. A point of reference must be chosen

where V = 0. For a point charge a distance of infinity (from the point

charge) is assigned a potential V = 0.

To calculate the potential at a point due to a combination of point charges,

simply add the potentials at that point form each charge algebraically. To

calculate the energy or work required to bring a charge, q2, from infinity to

a distance r from another charge, q1, just remember that the work required

to bring q2 to a potential V is,

W = q2V

And the potential around q1 is,

kq1

V=

Kr

Therefore

kq1q 2

W=

Kr

For example if we have several charges arranged as shown below and we

want the potential at point, P:

q1

for several charges:

q2

P

VP = kΣi (qi/ri)

Potential energy of a charge q'

placed at point P:

q3

U = q'V = q'k[Σi (qi/ri)]

Example 3

A classroom demonstration is set up as follows:

A

30.0 cm

20˚

Ball 1

r

B

C

Ball 2

Two spheres of equal mass are each given a

charge; q1 = 5.0 µC and q2 = 3.4 µC. The

30.0 cm long string holding ball 1 is

observed to make a 20 degree angle with

respect to the vertical. What angle will the

string which holds ball 2 make with respect

to the vertical? What is the magnitude of

the electric force pushing the balls apart?

What is the electric field at B, which is

10.0 cm directly below point C? What is

the electric potential at B?

Solution

The balls have equal mass and the electric force on each is equal and

opposite. Therefore, they both hang at the same angle, i.e., 20o with respect

to the vertical. We are given q1 and q2 in the problem. We need the

distance between the balls, r, to determine the force. Using trigonometry:

r = 2(30.0 cm)(sin(20˚)) = 20.5 cm = 0.205 m.

So the force is,

F=

kq1q 2

2

K (r )

(9.0 × 10 )(5.0 × 10 )(3.4 × 10 )

=

−6

9

−6

1.007(0.205)

2

= 3.62 N

To calculate the electric field at B we need the distance, R, shown in the

diagram (the same for both spheres):

r

R

B

10.0 cm

R2 = (r/2)2 + (10.0)2 = (20.5/2)2 + 100.0

⇒ R = 14.3 cm = 0.143 m

To get the electric field at point B the following diagram is useful:

0.205 m

q1

q2

y

0.100 m

θ

B

0.143 m

x

φ

E2

E1

EB

We need the value of θ:

tan(θ) = 0.100/(0.205/2)

θ = 44.3o .

The total electric field at B, EB, is the vectorial sum of the electric field at

B due to q1, E1, and the electric field at B due to q2, E2.

r

r

r

E B = E1 + E 2

The magnitudes of E1 and E2 are given by E = kQ/r2,

(

r

kq1 9.0 ×109 5.0 ×10 −6

E1 = 2 =

2

Kr

1.007(0.143)

= 2.19 ×10 N/C

5

)

.

Calculating the magnitude of E2, similarly, we find that E2 = 1.49 × 10 5 N/C.

The final answer is the vectorial sum of the two electric fields. This means

we add their x components and y components together separately. So…

EBx = E1x + E2x = (2.19cos(44.3) – 1.49cos(44.3)) × 10 5 = 0.504 × 10

5

EBy = E1y + E2y = -2.19sin(44.3) - 1.49sin(44.3) × 10 5 = -2.57 × 10

N/C

5

N/C.

Therefore the magnitude of the electric field at B is,

r

r 2 r 2 1/ 2

E B = E Bx + E By

= 2.62 × 105 N/C

at some angle φ below the horizontal. Using trigonometry:

and therefore,

sin(φ) = 2.57/2.62

φ = 78.8o below horizontal.

The potential at B, VB, is equal to the algebraic sum of the potential at B due

to q1, V1, and the potential at B due to q2, V2, that is,

where,

V B = V1 + V2

kq1

V1 =

Kr

and

kq2

V2 =

Kr

Therefore, since k, K and r are the same for both V1 and V2,

VB =

kq 1 kq 2 k

(q 1+ q2 )

+

=

Kr

Kr Kr

9.0 × 109

=

5.0 × 10 −6 + 3.4 × 10 −6

1.007(0.143)

(

= 0.524 × 106 V

)

.

WORK, POTENTIAL ENERGY AND

ELECTRIC POTENTIAL

1

q

r

E

2

Move charge in electric field - Work is done by electric force, qE. W = -∆U

[or -(U2-U1)]. The existence of this "electric potential" indicates that the

electric force is CONSERVATIVE.

Since,

U = qV → ∆U = q∆V

Therefore,

W = -∆U = -q∆V

EXAMPLE 4

An α particle ( charge = +2e) is moving away from a fixed charge (+Q). At

point, A, which is a distance d from the fixed charge, the potential is 900 V.

By how much does the kinetic energy of the α particle increase as it moves

from A to B - which is 2d away from the fixed charge?

2d

α particle, q = 2e moving away from Q; ∆K = ?

B

d

A

VB = ? = kQ/2d

+Q

VA = 900 V = kQ/d

We see that VA/2 = 450 V = VB

Energy Conservation:

UA + KA = UB + KB

UA - UB = KB - KA

qVA - qVB = ∆K

(2e)(900 - 450) = 900 eV

What if an electron moves from a to b? ∆K = ? ∆PE = ?

DC CURRENT

In direct current (DC) circuits the current is constant, (e.g. a battery) outlets provide AC. Only three quantities define a simple DC circuit,

Electric Potential (V), Resistance (R), and Current (I).

Electric Potential designated with symbol, VAB, is defined in terms of the

work (Energy) required to bring charge, q, from a point A to a point B, WAB.

WAB = qVAB

VAB = WAB/q

Therefore the Electric Potential is in units of Joules/Coulomb which is

defined as a Volt (V). Electric potential is often called the voltage.

Resistance is a property of the material through which the electric

potential is driving the current. Consider a voltage, VAB, across a material

with Resistance, R, as shown in the diagram below:

R

A

B

I

VAB

If R is a constant independent of VAB for a given temperature (ie. The

resistor is made of an Ohmic material) , then the above quantities may be

related using Ohm's law:

VAB = IR .

Ohm's Law

Therefore, the Resistance is given in Volt/Amperes. This unit is known as

the Ohm(Ω).

Current is the flow of charge, Q through a cross sectional area in a time, t.

I = IAV = ∆Q/∆t = dQ/dt

The SI unit for current is the Ampere (A) = (1 Coulomb of positive charge

flowing through a given area per second). In most material the electrons

carry the charge. For e.g. in a copper wire:

Copper atomic cores Collisions of e- → heat → resistance

Cross sectional Area

Direction of Conventional Current

Caused by net "drift velocity" of free electrons

Drift velocity is average of the horizontal components of the electron

velocities. Redrawing the diagram without the ion cores and only the x

component of the average electron velocities (ie. The "drift " velocity):

Cross sectional Area: A

1

v∆t

2

There are N particles in the volume A(v∆t) that will cross through surface 2

within time ∆t and register as "instantaneous" current. Each particle has a

charge q, making the total charge through surface 2 = Nq. Defining, n =

N/(Av∆t) as a number density of charges, each with charge q, per unit

volume, we get that the charge through area 2 is:

IAV = ∆Q/∆t = Nq/∆t = nAv∆tq/∆t = nqAv

For several charge carriers (eg, holes, ions electrons) the total current is a

sum over each type:

I = AΣiniqivi

Whether the circuit is treated as negative current moving in the direction

of the electrons or positive current moving in the opposite direction it

makes no difference mathematically. Therefore, since it is simpler, we will

henceforth consider only the positive flow of charge in problem solving.

EXAMPLE 5 - Calculation of Drift Speed

A copper wire with r = 0.50 × 10-3 m contains n= 8.0 × 1028 conduction e-/m3

(known from the Hall effect) while carrying a current of 2.0 A. What is the

drift velocity of the individual electrons?

I = nqvA

⇒

v = I/(nqπr2) = 2.0 × 10-4 m/s

VERY SLOW!

Conductors and Insulators - CALCULATING Resistance:

Resistance depends on the dimensions and material through which the

current is flowing. For example, consider a conductor with cross-sectional

area, A and length L;

A

L

Then, the resistance

is given by,

R = ρL/A ,

where ρ is the resistivity of the material (found in scientific data tables).

For metals ρ ≈ 10-8 → 10-6 Ωm; for insulators ρ ≈ 10+13 → 10+17 Ωm.

Resistivity depends upon the collisions of the current carriers with the ionic

cores making up the bulk of the material. The ionic core oscillations impede

the flow of electrons and increase with temperature. Therefore resistance

increases with the temperature. Some typical plots are shown below:

Ohmic

semiconductor

superconductor

insulator

ρ

ρ

ρ

conductor

T

T

T

Ohmic materials are defined as those that obey Ohm’s Law. That is (at

constant temperature) resistance is independent of voltage applied. Note

that insulators and conductors are both Ohmic – but with different slope.

ELECTRIC POWER – Joule heating

Consider an element in a circuit as shown below:

I

I

E

a

b

put an element in here through which current flows

•

In time ∆t, charge I∆t ( = ∆Q) passes through element.

•

Work done by electric field…

W

= -q∆V

(= -∆U = -(Ua – Ub))

= - (∆Q)(Vb – Va)

= ∆Q(Va – Vb)

= ∆QVab

= I∆tVab

Therefore, power = W/∆t = I∆tVab/∆t = IVab,

or,

P = IV

units: (J/C)(C/s) = J/s = Watts (W)

Cases:

1)

2)

Ohmic resistors: V = IR give P = I2R; I = V/R gives P = V2/R.

(Joule heating due to resistors)

EMF = P = ε I

SIMPLE CIRCUITS

DC CIRCUITS:

R

A simple DC circuit

I

V or EMF

Kirchoff's rules

1. Net voltage around a closed loop is zero.

2. The current going into a point is equal to

the current leaving it.

With these two rules, the currents (or other unknowns) of many simple

circuits can be calculated.

Generally useful observations:

points connected by a PERFECT conductor are at the same electric potential.

Any arrangement can be reduced to a network arranged in series and

parallel. For resistances connected in series that is,

SERIES NETWORK:

I

R1

R2

R3

A

B

V1

V2

V3

VAB

Since current coming = the current going in for each resistor, they all have

the same current: the total current, I.

The equivalent resistance, Req, for this network is:

VAB = IReq.

Each resistor has a different electric potential across it. Clearly the total

potential difference in going from A to B is:

VAB = V1+V2+V3.

Also, for each resistor;

IR1 = V1

IR2 = V2

So,

IR3 = V3

VAB = I(R1+R2+R3)

∴ Req = R1 + R2 + R3 .

Parallel Network:

R1

I1

R2

I

I

A

I2

R3

I3

V

The equivalent Resistance, Req, such that V= IReq for the three resistor

network shown above is found by applying Kirchoff's second rule at point, A,

I = I1 + I 2 + I 3

Current in

Current out

Also, since all three resistors are in parallel they have the same voltage

across them, V, therefore;

I1 = V/R1

I2 = V/R2

And we can write,

I3 = V/R3

V/Req = V/R1 + V/R2 + V/R3

Dividing by V on both sides, we find the equivalent resistance,

1

1

1

1

=

+

+ .

R R R

Req

1

2

3

This is the equivalent resistance for the network shown above. This means

if the network were part of a complex circuit, the analysis of the circuit

could be simplified by replacing the three resistors R1, R2 and R3 with a

single resistor with the equivalent resistance Req.

EXAMPLE 1: Series/Parallel Resistor Network

Calculate Req for the following combination of Resistors:

R1 = 500 Ω

R2 = 250 Ω

R3 = 1000 Ω

R4 = 600 Ω

The network can be simplified by noting that its resistance is equal to:

1/Req1 = 1/R1 + 1/R2

1/Req2 = 1/R3 + 1/R4

With a little algebra: Req1 = R1R2/(R1 + R2) and Req2 = R3R4/(R3 + R4) by using

the rule for parallel resistors. Since Req1 and Req2 are in series, we can use

the series rule to find the total Resistance of the network, Req. That is Req =

Req1 + Req2 . Therefore,

Req = R1R2/(R1 + R2) + R3R4/(R3 + R4)

Substitution of the given values for the Resistances gives:

Req = 542 Ω.

EXAMPLE 2: Series, Parallel or What? Calculate Req for the

following network. All the conductors are 1.0 Ω.

The wires are assumed to be perfect conductors. Therefore, points

connected by wires can be re-arranged to suggest a solution as long as the

same paths are possible in the new network as the old.

This is very similar to example for, except Req1 has three conductors rather

two. Using the same process to solve for Req, we find that Req = 0.83 Ω.

Symbol List of circuit elements

Battery

Connection

Multi-cell

Battery

No-connection

Resistor

Capacitor

Variable

Resistor

Variable

Capacitor

Variable

Resistor (3 – pole)

Inductor

(Air core)

Inductor

(Iron Core)

DC voltage

source

AC voltage

source

DC current

source

AC current

source

+

-

3V

1Ω

20 Ω

Example 3:

e

f

I2

c

I2

loop 1

5V

I3 = I1 - I2

I1

loop 2

1Ω

I2

I1

a

(a)

(b)

5Ω

I1 - I2

What is the current, I1, through the middle branch?

What is Vab = (Va - Vb)?

d

I1 - I2

b

GENERAL STRATEGY – MESH EQUATIONS: Use Kirchoff's rules and

Ohm's Law to solve for the two unknown loop currents, I1 and I2 then

determine Vab and I3. Take note that although there are three branches

(each with a different current) this method reduces the number of

unknowns to two by implicitly using Kirchoff’s point rule to get rid of I3 (see

below and text pg. 36-40).

(1)

Use Kirchoff's Point Rule (#2) to designate currents. For e.g. at

point c:

I3 = I1 - I2 ⇒ I1 = I2 + I3.

(2)

Use Kirchoff's Loop Rule (#1) on as many loops as required to

generate sufficient equations. Two loops are required from above.

(i)

For loop 1:

going clockwise starting at c

-IR looping in direction of I

-3V - I2 (1 Ω) - I2 (20 Ω) - I1 (1 Ω) + 5V = 0

“-” because going from + to - terminal

⇒ - I1 - 21 I2 = -2 Amps

⇒ I1 + 21 I2 = 2 A

(ii)

[1]

For loop 2: going clockwise starting at c

- 5 V + I1(1 Ω) + (I1 - I2)(5 Ω)

6 I1 - 5 I2 = 5 A

•

•

•

(3)

= 0

[2]

Loop rule works for ANY closed loop.

For e.g., big loop aefba.

Handy if there were more unknowns or as check.

Solve resulting system of equations:

Multiplying equation [1] by -6:

-6 I1 - 126 I2 = - 12 A

[3]

Add [2] and [3]…

-131 I2 = - 7 A

⇒ I2 = -7/-131 = 0.0534 A

Using this value for I2 in equation [1], we find:

I1 = 2 A- 21 I2 = 2 A -21 (7/131) A = 0.878 A.

Therefore the answer to question (a) is:

I1 = 0.878 A

For question (b), Vab = (I1 -I2) (5 Ω) = 4.12 V. This is also equal to Vcd and Vef

because these voltages are all parallel.

Example 4:

R1 = 3 Ω

What is the

current through

the 12 V battery?

R2 = 2 Ω

6V

R4 =

6Ω

12 V

R3 =

7 Ω What current flows

thru the 3Ω

resistor?

R5 = 5 Ω

Simplify diagram:

And draw

Mesh currents

8.2 Ω

6V

We want

I2

6Ω

I1

I2

12 V

5Ω

Apply Kirchoff’s loop rule

Starting in lower right corner of upper loop and moving around it in a counter

clockwise direction.

+8.2 (I1) – 6 + 6 (I1 –I2) = 0

I2 = (14.2/6)I1 - 1

Starting in lower right of lower loop and moving around it in a counter

clockwise direction.

6 (I2 – I1) + 6 + 12 + 5 (I2) = 0

Sub in I2 from above

11I2 + 18 = 6I1

11((14.2/6)I1 - 1) + 18 = 6I1

26.0I1 +7 = 6I1

⇒

I1 = -7/20 = - 0.35 A

Sub I1 into expression for I2

I2 = (14.2/6)(-0.35) – 1 = - 1.83 A

The current thru the 12 V battery = I2 = -1.83 A (Downwards in original

picture). To get the current in the 3Ω resistor we need to re – expand the

circuit…

R1 = 3 Ω

0.35 A

1.48 A

R2 = 2 Ω

6V

12 V

1.83 A

Element

R1

R2

R3

R4

R5

Resistance (Ω)

3

2

7

6

5

R3 =

7Ω

R4 =

6Ω

R5 = 5 Ω

Current (A)

V/R = -0.4/3 = -0.13

V/R = -0.4/2 = -0.2

I1 = -0.35

I1 – I2 = 1.48

I2 = -1.83

Voltage (V)

-12+9.15+2.45 = -0.4

-12+9.15+2.45 = -0.4

IR = - 2.45

IR =

8.88

IR = - 9.15

Using Microcap 7.0 the simplified circuit after Dynamic DC analysis is:

Example 5 – Above problems were warm-up

10 V

1Ω

3Ω

5V

I2

4Ω

2Ω

I3

8Ω

5Ω

7Ω

I1

6Ω

•

Choose I1, I2 and I3. There are 3 independent currents in this problem –

all others depend on those three – check using point rule.

•

To solve 3 unknowns we need 3 equations. Each labeled current loop gives

us one equation.

•

Note that some resistors have more than one current passing thru them.

E.g. 7Ω resistor has BOTH I1 going up and I3 going down.

1)

Loop 1: start in lower left and go clockwise (can start anywhere and go

any direction)

-18I1 + 5I2 + 7I3 = 0

-I1(7) + I3(7) – I1(5) + I2(5) – I1(6) = 0 ⇒

2)

Loop 2: start in lower left and go clockwise

-I2(2) + I3(2) – 5 – I2(3) – I2(4) – I2(5) + I1(5) = 0

⇒

5I1 - 14I2 + 2I3 = 5

3)

Loop 3: start in lower left and go clockwise

-I3(8) – 10 – (I3)1 + 5 - I3(2) + I2(2) - I3(7) + I1(7) = 0

⇒

7I1 - 2I2 - 16I3 = 5

Use Cramer’s Rule – See Chapter 52 of text

This system of 3 equations in 3 unknowns can be solved using linear algebra

For large (3 or more equations) systems of equations, it is much easier to use

Cramer’s rule than regular algebra. For 3 linear equations in 3 unknowns:

7I1 - 2I2 - 18I3 = 5

5I1 - 14I2 + 2I3 = 5

-18I1 + 5I2 + 7I3 = 0

1)

Evaluate determinant for the coefficients of the unknown currents.

“Expanding the determinant”

7

D =

2

5

− 14

− 18 5

− 18

−2

7

= 7

− 14 − 2

5

7

−5

2 − 18

5

7

− 18

2

− 18

− 14

2

⇒ D = 7 (-98 - 10) – 5(14 – (-90)) -18 (4 – 252)

⇒ D = 7 (-108) – 5(104) -18 (-248)

⇒ D = 3188

2)

Replace the coefficients for I1 in the determinant (1st column) with

the numbers on the right hand side of the equations. That is, replace

(7, 5 -18) with (5, 5, 0). For I2 do the same thing to the 2nd column

5

D1

=

2

5 − 14

0

5

− 18

−2

7

= 5

− 14 − 2

5

D1 = 5 (-108) - 5(104) + 0 = -1060

7

−5

2 − 18

5

7

−0

2

− 18

− 14

2

3)

I1 is then given by D1/D = -1060/3188 = - 0.33 A.

The NEGATIVE means I1 goes in opposite direction to that shown in

diagram

4)

A similar process for I2 yields:

7

D2

=

5 − 18

5 5

− 18 0

−2

7

= − 18

5 − 18

5

2

−0

7 − 18

5

2

+7

7 5

5 5

= -1730

I2 is then given by D1/D = -1730/3188 = - 0.54 A

5)

use I1 and I2 to solve for I3

Use third equation…

-18I1 + 5I2 + 7I3 = 0

-18(-0.33) + 5(-0.54) + 7I3 = 0

I3 = -0.47 A

Check answer using outer loop. Start in lower left and go clockwise:

R3

R1

-8I3– 10 – I3 – 3I2 – 4I2 - 6I1 should be = 0

-9I3– 7I2 - 6I1 – 10

= -8(-0.47) – 7(-0.54) – 6(- 0.33) – 10

R8

= -0.01

R7

R4

R6

Very near 0 ⇒ answer is within round off errors. With these mesh currents

can determine the current and voltage through each element of the circuit…

Element R (Ω) Current (A)

Voltage (V)

R1

1

I3 = - 0.47

1(-0.47) = -0.47

R2

2

I2-I3 = -0.54 – (-0.47) = - 0.07 2(-0.07) = -0.14

R3

3

I2 = - 0.54

3(-0.54) = -1.62

R4

4

I2 = - 0.54

4(-0.54) = -2.16

R5

5

I1-I2 = - 0.33 – (-0.54) = 0.21

5(0.21) = 1.05

R6

6

I1 = - 0.33

6(-0.33) = -1.98

R7

7

I1-I3 = - 0.33 – (- 0.47) = 0.14

7(0.14) = 0.98

R8

8

I3 = - 0.47

8(-0.47) = -3.76

Microcap or other software is useful here

Step 1: Construct circuit…

Step 2 – Analyze

VR1 =-6.261–(-5.794) = -0.467

VR2 = -0.944 - 0.793 = -0.151

VR3 = -5.794 – (-4.166) = -1.63

VR4 = -4.166 – (-1.995) = -2.17

VR5 = -0.944-(-1.995) = 1.05

VR6 = -1.995

VR7 = 0.944

VR8 = -3.739

Compare to table of calculated values…

CAPACITORS

Many electric devices are basically resistors (e.g. stoves, light bulbs,

toasters, etc.) or power sources (batteries, power supplies, solar cells…).

Another basic component is the capacitor, which is a device that stores

charge. It has many uses e.g.:

•

•

Frequency tuning on a radio is a variable capacitor

Photographic flash: slow charge - quick release.

A capacitor is typically constructed of two conductors separated by an

insulator. The circuit symbol for a capacitor is:

or

•

•

Normally equal and opposite charges Q and -Q on each conductor

Q depends on area (and shape) of conductors, distance and

insulator between them, and voltage.

A capacitor differs from a battery (which also stores charge) in that its

energy is stored purely in the field between the plates. There are no

electrochemical reactions in a capacitor to restore this field as it depletes.

Capacitance:

C = Q/V

where V ≡ potential difference

between conductors

NB the use of italics to avoid confusion with, Coluombs (C as opposed to C )

Units: Coulomb/Volt ≡ farad (F) (this is a huge unit most capacitors are in

the picofarad range)

Parallel Plate Capacitor

Va

Vb

+

+

+

+

+

+

+

r

E

-

-

-

-

d

-

-

-

Assuming that the area of the plates, A >> d2, where d is the distance

between the plates, we can ignore distortions in the constant electric field

and,

E = σ/ε0 = Vab/d.

By definition σ = Q/A, i.e. charge per unit area. Therefore,

E = Q/(Aε0) = Vab/d.

⇒ Q/Vab = ε0A/d

⇒ C = ε0A/d

(for two plates separated by vacuum)

Energy of a charged Capacitor:

(Work required to charge it)

(Can be shown using calculus)

U = ½CV2 = Q2/(2C) = ½QV

CAPACITORS NETWORKS

Va

a

C1

+

-

Vab = V

b

constant voltage in conductor

Q1

C2

+

-

Q2

Vb

We can treat above capacitor network as a single EQUIVALENT capacitance

(As for resistors):

a

From above:

CEQ

+

-

Vab = V

QEQ = Q1 + Q2

B

Q1 = C 1 V

Q2 = C2V

V across both capacitors

total charge provided by source is Q = Q1 + Q2. Therefore,

CEQ = Q/V = (Q1 + Q2)/V = Q1/V + Q2/V = C1 + C2 .

Or for many capacitors in parallel: C = ΣiCi . Equivalent capacitance in parallel

is determined like equivalent resistance in series.

a

Vab = V

C1

C2

+ Q1

- Q1

+ Q2

- Q2

b

NB: Net charge of this piece

of circuit must = 0.

Therefore, Q1 = Q2

CAPACITORS HAVE

SAME CHARGE = Q.

Voltages, however are now different:

V1 = Q/C1

V2 = Q/C2

(by Kirchoff's loop rule)

V = V1 + V2 = Q/C1 +Q/C2

Treating the above network as a single EQUIVALENT capacitance, we find:

a

From above:

Vab = V

+

-

CEQ = ?

QEQ = Q

QEQ/CEQ = V

Q/CEQ = V

b

Therefore we have two expressions for V = Q/CEQ = Q/C1 + Q/C2. Canceling

the value of Q on both sides we find….

1/CEQ = 1/C1 + 1/C2

i.e.) in series: (CEQ)-1 = Σi(1/Ci)

Equivalent capacitance in series is like equivalent resistance in parallel.

Example 1

C2

a

Vab = 15 V

b

C1 = 1.0 µF

C2 = 2.0 µF

C3 = 3.0 µF

C1

C3

Determine the equivalent capacitance between terminals a and b and

determine the voltage and charge on each capacitor.

a) Equivalent Capacitance: C2 and C3 are in series: Therefore they may be

replaced by a single capacitor with capacitance, C23:

Vab = 15 V

+

C1

C23

+

(1/C23) = 1/C1 + 1/C2

C23 = (1/2.0 µF + 1/3.0 µF)-1 = 1.2 µF

C1 and C23 are in parallel: Therefore their capacitances are added

together to get the total equivalent capacitance:

CEQ = C1 + C23 = 1.0 + 1.2 µF = 2.2 µF

b) Voltages and charges on each capacitor:

For C1: V1 = Vab = 15 V ⇒ Q1 = C1V1 = (1.0 × 10-6 F)(15 V) = 1.5 × 10-5 C.

For C2 and C3: V2 + V3 = Vab (Kirchoff's loop rule) Therefore using Q = CV

for each capacitor:

Vab = Q2/C2 + Q3/C3

But, as we saw in section on series capacitors, each capacitor in series has

the same charge, Q, induced on it (because of electric neutrality of each

piece of conductor). Therefore:

Vab = Q/C2 + Q/C3 = Q(1/C2 + 1/C3) = Q/C23

Q = C23Vab = (1.2 µF)(15 V) = 1.8 × 10-5 C

for C2 and C3

The voltages are found by using Q = CiVi on each capacitor:

V2 = Q/C2 = (1.8 × 10-5 C)/(2.0 × 10-6 F) = 9.0 V

-5

-6

V3 = Q/C3 = (1.8 × 10 C)/(3.0 × 10 F) = 6.0 V

V2 + V3 = 15.0 V (checks)

Now consider the same capacitor except with a jumper wire across C2 as

shown below:

c

a

C2

C1 = 1.0 µF

C2 = 2.0 µF

Vab = 15 V

C1

C3 = 3.0 µF

(as before)

B

C3

d

The jumper wire causes V2 = Vcd = 0. This takes C2 out of the circuit. The

remaining two capacitors are in parallel:

Vab = 15 V

C1

C3

CEQ = C1 + C3 = 4.0 µF

V1 = V3 = 15 V

Therefore Q1 = C1V1 = 1.5 × 10-5 C and Q3 = C3V3 = 4.5 × 10-5 C

DIELECTRICS IN CAPACITORS

Advantages:

• Materials with dielectric constant higher than air reduce electric field in

the capacitor (at same voltage) to stop arcing (dielectric breakdown). The

capacitance is increased for capacitors of the same size.

• Allows the plates a capacitor operating at a given voltage to be placed

closer together (smaller capacitors of same capacitance as "empty" ones).

e.g.:

dielectric strength of air ≈ 8 × 105 V/m

Plastics and Ceramics ≈ 1 × 107 V/m

Q

V0

r

Maximum E supported

Q

r

E0

d0

ceramic, TiO

empty

V

d

-Q

r

E

wax paper

plastic,

-Q

Same plate area, A, and distance d for each capacitor. Assume that both

capacitors have same induced charge, Q. Microscopically:

r

E 0 re-aligns dipoles

r

r

Ed + E0

r

= E

in dielectric

Since E < E0

⇒

⇒

V/d < V0/d

V < V0

electric field is

reduced

Both capacitors have a charge Q = C0V0 = CV upon them. Therefore, if V< V0,

then C > C0. We define the dielectric constant as K ≡ C/C0 > 1. Earlier we

showed that C = ε0A/d for an empty capacitor. Therefore,

C = εA/d = KC0 = Kε0A/d ⇒ ε = Kε0

where ε is the permittivity of the dielectric.

THE RC CIRCUIT

Let's consider a circuit containing both a resistor and a capacitor.

V

( int. r << R)

V

i

open switch

C

close switch at t = 0

R

-q

q

i

i

b

c

a

•

Use lower case i, v, q for time dependent quantities

•

Switch open: no current flows, no charge accumulates on the capacitor

•

When switch closed: battery does work to charge the capacitor to final

charge +Qf and -Qf on the capacitor plates. While charging, current i

flows.

•

Eventually, the capacitor will be fully charged to Qf and the current i will

drop to zero.

•

What is q(t) and i(t)?

We know that:

i = dq/dt

Also:

vac = iR

[1]

and

vcb = q/C

From Kirchoff's loop rule V = vac + vcb

⇒

V = iR + q/C

[2]

Re-arranging [2] we get: CV - q = iRC and substituting for i using [1] we get:

(dq/dt)RC = CV - q

dq/(CV - q) = dt /RC

Integrating over the interval from t = 0 to t = t (during which charge q

grows from zero to q on both sides of the equation;

∫

q

0

t dt

dq

=

CV − q ∫0 RC

− ln(CV − q ) 0

q

t

=

RC

t

0

− ln(CV − q ) − (− ln(CV )) =

t

RC

solving for q, w get;

t

CV − q

− ln

=

CV RC

CV − q

− t/RC

=e

CV

q = CV - CVe − t/RC = CV (1 − e − t/RC )

[3]

At t = 0, the capacitor is uncharged, q = 0, i = I0 ≡ initial current. Therefore

vcb(0) = 0 and,

I0R = V

[4]

At t = ∞, i → 0, q → Qf. Therefore, vac → 0 and

vbc = Qf/C = V

[5]

Using expression [5] in [3] we get the final expression for q(t):

q = Q f (1 − e − t/RC ) .

Checking the limits of the above expression we see that:

1. At t=0 q(0) = Qf (1-1) = 0

2. As t → ∞, q → Qf(1 - 0)= Qf

As expected

Plot q vs. t

q

Qf

Qf/e

RC

t

At t = RC , q = Qf(1 - 1/e) ≈ Qf(1 - 0.368)

RC = time constant (τ) = relaxation time.

For expression describing the current simply use:

i = dq/dt = d/dt[Qf(1 -e-t/RC)]

Therefore;

Q f − t/RC

d

− t/RC

i = (Q f − Q f e

)=0+

e

dt

RC

using [5] and [3] we get

V − t/RC

i= e

= I 0 e − t/RC

R

Plot i vs. t

i

I0

I0/e

t

RC

At t = 0, i = I0

As expected

As t → ∞, i→ 0

At t = RC

i = I0/e

Include a plot of I vs. v to show capacitor is linear

Include a plot of v vs. t to show type of output Microcap will generate

ADVANCED CIRCUIT ANALYSIS

Real vs. ideal sources

We often treat batteries simply as constant voltage differences with no

resistance. Real batteries have (non constant) internal resistance and have a

voltage difference that varies over time:

a

From Kirchoff’s loop rule

ε

b

ε - Ir – IRL = 0

a

t

t

e

r

y

RL

r

b

I

(1)

∴ ε I – I 2r – I 2R L = 0

ε I = I 2r + I 2R L

emf

power

useful work = PL

In actual fact any “real” electronic component also has a small amount of

inductance and capacitance. A real battery might also be depicted as…

However in most real cases the

Inductance and capacitance

Are small enough to neglect

Sometimes even the resistance is

Neglected though it is always present

For a “real” battery with only a voltage an internal resistance….

The voltage at the terminals, or terminal voltage (i.e. Vcd = Vc- Vd)

Vcd =

ε - Ir < ε

As batteries age, ε decreases slightly and r increases a lot

(electrochemical by-products gunk up electrodes)

Therefore by equation (1) above I decreases [from (1) I = ε/(r + RL)].

This means the power in load RL = I2RL goes down as well. The battery is said

to have “less juice”. What happens to batteries in the cold?

Power Matching:

a

From Above

ε

b

ε = I(r + RL) ⇒ I = ε /(r + RL)

PL = I2RL = [ε /(r + RL)]2RL

a

t

t

e

Maximum useful power occurs when:

r

r

dPL/dRL =

RL

d 2

=0

ε 2

2

dRL RL + 2RL r + r

y

b

I

⇒

ε2

d

dRL

RL

2

R + 2R r + r 2 = 0

L

L

1 (R 2 + 2R r + r 2 ) - R (2R + 2r )

L

L

L

L

=0

Using Quotient rule we find that : ε 2

2

2 2

(RL + 2RL r + r )

ε 2

(

r 2 - RL2

R 2 + 2R r + r 2

L

L

)

2

= 0 ⇒ r2 – RL2 = 0 ⇒ RL = r for maximum power output

At the maximum (RL = r), the power output is:

MAX PL = I2RL = [ε /(r + RL)]2RL

= [ε /(2r)]2r = ε2/4r

Therefore for an EMF of 100 V with an internal resistance of 50 Ω, we

would expect the maximum power output to occur at RL = 50 Ω and we would

expect the peak power to be: (100)2/4(50) = 10000/200 = 50 Watts. Below

is a graph of PL vs. RL using the above quantities where it is clear that the

maximum does occur at RL = 50 Ω and that the maximum power output is 50

W.

P

(W)

RL (Ω)

Advanced Circuit Analysis Techniques

Superposition – The current in any branch of a linear circuit is equal to the

sum of the currents produced separately by each source remainder of the

circuit, with all other sources set to zero.

Reciprocity – The partial current in branch x of a linear, dc circuit produced

by a voltage source in branch y is equal to that which would be produced in

branch y by the same source if it were placed in branch x.

Linear Circuit – Circuits involving only elements with voltage-current

relationships that are linear (e.g. resistors, capacitors, inductors).

Thevenin’s Theorem:

any complex network of linear circuit

elements (sources, resistors and impedances) having two terminals can be

replaced by a single equivalent voltage source connected in series with a

single resistor (impedance).

Procedure for using Thevenin’s Theorem:

1. If the circuit to be replaced by the Thevenin equivalent circuit already

has two open terminals, label these terminals VTh. If there is a circuit

element at the point where the circuit is to be studied, remove the

element from the circuit, replace it by an open circuit and label the

terminals VTh.

2. Compute VTh, the voltage at the open terminals

3. Replace all voltage sources in the circuit with short circuits and all

current sources with open circuits. (Conceptually - NOT in the Lab!)

4. Compute RTh, the resistance of the circuit looking back into the output

terminals after making these changes.

5. The network can then be replaced by the Thevenin equivalent circuit:

RTh

VTh

Example 1 – Using Thevenin’s Theorem - or save for Ass. #4?

Given the circuit:

Vin

R1

R2

C1

Where R1 = 6000 (6k) Ω, R2 = 3000 (3k) Ω and C1 = 4.0 × 10-8 F. What is the time

constant for this circuit?

This circuit can be simplified using Thevenin’s Method.

First replace the entire circuit except the capacitor with the Thevenin equivalent circuit so

that a simple RC circuit results for which the time constant can easily be evaluated:

RTh

VTh

C1

This is done in two steps

Step 1 –Compute the Thevenin Equivalent Voltage VTh of the original the circuit

without the capacitor:

R1

i = Vin/(R1+R2)

VTh = iR2 = VinR2/(R1+R2)

R2

Vin

VTh

VTh = Vin(3k)/(6k+3k) = Vin/3

Step 2 –Compute the Thevenin Equivalent Resistance RTh of the original the circuit

without the capacitor by replacing the voltage source in the above circuit with a closed

circuit:

R1

1/RTh = 1/R1 1/R2

1/RTh = 1/6000 1/3000

R2

RTh = 2000 Ω

VTh

The original circuit

R1

Vin

R2

C1

can now be replaced with its Thevenin Equivalent circuit:

RTh

VTh

C1

Where VTh = Vin/3 and RTh = 2000 Ω

The resulting time constant is (RTh)(C1) = (2×103)(4.0×10-8) = 8.0×10-5 s

Using Microcap we find:

When Vin (V1 in diagram above) is set to be a square wave with the following

properties:

V0 = 0

Von = 18V

Time delay to leading edge = 100 µs

Time delay to trailing edge = 600 µs

Total time per pulse =

1 ms = 1000 µs

Then transient analysis of the circuit yields the following v(t) curves.

Note that the time constant in the above curves can be shown to match the

calculated value and that v(2) corresponds to the voltage across the

capacitor.

Norton’s Theorem: any complex network of linear circuit elements (sources,

resistors and impedances) can be replaced by a single equivalent current

source connected in parallel with a single resistor (impedance).

Procedure for using Norton’s Theorem

1. If the circuit has two terminals, connect these by a short circuit. If the

current through some element is to be studied, replace it by a short

circuit.

2. Calculate INor, the current through this short circuit

3. Replace all the voltage sources by short circuits and all the current

sources by open circuits

4. Compute the shunt resistance RNor looking back into the circuit after

making all of these changes. NB RNor = RTh.

5. Finally replace the network by the Norton Equivalent current source.

Norton’s method is not used as often as Thevenin’s method – for an

example see text pages 47 and 50.

If time permits: Do a questions 6-1 to 6-5 in text.

MAGNETIC FIELDS

Magnetic fields,

r

B , are produced by moving charges.

I

Electron orbiting

in atom

nucleus

r

B

r

B

Classical trajectory

Of e- as suggested

r

By e- orbital L .

The angular momentum of electrons in the atom creates magnetic fields.

When aligned, the momenta create permanent magnets:.

North

South

Bar magnet

S

N

However, any current will create a magnetic field. (Magnetic forces in

circuits are therefore a concern). For example:

Inductor with constant current flowing thru it – The strength of the field is

proportional to the magnitude of the current B ≅ µ0NI/x.

I

x

S

N

turns

Notes re: Magnetic fields

•

r

B points from North to South (OUTSIDE OF THE MAGNET)

•

Every magnetic N has a S

•

Unlike poles attract, like poles repel.

The N pole of a magnet points to the Earth's magnetic North. Therefore

r

the geographic North pole is actually a South Magnetic pole. B of Earth ∼

10-4 T: For comparison a strong bar magnet ∼ 0.2 T

•

r

The field lines, tangent to B at each point in space, point in direction of

force on a magnetic North pole

•

r

Number of lines/(unit Area) ∝ B ∝ strength of field

•

r

SI unit for B is Tesla (T)= NA-1m-1. Another unit is Gauss (G): 1 T = 104 G.

ELECTROMAGNETIC INDUCTION

It has been observed

that a magnet moving

towards a loop of wire

induces a current in the

wire.

r

v

•

•

•

•

•

•

Move magnet downwards and current flows

around loop

Move magnet upwards and current flows in

opposite direction

When magnet is stationary with respect to the loop - no current flows.

THERE IS AN INDUCED CURRENT DUE TO AN INDUCED EMF.

The induced EMF, ε, depends on how B changes with time in the loop.

Depends on number of B field lines that intersect the cross sectional

area of the loop. (Defined as MAGNETIC FLUX, ΦB)

FARADAY's LAW OF INDUCTION

The induced emf in a closed loop equals the negative of the time rate of

change of magnetic flux through the loop.

ε = - dΦB/dt .

The direction of the induced current is given by

LENZ's LAW:

Direction of magnetic induction opposes the cause.

B increasing

B

I

B induced

ε

The actual amount of I that flows (and therefore the magnitude of induced

B) depends on the resistance in the wire, that is:

I = ε /R

INDUCTORS

A changing magnetic field will induce a voltage in many electronic

components. However, significant inductance is usually produced by coils of

wire specifically designed for the purpose. Such coils are called inductors.

As discussed above, the induced voltage is proportional to the change in

magnetic flux. For a loop of constant area, the change in flux is proportional

to the change in the magnetic field. The magnetic field is proportional to

the current. Therefore (for fixed geometry) the induced voltage, v(t) is

proportional to the change in current (di(t)/dt). The proportionality

constant linking the two is called, L, the inductance:

v(t) = L di(t)/dt

[1]

This can be re-arranged to give i(t) in terms of v(t):

1

i(t) = ∫ v (t )dt

L

[2]

The unit for inductance is called the Henry (H). Let’s compare inductance

to capacitance:

Q= CV

dQ/dt = I = V dC/dt + C dV/dt

assume constant geometry ⇒ C is constant

⇒ dC/dt = 0

i(t) = C dv(t)/dt

Compare to expression [1]. Integrating the above expressions yields:

1

v(t) = ∫ i(t )dt

C

Note the symmetry between inductance and capacitance. Also notice that

under steady state (DC) conditions, the voltage and current do not change –

hence inductance and capacitance are not studied in courses restricted to

DC circuits.

The RL Circuit

Let's consider a circuit containing both a resistor and a inductor.

V

i

V

A

open switch

B

close switch at t = 0

L

R

i

i

•

Switch open: no current flows, no induced voltage on the inductor

•

Switch closed: Current i flows but induced counter voltage stops current

from instantly reaching steady state value, I = V/R.

•

Eventually, current reaches I, and the counter voltage will drop to zero.

•

What is v(t) and i(t)?

Applying Kirchoff's loop rule: V – iR – Ldi/dt = 0

⇒

V – iR = Ldi/dt

⇒

(V – iR)dt = L di

⇒

dt = L di/(V-iR)

Integrating over the interval from t’ = 0 to t’ = t (during which time current

i’ grows from 0 to i on both sides of the equation;

t

i

dt ′

di′

=

∫0 L ∫0 V − i′R

i

t

1

t′

− ln(V − i′R ) =

R

L0

0

ln(V − iR ) − (ln(V )) = −

tR

L

solving for i, w get;

tR

V − iR

ln

=−

L

V

iR

− tR/L

1 − = e

V

i=

V

(1 − e − tR/L )

R

We see that at t = 0, the current i = 0. As t → ∞, i → V/R, which is the

steady state value of the circuit without the inductor. Therefore inductors

behave as short circuits in Dc circuits (and capacitors behave as breaks in

the circuit). To get the voltage across the inductor we note that v =

L(di/dt)…

v=L

v=

di

d V

= L (1 − e − tR/L )

dt

dt R

VL d

VL d − tR/L

1 − e − tR/L = −

e

= −Ve − tR/L

R dt

R dt

(

)

(

)

Therefore at = 0 the voltage across the inductor is –V and it decays

exponentially to zero as time passes.

Plot i vs. t

i

if = V/R

if/e

t

R/L

At t = R/L , i = V/R(1 - 1/e) ≈ V/R(1 - 0.368)

R/L = time constant (τ) = relaxation time – just like with capacitor.

v Plot v vs. t

t

-V/e

R/L

-V

Plot of v vs. i

V – v – iR = 0 from Kirchoff’s loop rule, where v = L(di/dt)

v(i)

v = -V + iR

As with capacitors

the plot is linear indicating

that inductors are linear

circuit elements.

v = 0 (t = ∞)

i

v = -V (t = 0)

How do these plots

if switch is thrown to B

after a long time?

Complex numbers

It is possible to display AC voltages and other quantities in a concise

notation involving complex numbers….

Consider first the real numbers: 0, -3, π, (18.4)½, etc. are all examples of

REAL NUMBERS shown on the line below…

0

-3

π

(18.4)½

Real numbers include all rational numbers, all algebraic irrationals and all

transcendental real numbers (such as e, and π).

When solving an equation such as x2 + 1 = 0, numbers such as − 1 appear as

solutions, the equation has no REAL solution. However, a great deal of REAL

mathematics could not be proven true without the assumption that a solution

exists. In order to deal with this, the concept of imaginary numbers has

been developed by mathematicians.

−1 = j

− 2 = 2 −1 = 2 j

− 4 = 4 − 1 = 2j

and so on …

Just as for the REALS, we can plot the imaginary numbers on a line.

0

πj (18.4)½j

-3j

Once we allow that imaginary numbers exist a wide doorway has opened. We

have discussed pure imaginary and pure real numbers. What about “mixed”

numbers? All solutions to a quadratic equation ax2 + bx + c = 0 are given by :

x=

− b ± b 2 − 4ac

2a

We may have been told that if b2 – 4ac < 0 there was no solution but now we

see that a “mixed” solution with both a real part and an imaginary part is the

actual result. Such numbers are called COMPLEX NUMBERS.

From our imaginary and real axes we see that the only number that is both

real number and an imaginary number is zero. That is, 0 is the one point in

the intersection between the set of REALS and the set of imaginary

numbers. This suggests that the REAL and IMAGINARY axes can be drawn

perpendicular to one another with an intersection at zero. This gives us a

graphical interpretation of the complex numbers.

2j

j

-4

-3

-2

-1

1

2

3

jy

4

5

x

-j

-2j

The standard or “Cartesian” form for such numbers is z = x + jy. Complex

numbers are clearly two dimensional vectors…

Polar Representation of Complex Numbers: From the diagram above we can

see that the complex numbers may also be represented in polar form:

x = rcosθ

r = z = x2 + y2

y = rsinθ

2j

z = x + jy = r(cosθ + jsinθ)

(modulus or magnitude)

r

j

θ = tan-1(y/x)

(argument or phase)

θ

-4

-3

-2

-1

1

-j

2

3

4

5

Using Euler’s Theorem:

e j(θ ) = cos(θ) + jsin(θ)

It is possible to write complex numbers in exponential form:

rejθ = r(cos(θ) + jsin(θ))

Operations on complex numbers

Complex conjugate: If z = x + jy, then its complex conjugate, z* is:

z* = x – jy

in cartesian form

-jθ

= re

in exponential form

= r(cosθ - jsinθ) in trigonometric form

The magnitude z = (zz*)½ = (x2 + y2)½

Plot zz*.

z

2j

j

-4

-3

-2

-1

1

2

3

4

5

z + z*

-j

-2j

z*

Addition:

z1 + z2 = (x1 + x2) + j (y1 + y2)

Complex numbers add (and subtract) like vectors. Easiest in Cartesian form.

Multiplication:

z1z2 = (x1 + jy1)(x2 + jy2) = (x1x2 – y1y2) + j(x1y2 + y1x2)

Easiest in exponential form: z1z2 = (r1ejθ)( r2ejϕ) = r1r2 ej(θ+ϕ)

Division

z1/z2 = (r1ejθ)/( r2ejϕ) = (r1/r2)ej(θ-ϕ)

V-I in an AC circuit for linear elements

What is voltage when an AC current, i = Imsin (ωt), is driven through a

Resistor:

Capacitor:

v(t) = iR = RImsin(ωt)

1

i(t )dt

C∫

1

= ∫ Imsin(ωt )dt

C

v(t) =

= - (Im/ωC)cos(ωt)

or an Inductor:

v(t) = L di(t)/dt

= L d(Imsin(ωt))/dt

= ωLImcos(ωt)

What is current when an AC voltage, v = Vmsin (ωt), is driven through a

Resistor:

Capacitor:

i(t) = v/R = (Vm/R)sin(ωt)

i(t) = C(dv/dt)

= C[d(Vmsin(ωt))/dt]

= CωVmcos(ωt)

NB sin(θ + π/2) = cos(θ)

+90o out of phase with i(t)

or an Inductor:

1

i(t) = ∫ v(t )dt

L

1

= ∫ Vmsin(ωt )dt

L

Vm

= - ω L cos(ωt )

-90o out of phase with i(t)

See Table 8-1 and 8-2 if you do not want to use calculus every time…

Equations for sinusoidal AC voltage (See pg.56 of text)

V = Vmsin(ωt)

Periodic functions

V = Vmsin(ωt ± φ)

Phase angle

φ = “phase angle” is proportional to shift of function along time axis

“+” or “-” according to direction of lag.

φ/2π = the fraction of a period the function is shifted (if φ is in radians)

If “+” the second voltage is said to “lead” the first by φ.

If “-” the second voltage is said to “lag” behind the first by φ.

Period

The period over which the wave repeats itself is defined as T the period. It

can be calculated from the angular frequency ω = 2πf = 2π/T.

Graphing

If we look at V = V0sin(2πt/T) we can graph it easily.

V

3T/4

+V0

-V0

2T

t

T/4

T/2

T

If we look at V = V0sin(2πt/T + φ) we now can graph it easily.

V

+V0

t

-V0

The entire wave is shifted LEFT by T(φ/(2π)) seconds

AC – ALTERNATING CURRENT

We have now been introduced to circuits with time varying voltage. A

common type of time varying voltage is household power provided by

alternating current – in which voltage and current vary sinusoidally with time.

In North America power is provided in a 60 Hz sinusoidal cycle with root

mean square voltage of 120 V.

Period τ = (1/60) s

+ Vm

v

v = Vmsin(2πt/τ)

t

average value of v = 0

-Vm

Lower case v is used for varying voltage. Although the average v = 0, the

average v2 ≠ 0.

Period τ = (1/60) s

v2 = Vm2sin2(2πt/τ)

Vm2

v2

v2 = Vm2sin2(ωt)

where ω = 2π/τ

(angular frequency)

t

average v

2

=

1

τ

v (t )dt

τ∫

average value over one period

2

0

=

1

τ

τ

2

2

∫ Vm sin (ωt )dt =

0

2

Therefore the average v =

Vm2

τ

Vm2/2.

τ

2

∫ sin (ωt )dt =

0

Vm2

1

[1 − cos(2ωt )]dt = Vm

∫

τ 02

2

τ

2

The square of the maximum voltage/2

A useful quantity to define is the root – mean – square voltage, Vrms or the

square root of the average v2 ,

Vrms = v 2 =

Vm

2

= 120 V in North America.

This means that in the outlets in our homes, the maximum voltage per cycle

is Vm = 2 (120 V) = 170 V.

Phasor (Complex) representation of voltages and currents

A real sinusoidal voltage, v(t) = Vmcos(ωt) can be represented as a

complex number that varies in time:

z = v(t) = Vmejωt = Vm[cos(ωt) + jsin(ωt)]

conjugate = z* = Vm[cos(ωt) - jsin(ωt)]

(zz*) = Vm2[cos2(ωt) - jcos(ωt)sin(ωt) +jcos(ωt)sin(ωt) –j2sin2(ωt)]

= Vm2[cos2(ωt) + sin2(ωt)] = Vm2

Modulus = (zz*)½ = (Vm2)½ = Vm

Argument = ωt

The real part Vmcos(ωt) is the actual observable voltage. The imaginary part

represents the energy transferred to i(t). In the complex plane, at time t,

this looks like:

As the phasor

(complex#)

describing v(t)

sweeps thru

complex plane

-3

-2

2j

Vm

j

Vm

ωt

-1

Real part of v(t)

Varies sinusoidally

v(t + ∆t)

v(t)

1

-j

-2j

2

The modulus Vm is

constant.

ω(t + ∆t)

3

4

The same is true for an AC current: i(t) = Imejωt

2j

Im

j

-3

-2

-1

ω(t + ∆t)

Im

ωt

-j

Real part of i(t)

Varies sinusoidally

i(t + ∆t)

i(t)

1

2

3

4

-2j

Re[i(t)] = Re[Imejωt] = Imcos(ωt) = Imsin(ωt + π/2)

Kirchoff’s Laws and Alternating Current and Voltage

Kirchoff’s laws are also valid for alternating current circuits. The only

constraint is that they are only valid at each instant in time. However,

quantities from different times cannot be considered. Due to the finite

velocity at which electrical signals are physically transferred (they cannot

propagate faster than c), in some circuits “the same instant” is difficult to

define. This concern won’t be addressed even though it is a consideration in

the continent wide power grids. So Kirchoff’s laws are then…

1. At any instant in time, the sum of the voltages around a closed loop = 0

2. At any instant in time, the (current entering a point) = (current leaving)

Take note that the quantities can be handled as complex numbers e.g. i(t):

i2(t)

2j

j

-3

-2

-1

i3(t)

1

i1

i1(t)

2

i2

3

4

i1+i2 = i3

AC POWER CALCULATION:

Instantaneous power consumption: P(t) = i(t) v(t)

FOR RESISTORS:

Assume v= Vmsin(ωt) ⇒ current i = (Vm/R)sin(ωt) = Imsin(ωt).

P = iv = [Imsin (ωt)] [Vmsin (ωt)] = ImVmsin2(ωt)

Average power is determined using similar methods as for the rms voltage…

average P

=

I V

I V sin (ωt )dt =

∫

τ

2

1

τ

m m

2

m m

0

Therefore,

Pavg = IrmsVrms

Also

Vrms = IrmsR

So that

P = (Irms)2R = (Vrms)2/R

I V

= m m = IrmsVrms

2 2

AVERAGE POWER DISSIPATED IN CAPACITORS

AND INDUCTORS:

Assume v= Vmsin(ωt) ⇒ current i = CωVmcos(ωt)

P = iv = [CωVmcos(ωt)] [Vmsin (ωt)]

ωCVm2

= τ ∫0 cos(ωt )sin(ωt )dt

τ

average P

Solve by substitution:

Let x = sin(ωt)

then dx/dt = ωcos(ωt)

dx/ω = cos(ωt)dt

And the integral becomes:

ωCV

ωCV x2

xdx =

∫

average P = τ x1

τ 2

2 x2

m

2

m

x2

x1

2 τ

ωCV (sin(ωt ))

average P = τ

2

=0

0

2

m

A similar proof for inductors yields a zero as well – and it does not depend

on whether the voltage is calculated from the current or the other way

around. No matter how the quantities are calculated the integrand will

always be [sin(ωt) cos(ωt)] . Therefore, capacitors and Inductors do not

DISSIPATE power in a circuit. This is because the energy from the

voltage and current are not dissipated but stored 90o out of phase in the

electric or magnetic field generated by the device.

EXAMPLE 1: A toaster has a 700 W average power consumption. Vrms

= 120. Irms = ?

Pavg = IrmsVrms

Vrms = Irms R

R=?

Therefore, Irms = 700/120 = 5.83 A

Therefore, R = Vrms/Irms = 120/5.83 = 20.6 Ω

Impedance (See pg. 64-65 of text)

If we use complex numbers to describe AC voltages and currents we can

define a quantity called IMPEDANCE, Z = v/i

NB: only true for: i(t) = Imejωt

Resistor:

and

v(t) = Vmejωt

i(t) = v/R = (Vm/R) ejωt

ZR = v/i = [Vmejωt]/[(Vm/R) ejωt] = R

ZR = R

The impedance of a resistor = R, its resistance

i(t) = C(dv/dt)

= C[d(Vmejωt)/dt]

= Cjω Vmejωt = jωCv

Capacitor:

or an Inductor:

ZC

ZC

ZC

= v/i = v/(jωCv)

= 1/(jωC) = j/(ωC)

= -j/(ωC)

i(t)

=

=

ZL

ZL

1

v(t )dt

L∫

Z depends on ω for capacitor

V

1

Vm e jωt dt = m e jωt

∫

L

Ljω

= v/(jωL)

= v/i = v/[v/(jωL)]

= jωL

Impedances are manipulated like complex resistances. Purely resistive loads

are unchanged. Capacitors and inductors become frequency dependent phase

shifting resistors.

Equivalent Impedance ZEQ for Impedances in series

Equals…

Z1

ZEQ

Im

ZEQ

Z2

Z1

ZEQ = Z1 + Z2

Equivalent Impedance ZEQ for Impedances in parallel

Z1

Z2

=

Z2

ZEQ

1/ZEQ = 1/Z1 + 1/Z2

Re

AC Analysis using complex numbers

AC version of OHM’s LAW:

i = Vin/ZEQ

In polar exponential form:

i=

j(ωt + θ )

Ve

ZEQ

=

Ve j(ωt + θ )

ZEQ e jφ

=

Vin

ZEQ e jφ

V

e j(ωt + θ-φ )

=

ZEQ

or also

Vin

i= Z

EQ

=

Vin e j(-φ )

ZEQ

Where :

|ZEQ| = [(Re{ZEQ})2 + (Im{ZEQ})2 ]½ = magnitude of ZEQ in complex plane

and

φ = tan-1(Im{ZEQ}/ Re{ZEQ}) = argument of ZEQ in complex plane

This exactly like OHM’s law for DC resistors except we use the magnitude

of ZEQ rather than R to divide the voltage and the current is shifted -φ out

of phase with the voltage.

So all we have to remember with AC analysis is that the “resistance” is now a

complex number and we need to know both its magnitude and phase to

determine how the complex voltage relates to the complex current.

We will first revisit the RC and RL circuits except that we will now drive

these circuits with a sinusoidal AC voltage rather than with a DC voltage.

The RC circuit with Alternating Current

Let's consider a circuit containing both a resistor and a capacitor.

Vin = Vejωt

i

Vout

R

C

Vout = iR

⇒

need expression for i

From Kirchoff's loop rule:

Starting in upper left and going clockwise:

Vin – iZR – iZC = 0

⇒

i = Vin/(ZR + ZC)

⇒

i = Vin/[ R - j/(ωC)]

⇒

Vout = iR = (Vin) R/[ R - j/(ωC)]

Another way of looking at this is i = Vin/ZEQ

ZEQ = R - j/(ωC)

⇒

phase shift ⇒

and therefore

| ZEQ| = [(R - j/(ωC))( R + j/(ωC))]½ = [R2 + (ωC)-2]½

φ = tan-1[(1/(ωC))/R] = tan-1[(1/(ωCR)]

i = Vin/ZEQ =

V

R2 +

1

ω C2

ej(ωt - φ) = Imaxej(ωt - φ)

2

i(t) is just the input voltage Vin(t) with a magnitude divided by a factor of

|ZEQ| and phase shifted by φ. The frequency ω is unchanged.

This looks like

T = period = 2π/ω

V

T

t

-IMAX

IMAX =

V

φ = tan-1[(1/(ωCR)]

1

R2 + 2 2

ωC

Later we will do an example showing similar concepts in the complex plane…

While such relationship between current and voltage are useful, it turns out

that for many AC circuits (including this one), it is most interesting to study

the GAIN.

GAIN = Ratio of the output voltage over the input voltage = Vout/Vin

For this circuit…

R

1 Vin

G = Vout/Vin = iR/Vin = V

j

j R=

in R −

R−

ωC

ωC

First rationalizing the denominator we find… (see expr. 9-5)

G=

j

R R +

ωC

R − j R + j

ωC

ωC

=

R 2 + jR

ωC

2

R 2 + 1

ωC

=

(1 + j/(RωC ))

1

1+

R ωC

2

In an AC circuit the gain is also a complex number and it is useful to study it

in polar form…

|G| =

R

2

2 1

R

+

ωC

and φ = tan-1(1/(RωC))

The magnitude of the gain can be further simplified…

-2 -½

|G| = (1 + (RωC) )

1

=

1

1+

R ωC

2

As ω goes to infinity in the above circuit, the gain goes to 1. As ω goes to

zero the gain goes to zero. Therefore the above circuit is called a high pass

filter because it only passes high frequencies.

If such a circuit is AC analyzed using Microcap, the following Gain and phase

shift as a function of frequency plots are found….

THE LOW PASS FILTER

If, in the following circuit, the voltage across the capacitor is studied, we

find it has a very different behaviour from the high pass filter above.

Similar to high pass above

Except now we consider

The voltage across

capacitor

Rather than analyze the entire circuit again, we will simply plot v2 vs. time

(the output voltage across the capacitor). Transient analysis on Microcap

yields…

For this circuit, ZEQ = same as above for high pass filter and …

G = Vout/Vin = iZC/Vin =

- j/(ωC )

Vin

j

Vin

R−

ωC

Simplifying the above we find… |G| = ((RωC)2 + 1)-½

j/(ωC )

= -

j

R−

ωC

For the R and C values listed above at 60 Hz this should yield a ratio of the

amplitude of the output voltage over the input voltage of 1/(17)½ which is

what we find in the above transient analysis graph. Calculation of the phase

shift yields…

AC analysis on Microcap gives the following graphs, which show that the

circuit is a low pass filter, suppressing high frequencies and passing low

ones…

|G|

φ

Bode plots for the above circuit

If you plot:

Gain in dB = 10log10(G)

vs Frequency on

on a logarithmic

scale you get a

BODE PLOT

The RL circuit with Alternating Current

Let's consider a circuit containing both a resistors and inductors.

Vin = Vejωt

i

R1

R2

Vout

L2

L1

Let’s determine i = Vin/ZEQ

ZEQ = REQ + jωL1 +

jωL2

Where 1/REQ = 1/R1 + 1/R2

ZEQ =

⇒ REQ =

R1R2

+ jω(L1 + L2)

R1 + R2

R1R2

R1 + R2

2

⇒

| ZEQ| =

R1R2

+ ω 2 (L1 + L2 )2

R1 + R2

phase shift ⇒ φ = tan-1[(ω(L1 + L2)/REQ] = tan-1[(ω(L1 + L2)(R1 + R2)/(R1R2)]

and

i = Vin/ZEQ = (V/|ZEQ|)ej(ωt - φ)

Vout = iREQ

Is the above circuit a low pass or a high pass circuit? – analyze on Microcap

to check….

Result should look like…

The RLC circuit

Applying Kirchoff’s loop rule starting

In the lower left of the circuit and

going clockwise.

R

L

Vin = Ve

Vin(t) – i(t)ZR – i(t)ZL – i(t)ZC = 0

jωt

C

Vin(t) = i(t)(ZR + ZL + ZC) = [ i(t)]ZEQ

Vout

Using expressions for ZR, ZL and ZC

Vin (t )

R + jωL − (j/ωC )

= i(t)

This is more difficult to interpret than in DC case since the relationship

between current and voltage now changes each time the frequency of the

input voltage ω is changed – FOR THE SAME COMPONENTS.

i(t) is clearly a complex number

In polar form… i(t) = Vin(t)/ZEQ = Ve

jωt

ZEQ e jθ

=

V

e j(ωt-θ )

ZEQ

Where |ZEQ| = the modulus of ZEQ = (R2 + (ωL – 1/ωC)2)½

ωL − 1/ωC

And θ = argument of ZEQ = tan-1

R

Vin(t):

Modulus = V

Argument = ωt

Im

Modulus i(t) = V/|ZEQ|

i(t) argument i(t) =ωt + θ

ZEQ

Study limits of ω

V

Vin(t)

ωt

Re

|ZEQ| and θ are constant for fixed components and fixed values of ω.

Therefore as the phasor corresponding to Vin(t) sweeps through the complex

plane, the phasor corresponding to i(t) will be reduced w.r.t. Vin(t) by a

constant factor = |ZEQ|-1 and will lead Vin(t) by a constant phase shift =θ.

These concepts can be applied to any pure AC, RLC circuit (that is a circuit

containing any combination of R, L and C and driven by a purely sinusiodal

input voltage or current) after suitable simplifications have been made using

parallel and series impedance formulae and, if necessary, Thevenin’s method.

Vin (t )

From above: Vout = iZC = ZC

(

)

R

+

j

L

−

j/

C

ω

ω

− (j/ωC )

Vin (t )

(-j/ωC)/[Vin(t)] =

R + jωL − (j/ωC )

(

)

R

+

j

ω

L

−

j/

ω

C

Gain = Vout/Vin =

This is a complex number best plotted in polar form:

1

2

(j/ωC )

− (j/ωC )

Modulus of the Gain = |G| =

R + j[ωL − (1/ωC )] R - j[ωL − (1/ωC )]

|G| =

1

(

ωC R 2 + [ωL − (1/ωC )] 2

= 1/(ωC|ZEQ|)

)

1

2

The phase shift,φ, of the gain can be calculated also and is left as an

exercise. The result is:

1/(ωC ) − ωL

R

φ (ω) = tan −1

The output voltage Vout = GVin. Therefore if Vin is a sinusoidal driving voltage

then Vout will be sinusoidal with an amplitude Vin/|G| and a phase shift, θ.

What is interesting about these circuits is that at a certain frequency, the

circuit resonates and, if the resistance is low enough, the output voltage can

exceed the input voltage.

|G| =

1

(

ωC R 2 + [ωL − (1/ωC )] 2

)

1

2

The circuit resonates at the resonant frequency, ω0, which occurs when:

ω0L – 1/ω0C = 0

⇒

ω0L = 1/ω0C ⇒

1

LC

ω0 =

At resonance:

(ω0)2 = 1/LC

RESONANT FREQUENCY

ZEQ= R

|G| = 1/(ω0CR)

i(t) = Vin(t)/ZEQ = Vin(t)/R – current is in phase with voltage

Vout = i(t)ZC = -jVin(t)/(ω0CR)

Under such conditions:

• if R is zero the voltage gain would go to infinity. C cannot go to zero

because then the circuit does not resonate.

• The power coming out of the circuit does not go to infinity, it is balanced

by the current in the output part of the circuit.

|G| vs. ω plot using Excel

Values of

6

R = 0.2 Ω

C = 1 mF

L = 1 mH

Gain = Vout/Vin

ω = 2πf

NB

4

Gain

Were used

To make this

graph .

5

lim ω → 0

|G| = 1

3

2

1

0

0

500

1000

1500

2000

omega

2500

3000

3500

4000

Transfer Function

In AC circuits we often have an input voltage with a known amplitude, V,