CME-M5 Family

Data Sheet

September 2014

Capital Microelectronics Co., Ltd.

CME-M5 Family Data Sheet

Notes

Copyright © 2014 Capital Microelectronics,

Inc. All rights reserved.

No part of this document may be copied,

transmitted, transcribed, stored in a retrieval

system, or translated into any language or

computer language, in any form or by any

means, electronic, mechanical, magnetic,

optical, chemical, manual or otherwise, without

the written permission of Capital

Microelectronics, Inc. All trademarks are the

property of their respective companies.

Version Part Number

CME-M5DSE08

Contact Us

If you have any problems or requirements

during using our product, please contact

Capital Microelectronics, Inc. or your local

distributors, or send e-mail to

sales@capital-micro.com

Environmental Considerations

To avoid the harmful substances being

released into the environment or harming

human health, we encourage you to recycle this

product in an appropriate way to make sure that

most of the materials are reused or recycled

appropriately. Please contact your local

authorities for disposal or recycle information.

Warranty

The information in this document has been

carefully checked and is believed to be entirely

reliable. However, no responsibility is assumed for

inaccuracies. Furthermore, Capital

Microelectronics, Inc. reserves the right to

discontinue or make changes, without prior notice,

to any products herein to improve reliability,

function, or design.

Capital Microelectronics, Inc. advises its

customers to obtain the latest version of the

relevant information to verify, before placing

orders, that the information being relied upon is

current.

The product introduced in this book is not

authorized for use as critical components in life

support devices or systems without the express

written approval of Capital Microelectronics, Inc.

As used herein: 1. Life support devices or systems

are devices or systems that (a) are intended for

surgical implant into the body or (b) support or

sustain life, and whose failure to perform, when

properly used in accordance with instructions for

use provided in the labeling, can be reasonably

expected to result in a significant injury to the user.

2. A critical component is any component of a life

support device or system whose failure to perform

can be reasonably expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

http://www.capital-micro.com

1

CME-M5 Family Data Sheet

Revision History

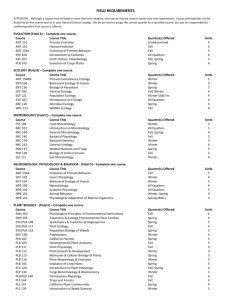

The table below shows the revision history for this document.

Date

Version

June 2012

1.0

Initial release.

July 2012

1.1

First updated.

October 2012

CME-M5DSE03

November 2012

CME-M5DSE04

IO38/MSEL_2->IO39/MSEL_2

EMIF Read Waveform modified

CME-M5DSE05

Update the MSS peripheral information;

Update the Device-package, see Table 2;

Add the information about GUBF, see section GBUF;

Update figures: Figure 1, Figure 24, etc.;

Revise bugs in the manual.

CME-M5DSE06

Add QFN68 Pin Package, see P75 and P79

The Temperature Range in Industrial level is changed

from (TJ = -40°C to +100°C) to (TJ = -40°C to +125°C),

see P82;

In SDR mode, the read port 256x16 does not support the

following write ports:

4K × 1, 2K × 2, 1K × 4 and 512 × 8, see Table 8;

ISCHEADER3 is updated from 0x2A to 0x22, see

ISCHEADER3 = 0x22;

The max TD Junction temperature is corrected from -85°C

to 125°C, see Table 37.

CME-M5DSE07

Update dimensions of LQFP144 Low-profile Quad

Flat-Pack Package Specifications, TQFP100 Thin

Quad Flat-Pack Package Specifications and QFN68

Package Specifications;

Update the 9 Ordering Information;

Correct the formula of PLL configuration in section of

MSS in System Clock Configuration;

Change the Pins of QFN68 Package Pin List:

Pin 20 is changed from IO15_0 to IO15_1;

Pin 21 is changed from IO16_0 to IO16_1;

Pin 22 is changed from IO17_0 to IO17_1;

Pin 23 is changed from IO18_0 to IO18_1;

April 2013

November 2013

March 2014

Revision

Update new device name and FBGA256 package

http://www.capital-micro.com

2

CME-M5 Family Data Sheet

Date

September 2014

Version

Revision

CME-M5DSE08

Update Table 39 Supply Voltage Ramp Rate:

The minimum Supply Voltage Ramp Rate of VCCINT is

changed from 10us to 10ms and the VCCINT must be

powered to threshold before the VCCIO.

Add Figure 38 Power on waveform.

http://www.capital-micro.com

3

CME-M5 Family Data Sheet

Table of Contents

Notes .......................................................................................................................................................... 1

Revision History ....................................................................................................................................... 2

Table of Contents ..................................................................................................................................... 4

Before You Start........................................................................................................................................ 7

About this Guide.................................................................................................................................. 7

CME-M5 Family FPGA Introduction.................................................................................................... 7

1

CME-M5 Family FPGA Features ...................................................................................................... 8

1.1

1.2

2

CME-M5 Family FPGA Feature Summary ........................................................................... 9

Architecture Overview ........................................................................................................ 10

FPGA ................................................................................................................................................ 12

2.1

2.1.1

2.2

2.3

2.3.1

2.3.2

2.3.3

2.3.4

2.4

2.4.1

2.4.2

2.5

2.5.1

2.6

2.6.1

Programmable Logic Block (PLB) ...................................................................................... 12

LP................................................................................................................................... 12

(1) Look-Up Table ............................................................................................................ 13

(2) Register ...................................................................................................................... 13

(3) Carry, Cascade and Arithmetic Logic ........................................................................ 13

LE ....................................................................................................................................... 14

(1) LE Cascade ............................................................................................................... 14

(2) LE Carry and Skip ...................................................................................................... 14

(3) LE Shift....................................................................................................................... 14

Embedded Memory Block .................................................................................................. 14

EMB5K Port Definitions ................................................................................................. 15

EMB5K Operations ........................................................................................................ 16

EMB5K Operation Mode................................................................................................ 17

(1) EMB5K True Dual-port............................................................................................... 17

(2) EMB5K Simple Dual-port ........................................................................................... 18

(3) EMB5K Single-port .................................................................................................... 19

Conflict Avoidance ......................................................................................................... 20

DSP Block........................................................................................................................... 20

DSP Primitive................................................................................................................. 20

DSP Usage Mode .......................................................................................................... 22

(1) Multiplier ..................................................................................................................... 23

(2) Multiplier and adder ................................................................................................... 23

(3) Multiplier and Accumulator......................................................................................... 24

Embedded Single Port SRAM ............................................................................................ 24

SRAM Port Definitions ................................................................................................... 24

Input/output Blocks ............................................................................................................. 25

Pull-Up/Down/Keeper Resistors .................................................................................... 27

http://www.capital-micro.com

4

CME-M5 Family Data Sheet

2.6.2

2.6.3

2.6.4

2.6.5

2.7

2.8

2.8.1

2.8.2

2.8.3

2.8.4

2.9

2.9.1

2.9.2

2.9.3

2.9.4

3

MSS Subsystem .............................................................................................................................. 39

3.1

3.1.1

3.2

3.3

3.4

3.5

3.6

3.7

3.7.1

3.7.2

3.7.3

3.7.4

3.7.5

4

ESD Protection .............................................................................................................. 27

Drive Strength ................................................................................................................ 27

The Organization of IOBs into Banks ............................................................................ 27

The I/Os During Power-On, Configuration, and User Mode ......................................... 28

Interconnect ........................................................................................................................ 28

PLL ..................................................................................................................................... 29

PLL features................................................................................................................... 29

PLL Hardware Description ............................................................................................. 29

PLL Primitive Port Signal Definitions ............................................................................. 30

Clock Feedback Modes ................................................................................................. 32

(1) Internal Feedback Mode (Frequency Synchronous Mode) ....................................... 33

(2) External Feedback Mode ........................................................................................... 33

Global Clock & Reset Resources ....................................................................................... 34

External Crystal Input .................................................................................................... 35

Clocking Infrastructure................................................................................................... 35

GBUF ............................................................................................................................. 36

Clock Switch .................................................................................................................. 37

8051 Instantiation ............................................................................................................... 40

8051 Macro Primitive Description.................................................................................. 40

Multiplex of P Port Pins ...................................................................................................... 42

MSS Clock Description ....................................................................................................... 43

MSS Memory Map .............................................................................................................. 43

MSS External Memory Interface (EMIF) ............................................................................ 44

(1) Synchronous EMIF .................................................................................................... 44

(2) Asynchronous EMIF .................................................................................................. 45

RTC..................................................................................................................................... 46

MSS in System Management ............................................................................................. 47

Device Register ............................................................................................................. 47

ISC Register Frame ....................................................................................................... 48

Extended SFR ............................................................................................................... 48

MSS In System Configuration ....................................................................................... 49

MSS in System Clock Configuration ............................................................................. 51

(1) PLL Configuration ...................................................................................................... 51

(2) GCLK Dynamic Switch .............................................................................................. 51

(3) MSS Clock Dynamic Switch ...................................................................................... 52

Configuration and Debug ............................................................................................................... 53

4.1

Configuration Mode ............................................................................................................ 53

4.1.1

AS Mode ........................................................................................................................ 53

4.1.2

PS Mode ........................................................................................................................ 54

4.1.3

JTAG Mode .................................................................................................................... 55

4.2

SPI Flash ............................................................................................................................ 55

(1) Using embedded SPI-Flash ....................................................................................... 55

http://www.capital-micro.com

5

CME-M5 Family Data Sheet

(2) Using External SPI-Flash........................................................................................... 56

ISC ...................................................................................................................................... 56

Debug ................................................................................................................................. 56

Power-On-Reset (POR) ..................................................................................................... 56

eFUSE Program ................................................................................................................. 57

4.3

4.4

4.5

4.6

5

Security ............................................................................................................................................ 58

5.1

Bitstream Generation Security Level .................................................................................. 58

(1) prot_flagn ................................................................................................................... 58

(2) read_disable0 ............................................................................................................ 59

(3) read_disable1 ............................................................................................................ 59

On-Chip eFuse ................................................................................................................... 59

Embedded SPI-Flash Hidden Bitstream ............................................................................ 59

AES Security ...................................................................................................................... 60

5.2

5.3

5.4

6

DC & Switching Characteristics .................................................................................................... 61

6.1

6.1.1

6.1.2

6.1.3

6.2

6.2.1

6.2.2

6.2.3

6.2.4

6.2.5

7

DC Electrical Characteristics .............................................................................................. 61

Absolute Maximum Ratings ........................................................................................... 61

Power Supply Specifications ......................................................................................... 61

General Recommended Operating Conditions ............................................................. 62

Switching Characteristics ................................................................................................... 65

Clock Performance ........................................................................................................ 66

I/O Performance ............................................................................................................ 66

PLB Performance .......................................................................................................... 66

EMB5K Performance ..................................................................................................... 66

DSP Performance .......................................................................................................... 67

Pins and Package............................................................................................................................ 68

7.1

7.2

7.2.1

7.2.2

7.2.3

7.2.4

7.3

7.3.1

7.3.2

7.3.3

7.3.4

Pins Definitions and Rules ................................................................................................. 68

Pin List ................................................................................................................................ 69

LQFP144 Package Pin List ........................................................................................... 69

TQFP100 Package Pin List ........................................................................................... 72

FBGA256 Package Pin List ........................................................................................... 73

QFN68 Package Pin List ............................................................................................... 76

Package Information .......................................................................................................... 77

LQFP144 Low-profile Quad Flat-Pack Package Specifications.................................... 77

TQFP100 Thin Quad Flat-Pack Package Specifications .............................................. 78

FBGA256-Pin FineLine Ball-Grid Array (FBGA) – THIN – Wire Bond.......................... 79

QFN68 Package Specifications..................................................................................... 80

8

Developer Kits ................................................................................................................................. 81

9

Ordering Information ...................................................................................................................... 82

10

Legends ...................................................................................................................................... 84

http://www.capital-micro.com

6

CME-M5 Family Data Sheet

Before You Start

About this Guide

This guide is only a part of an overall of documentation on CME-M5 family FPGA. It serves as a

technical reference guiding you to be familiar with the CME-M5 family FPGA module with its heart

functions and characteristics.

The CME-M5 Family FPGA consists of CME-M5 C, CME-M5 R and CME-M5 P series FPGA

modules. And this manual is available for all modules contained in this family except where

noted.

For the detailed information of this family module, please go to http://www.capital-micro.com.

Note:

CME-M5 Family FPGA is just a name that replaces the manuals of CME3000-M and CME3000-C FPGA

Data Sheet.

CME-M5 Family FPGA Introduction

CME-M5 family FPGA has C, R and P three series devices.

The C series devices are an intelligent device integrated enhanced 8051 MCU and high performance

FPGA, which can fulfill customized system design and IP protection (128 bit AES). Embedded optimized

RAM confers the highest speed and performance on 8051 processor hardcore. Designers can design

FPGA with CME’s Primace as well as embedded design with third party EDA tool KeilTM conveniently

and quickly. Based on CME-M5 single chip, CAP (Configurable Application Platform on chip) is ideal for

hardware and embedded designers who need a true system-on-chip (SoC) solution that gives more

flexibility than traditional fixed-function microcontrollers and is more cost-efficient than FPGAs-without

the excessive cost of soft processor cores on traditional FPGAs.

The R series devices are with no hard MCU core and P series devices are special for tradition FPGA

application with no hard MCU core and large embedded SRAM.

The three series FPGA can be used widely in industry, medical, communication system,

consumer electronics, etc.

http://www.capital-micro.com

7

CME-M5 Family Data Sheet

1 CME-M5 Family FPGA Features

FPGA

SRAM-based FPGA Fabric

Up to 6144 4-input Look-up Tables, 4096

DFF-based registers

Performance up to 250MHz

Embedded RAM Block Memory

32 4.5Kbit programmable dual-port

DPRAM memory EMB5K blocks

Embedded DSPs block

16 18x18 DSP (MAC) blocks

Clock Network

8 de-skew global clocks

2 PLLs support frequency multiplication,

frequency division, phase-shifting,

de-skew

8 external input clocks, 1 external crystal

clock input

I/O

3.3/2.5/1.8/1.5V LVTTL/LVCMOS support

Programmable Pull-Up, Pull down and

Bus Keeper control

Programmable driver strength: 2, 4, 8, 12,

16 mA

Level slope ratio control

Configuration

MSS

Enhanced 8051 MCU

Reduced instruction cycle time (Up to 12

times in respect to standard 8051),

frequency up to 200MHz

Compatible to 8051 instruction system

Support up to 8MB data/code memory

extension

Support hardware 32/16-bit MDU

On-chip debugger system (OCDS)

8-channel DMA

Embedded SRAM Memory

128KByte single-port SRAM

Data/code unified addressing, flexible

memory configuration

Peripheral

3 16-bit Timers

1 I2C interface

1 SPI interface

Master rate up to 100Mb/s @200MHz

Slave rate up to 25Mb/s @200MHz

2 Full Duplex Serial Interfaces, the rate is

up to 6.25Mb/s @200MHz

Enhanced hardware operation unit

supports multiplication, division, skip and

normalization.

STOP, IDLE Mode Power Management

In System Management

ISC Control

Dynamic clock management in system

Configuration Mode

JTAG Mode

AS Mode

PS Mode

JTAG Interface

JTAG Chip Configuration

JTAG 8051 Debugging

Dynamic/Multi-configuration Image Support

Security

Encrypted Bitstream with 128-bit AES

Based Efuse and SPI Flash security settings

control accessing the device memory

Protection against copying, overbuilding,

cloning and tampering with both of

customer's FPGA and 8051 firmware IP

Package

TQFP-100

LQFP-144

FBGA-256

QFN-68

http://www.capital-micro.com

8

CME-M5 Family Data Sheet

1.1 CME-M5 Family FPGA Feature Summary

Table 1 CME-M5 C Series FPGA Feature Summary

Series

C

R

P

Device (1)

LUT

Programmable

Embedded

Logic

Memory

SRAM

Block(PLB) (2)

Block

(3)

LP

Register

4.5Kb

Max

DSP

Max

Block

PLL

Flash

MCU

User

(4)

I/O

M5C03N0

3072

1024

2048

32

144Kb

128KB

16

2

-

1

186

M5C06N0

6144

2048

4096

32

144Kb

128KB

16

2

-

1

186

M5C03N3

3072

1024

2048

32

144Kb

128KB

16

2

4Mb

1

186

M5C06N3

6144

2048

4096

32

144Kb

128KB

16

2

4Mb

1

186

M5R03N0

3072

1024

2048

32

144Kb

128KB

16

2

-

-

186

M5R06N0

6144

2048

4096

32

144Kb

128KB

16

2

-

-

186

M5R03N3

3072

1024

2048

32

144Kb

128KB

16

2

4Mb

-

186

M5R06N3

6144

2048

4096

32

144Kb

128KB

16

2

4Mb

-

186

M5P03N0

3072

1024

2048

32

144Kb

-

16

2

-

-

186

M5P06N0

6144

2048

4096

32

144Kb

-

16

2

-

-

186

M5P03N3

3072

1024

2048

32

144Kb

-

16

2

4Mb

-

186

M5P06N3

6144

2048

4096

32

144Kb

-

16

2

4Mb

-

186

Note:

(1) C: FPGA + SRAM (used by MCU) + MCU; R: FPGA + SRAM; P: FPGA.

‘N0’: indicates device contains no Flash, ‘N3 ’indicates that device contains 4Mb Flash.

(2) Each CME-M5 PLB contains 4 LPs (Logic parcel). Each LP contains 3 LUTs, 2 registers.

(3) M5CXX series devices: SRAM could only be used by MCU; M5RXX series devices: SRAM could be

used by FPGA.

(4) Each DSP Block contains an 18 x 18 multiplier with 41 bits accumulator, an adder. Each DSP Block

can also support 2 independent 12 x 9 multipliers with 21 bits accumulator.

Table 2 CME-M5 FPGA Device-Package and Available I/Os

Package

TQFP100

LQFP144

FBGA256

QFN68

Pitch(mm)

0.5

0.5

1.0

0.4

Body Size(mm)

16 x 16

22 x 22

17 x 17

8x8

Device

User I/O

User I/O

User I/O

User I/O

M5x03N0

69

100

186

46

M5x06N0

69

100

186

46

M5x03N3

69

100

186

46

M5x06N3

69

100

186

46

http://www.capital-micro.com

9

CME-M5 Family Data Sheet

1.2 Architecture Overview

The CME-M5 FPGA architecture consists of 5 fundamental programmable functional tiles and an

enhanced 8051 MSS. The PLBs, IOBs, EMB, DSPs and PLLs make up the FPGA. The enhanced 8051

and SRAM make up the MSS. The EMB and DSP can be called as special function block (SFB).

Programmable Logic Blocks (PLBs) contain RAM-based Look-Up Tables (LUT-4) to implement

logic and storage elements that can be used as flip-flops. PLBs can be programmed to perform a

wide variety of logical functions as well as to store data.

Embedded Memory Block provides data storage in the form of 4.5K bit dual-port blocks.

DSPs accept two 18-bit binary numbers as inputs and calculate the product. The DSP block

includes special DSP multiply-accumulate blocks.

Phase (PLL) blocks provide self-calibrating, fully digital solutions for distributing, delaying,

multiplying, dividing, and phase shifting clock signals.

Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the

device. Each IOB supports bidirectional data flow plus 3-state operation.

The monocycle enhanced 8051 CPU is used as central processing unit, whose instruction set is

compatible with standard ASM51 completely.

The embedded 128KB SRAM is only used as the 8051 coding and data memory for C Series

devices.

These elements are organized as shown in figure below. A ring of IOBs surrounds a regular array of

PLBs. The CME-M5 family FPGA has a single column of block EMB and DSP in the array. The PLLs and

GCLK_CTRL blocks are positioned at the top and bottom right corner. The 8051 and SRAM memory are

laid out at the right side of the diagram. All these elements include the Xbars that interconnect the

functional elements, transmitting signals among them.

http://www.capital-micro.com

10

CME-M5 Family Data Sheet

IOBs

C1

r31

C2

PLB

PLB

C3

PLB

PLB

C4

PLB

PLB

C5

PLB

PLB

PLB

PLB

C6

PLB

PLB

C7

C8

PLB PLB

200um

PLB

C9

C1

0

PLB

C1

1

PLB

C1

2

PLB

C1

C1

3

4

PLB

300um

PLB

PLB

PLB

PLB

MAC

PLB

C1

C1

C1

C1

C1

5

6

7

8

9

PLB PLB PLB PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

GCLK_Ctrl

PLL

EMB

r30

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

MAC

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r27

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r26

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r29

r28

RTC analog

r32

RTC

Digital

MAC

EMB

MAC

r25

r24

r23

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

MAC

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

64KB SRAM

EMB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r21

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r20

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r19

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r18

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

MAC

8051

PLB

r22

MAC

EMB

MAC

IOBs

r17

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r16

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r15

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r14

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r13

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

IOBs

MAC

EMB

r12

r11

r10

MAC

MAC

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

MAC

r9

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r8

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

r7

64KB SRAM

EMB

SPI

Config /

JTAG

MAC

EMB

r6

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

MAC

r5

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

MAC

EMB

r2

r1

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

GCLK_Ctrl

MAC

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLB

PLL

Efuse ESD

r4

r3

PLB

IOBs

Figure 1 CME-M5 FAMILY FPGA Architecture

http://www.capital-micro.com

11

CME-M5 Family Data Sheet

2 FPGA

The CME-M5 FAMILY FPGA consists of up to 512 PLBs, 32 EMB5K blocks, 16 18x18 DSPs and 2 PLLs.

This chapter describes these element blocks.

2.1 Programmable Logic Block (PLB)

The Programmable Logic Block (PLB) is the fabric basic logic tile that is composed of LE and Xbar. The

PLB is the basic tile of the Fabric. Their organization is shown in the following figure. One LE contains

four interconnected Logic Parcels (LP). The LE constitutes the main logic resource for implementing

synchronous as well as combinatorial circuits.

The Xbar switches and passes the signals between the tile elements.

LP3

LE

LP2

Xbar

LP1

LP0

PLB

Figure 2 PLB Schematic Diagram

The PLBs are arranged in a regular array of rows and columns, as shown in Figure 1.

The CME development software designates the location of a PLB according to its C and R coordinates,

starting in the bottom left corner, as shown in Figure 1. The letter ‘C’ followed by a number identifies

columns of PLBs, incrementing from the left side of the die to the right. The letter ‘R’ followed by a

number identifies the position of each PLB in the CLB row, incrementing from the bottom of the die.

2.1.1

LP

LP is the basic programmable logic element. The LP has the following elements to provide logic,

arithmetic functions, as shown in the figure below.

Three 4-input LUT function generators

Two registers

Carry, cascade and arithmetic logic

http://www.capital-micro.com

12

CME-M5 Family Data Sheet

carry output

shift up/down

dx4b

fast cascade to next LP above

fast cascade to next PLB

din[1:0]

f0[8]

f1[8]

f2[8]

LUT5

Gen

byp[8]

dy[0]

LUT4

di

4_1

qx[4]

shift

din[1]

a_sr

en

4

Cascade Gen

LUT5

Gen

byp[12]

f0[4]

f1[4]

f2[4]

fast cascades

from prev PLB

fy[0]

dx[4]

LUT4C

4_0

din[0]

di

byp[4]

en

f0[0]

f1[0]

f2[0]

Lut5 cascades

from next LP up

0

LUT4

Cascad

e Gen

byp[0]

qx[0]

shift

a_sr

dx[0]

0

fx4b

carry input

shift[1:0]

clk

shift up/down

Figure 3 LP Schematic Diagram

(1) Look-Up Table

The Look-Up Table or LUT is a RAM-based function generator and is the main resource for

implementing logic functions. Each of the three LUTs in a LP has four logic inputs (f0-f3) and a single

output (d). Any four-variable Boolean logic operation can be implemented in one LUT. Functions with

more inputs can be implemented by cascading LUTs that are in one LP or adjacent LPs.

(2) Register

The register is a programmable D-type flip-flop. There are two level multiplexers on the D input select of

the registers. The first level multiplexer selects either the LUT combinatorial output or the bypass signal

byp[x]. The second level multiplexer selects either the first level multiplexer output signal byp[x] or signal

shift. The shift signal is from the next up/down relative register output qx.

The storage element output, qx, offers three possible paths:

Drives the interconnect line directly

Feedbacks to the LUT input

Cascade to the next up/down relative storage element signal shift

(3) Carry, Cascade and Arithmetic Logic

The vertical up cascading from near down LP feeds the LUT0 input, the LUT40 or LUT41 generates the

cascading output. Functions with more inputs can be implemented by cascading LUTs between PLBs.

The carry chain, together with various dedicated arithmetic logic gates, support fast and efficient

implementations of math operations such as adders, counters, comparators, multipliers, wide logic gates,

and related functions. The carry logic is automatically used for most arithmetic functions in a design. The

gates and multiplexers of the carry and arithmetic logic can also be used for general-purpose logic,

http://www.capital-micro.com

13

CME-M5 Family Data Sheet

including simple wide Boolean functions.

The carry input from LUT40 of the near down LP enters the LUT40 and the LUT40 generates the carry

out which can be cascaded to next up LUT40.

2.2 LE

The LE contains 4 LPs and Carry Ship, Register Control circuitry which make LE implement many

complex functions, such as cascading, Carry and Skip, LE Shift. These functions provide higher

performance and lower resources usage than normal LUT implemented because these connections are

hardware logic and connections.

(1) LE Cascade

The LEs can be cascaded vertically and horizontally to implement large and complex functions.

(2) LE Carry and Skip

The LEs can implement flexible carry function with skip 4 and skip 8 fast carry logics.

(3) LE Shift

The LE registers can be cascaded to implement the register shift up or down vertically with next up LE

register.

2.3 Embedded Memory Block

CME-M5 family device supports embedded memory block (EMB), which is organized as one column

total 32 4.5Kbit EMB5K. EMB5K module is a true dual-port memory that permits independent access to

the common EMB block. Each port has its own dedicated set of data, control and clock lines for

synchronous read and writes operations. EMB5K provides the features as below:

4.5Kbits

Mixed clock mode

A, B data width configured independently

Support write data through output

Parity bit. The EMB5K blocks support a parity bit for each byte. The parity bit, along with internal LC,

can implement parity checking for error detection to ensure data integrity. Parity-sized data words

can be used to store user-specified control bits.

Initialization support. The format of initialization file is either .hex or .dat (a hexadecimal number

each line, the number of lines depends on depth of EMB5K). Initialization files initialize EMB5K

memory during configuration.

Two EMB5K cascade

Three Memory Modes available. EMB5K can be configured into the following modes:

- emb_tdp

http://www.capital-micro.com

14

CME-M5 Family Data Sheet

-

emb_sdp

emb_sp

2.3.1

EMB5K Port Definitions

The dual-port primitive EMB5K signals are defined in the following table.

Table 3 EMB5K Port Definition

Port Name

Type

Width

Description

clka

I

1

Input clock for port A

cea

I

1

Chip enable for port A

wea

I

1

Write enable for port A

aa

I

12

Address line for port A

da

I

18

Data input for port A

clkb

I

1

Input clock for port B

ceb

I

1

Chip enable for port B

web

I

1

Wire enable for port B

ab

I

12

Address line for port B

db

I

18

Data input for port B

q

O

18

Memory data q output

wq_in

I

9

Input from paired EMB5K for wide true dual port mode

wq_out

O

9

Output to paired EMB5K for wide true dual port mode

Table 4 EMB5K Parameters

Parameters

Type

Description

string

Port a usage mode setting:

256x18, 512x9, 1kx4, 2kx2, 4kx1, wtdp (wide true dual port)

Default: 256x18

string

Port b usage mode setting:

256x18, 512x9, 1kx4, 2kx2, 4kx1, wtdp (wide true dual port)

Default: 256x18

string

Bypassing of write data from write port to read port enable for port a,

true or false

Default: false

portb_wr_through

string

Bypassing of write data from write port to read port enable for port b,

true or false

Default: false

init_file

string

EMB initial file

Default: “” (No initial file)

operation_mode

string

EMB working mode, just for simulation

true_dual_port, single_port, simple_dual_port

porta_data_width

string

EMB port a data width

modea_sel

modeb_sel

porta_wr_through

http://www.capital-micro.com

15

CME-M5 Family Data Sheet

Parameters

Type

portb_data_width

string

2.3.2

Description

EMB port b data width

EMB5K Operations

Writing data to and accessing data from the EMB5K are synchronous operations that take place

independently on each of the two ports.

When the we and ce signals enable the active edge of clk, data at the d input bus is written to the

EMB5K location addressed by the a lines. There are two write actions which are selected by wr_through

parameter. The write data is also passed to q output bus if the wr_through is true during the writing

process. The q output bus value will be the previous read output value during the writing process if the

wr_through is false. The two operation waveforms are shown in Figure 4 and Figure 5.

clk

ce

we

a

ab

d

0000

q

bb

FFFF

men[ab]

FFFF

mem[bb]

Figure 4 wr_through is false Waveform

http://www.capital-micro.com

16

CME-M5 Family Data Sheet

clk

ce

we

1

a

ab

d

0000

bb

1

q

FFFF

mem[ab]

FFFF

mem[bb]

FFFF

Figure 5 wr_through is true Waveform

2.3.3

EMB5K Operation Mode

(1) EMB5K True Dual-port

EMB5K supports any combination of dual-port operation: two read ports, two write ports, or one read and

one write at different clock frequencies. The following figure shows true dual-port memory configuration.

Port A

Port B

db[]

aa[]

ab[]

wea

clka

EMB5K

da[]

web

clkb

cea

ceb

qa[]

qb[]

Figure 6 True Dual-port Memory Mode

Table 5 Port Descriptions of True Dual-port Memory Mode

Port Name

Type

Description

aa (b)

Input

Port A (B) Address.

da (b)

Input

Port A (B) Data Input.

http://www.capital-micro.com

17

CME-M5 Family Data Sheet

Port Name

Type

Description

qa (b)

Output

wea (b)

Input

Port A (B) Write Enable. Data is written into the dual-port SRAM upon the

rising edge of the clock when both wea (b) and cea (b) are high.

cea (b)

Input

Port A (B) Enable. When cea (b) is high and wea (a) is low, data read from the

dual-port SRAM address aa (b). If cea (b) is low, qa (b) retains its value.

clka (b)

Input

Port Clock.

Port A (B) Data Output.

Table 6 True Dual-port Configurations

B Port

A Port

4K×1

2K×2

1K×4

512×8

4K × 1

√

√

√

√

2K × 2

√

√

√

√

1K × 4

√

√

√

√

512 × 8

√

√

√

√

512×9

256×16

256×18

√

512 × 9

256 × 16

256 × 18

(2) EMB5K Simple Dual-port

EMB5K also supports simple dual-port memory mode: one read port while one write port. The following

figure shows simple dual-port memory configuration.

qr[]

aw[]

ar[]

cew

clkw

EMB5K

dw[]

cer

clkr

Figure 7 Simple Dual-port Memory Mode

Table 7 Port Descriptions of Simple Dual-port Memory Mode

Port Name

Type

Description

dw

Input

Write Data

aw

Input

Write Address

clkw

Input

Write Clock

cew

Input

Write Port Enable. Active high.

http://www.capital-micro.com

18

CME-M5 Family Data Sheet

Port Name

Type

Description

qr

Output

ar

Input

Read Address

cer

Input

Read Enable. Active high

clkr

Input

Read Clock

Read Data

Table 8 Simple Dual-port Configurations

W Port

Read Port

4K×1

2K×2

1K×4

512×8

4K × 1

√

√

√

√

2K × 2

√

√

√

√

1K × 4

√

√

√

√

512 × 8

√

√

√

√

512×9

256×18

√

512 × 9

256 × 16

256×16

√

√

√

√

√

√

256 × 18

(3) EMB5K Single-port

EMB5K also supports single-port memory mode as shown in the figure below.

EMB5K

we

clk

ce

d[]

a[]

q[]

Figure 8 Single-port Memory Mode

Table 9 Pin Description of Single-port Memory Mode

Port Name

Type

Description

d

Input

Write Data

a

Input

Write Address.

we

Input

Write Enable. Active high.

clk

Input

Write Clock.

ce

Input

Port Enable. Active high.

q

Output

Read Data

Table 10 Single-port Configuration

Port

4K×1

2K×2

1K×4

512×8

512×9

http://www.capital-micro.com

256×16

256×18

19

CME-M5 Family Data Sheet

2.3.4

Conflict Avoidance

In the dual-port memory mode, both ports can access any memory address at any time. When both ports

access the same address, the read and write behavior should observe certain clock timing restrictions.

These restrictions are applicable to both synchronous and asynchronous clocks.

2.4 DSP Block

The CME-M5 family devices have one column of 8 DSP MAC tiles. Within the DSP column, a single DSP

tile is combined with extra logic and routing.

dinx

dinx_input_mode

diny

diny_input_mode

+

X

acc_en

dinz_en

mac_out

mac_output_mode

sload

dinz

dinz_input_mode

Figure 9 DSP Block

DSP tile contains an 18 x 18 two’s complement multiplier and a 40-bit sign-extended accumulator, a

function that is widely used in digital signal processing (DSP). Programmable pipelining of input

operands, intermediate products, and accumulator outputs enhances throughput.

DSP provides features as below:

18 x 18 two's-complement multiplier with a full-precision 36-bit result

Flexible 40-bit post-accumulator with optional registered accumulation feedback

Dynamic user-controlled operating modes to adapt DSP functions from clock cycle to clock cycle

Registers, ensuring maximum clock performance and highest possible sample rates with no area

cost

One DSP support 2 independent 12 x 9 multiplier with 21-bit accumulator

2.4.1

DSP Primitive

The following figure shows DSP (MAC) block.

http://www.capital-micro.com

20

CME-M5 Family Data Sheet

MAC

a_dinx[13:0]

a_diny[9:0]

a_dinz[20:0]

a_mac_out[20:0]

a_over_flow

a_sload

a_acc_en

a_dinz_en

clk

rst_n

b_dinx[13:0]

b_diny[9:0]

b_dinz[20:0]

b_mac_out[20:0]

b_over_flow

b_sload

b_acc_en

b_dinz_en

Figure 10 MAC Block

Table 11 Port Definition

Port

Direction

Width

Description

a_dinx[13:0]

I

14

Multiplicand inputs from ixbar to mult A MSBs, 6 bit LSBs

for usage in 18x18 mode.

b_dinx[13:0]

I

14

Multiplicand inputs from ixbar to mult B MSBs.

a_diny[9:0]

I

10

Multiplier input from ixbar to mult A, LSBs of multiplier

input in 18x18 mode.

b_diny[9:0]

I

10

Multiplier input from ixbar to mult B, MSBs of multiplier

input in 18x18 mode.

a_dinz[20:0]

I

21

Ixbar and bypass inputs to mult A post add and post add

LSBs in 18x18 mode.

b_dinz[20:0]

I

21

Ixbar and bypass inputs to mult B post add and post add

MSBs in 18x18 mode.

a_sload

I

1

sloadA, when asserted directly loads the post add input

into the accumulator.

b_sload

I

1

sloadB, when asserted directly loads the post add input

into the accumulator.

a_acc_en

I

1

Accumulator A enable.

http://www.capital-micro.com

21

CME-M5 Family Data Sheet

Port

Direction

Width

Description

a_dinz_en

I

1

Post adder A enable.

b_acc_en

I

1

Accumulator B enable.

b_dinz_en

I

1

Post adder B enable.

a_mac_out[20:0]

O

21

Outputs to oxbar mult A.

b_mac_out[20:0]

O

21

Outputs to oxbar mult B.

a_overflow

O

1

mulA Overflow flag.

b_overflow

O

1

mulB Overflow flag.

clk

I

1

Clock input.

rstn

I

1

Reset input, Active low.

Table 12 Parameter Table

Parameters

Type

mode_sel

string

MAC working mode select, default: 000.

signed_sel

string

Set signed/unsigned multiplication, true or false, default: true.

adinx_input_mode

string

a_dinx input mode setting: bypass or register, default: bypass.

adiny_input_mode

string

a_diny input mode setting: bypass or register, default: bypass.

adinz_input_mode

string

a_dinz input mode setting: bypass or register, default: bypass.

amac_output_mode

string

a_mac_out output mode setting: bypass or register

Default: bypass.

bdinx_input_mode

string

b_dinx input mode setting: bypass or register, default: bypass.

bdiny_input_mode

string

b_diny input mode setting: bypass or register, default: bypass.

bdinz_input_mode

string

b_dinz input mode setting: bypass or register, default: bypass.

bmac_output_mode

string

b_mac_out output mode setting: bypass or register,

Default: bypass.

2.4.2

Description

DSP Usage Mode

The DSP can be used as two dependent 12x9 A-MAC and B-MAC or one 18x18 MAC function. These

MACs have the same functions is shown as Figure 9. The CME Primace® deals with use input width and

maps to 12x9 A-MAC and B-MAC or one 18x18 MAC automatically.

Table 13 Port Description

Port name

Type

Description

clk

Input

Clock, posedge active.

rstn

Input

Reset, active low.

dinx

Input

Multiplier input (Range: 2~18).

diny

Input

Multiplier input (Range: 2~18).

dinz

Input

Input (Range: 2~40).

sload

Input

Accumulate load.

acc_en

Input

Accumulate enable, active high.

dinz_en

Input

Adder enable, active high.

mac_out

Output

Output (Range: 2~40).

http://www.capital-micro.com

22

CME-M5 Family Data Sheet

Port name

Type

overflow

Output

Description

Overflow, 1 overflow; 0 not active high.

Note: The acc_en and dinz_en both are not active if they are both high.

Table 14 Parameter Description

Parameter

Type

Description

signedx_sel

string

“true” dinx input type is signed

“false” dinx input type is unsigned

signedy_sel

string

“true” diny input type is signed

“false” diny input type is unsigned

signedz_sel

string

“true” dinz input type is signed

“false” dinz input type is unsigned

dinx_input_mode

string

" bypass " input directly to multiplier;

" register " input via register

diny_input_mode

string

" bypass " input directly to multiplier;

" register " input via register

dinz_input_mode

string

" bypass" input directly;

" register" input via register

mac_output_mode

string

" bypass" mac output directly;

" register" mac output via register

The x * y multiplier output will be an unsigned result only when both the x and y are unsigned, otherwise

the x * y multiplier output will be a signed and two’s complement result. The mac_out will be an unsigned

result only when both the dinz and multiplier output are unsigned, otherwise the mac_out will be a signed

and two’s complement result.

(1) Multiplier

The following figure describes that the DSP is used as a multiplier which outputs the dinx * diny result.

dinx

dinx_input_mode

diny

X

+

mac_out

mac_output_mod

e

diny_input_mode

Figure 11 Multiplier

(2) Multiplier and adder

The following figure describes that the DSP is used as a multiplier and adder which output the dinx * diny

+ dinz result.

http://www.capital-micro.com

23

CME-M5 Family Data Sheet

dinx

dinx_input_mode

diny

+

X

mac_out

mac_output_mode

acc_en

dinz_en

diny_input_mode

dinz

dinz_input_mode

Figure 12 Multiplier and Adder

(3) Multiplier and Accumulator

The following figure describes that the DSP is used as a multiplier and adder which output the dinx * diny

+ mac_out(n-1) result.

dinx

dinx_input_mode

diny

diny_input_mode

+

X

acc_en

dinz_en

mac_out

mac_output_mode

sload

dinz

dinz_input_mode

Figure 13 Multiplier and Accumulator

2.5 Embedded Single Port SRAM

CME-M5 family device contains an embedded SPRAM. The synchronous SPRAM total size is 128Kbyte

that can be configured as 128x8 or 64x16 mode.

2.5.1

SRAM Port Definitions

The dual-port primitive SPRAM signals are defined in the table below.

Table 15 SRAM Port Definition

Port Name

Type

Width

Description

clk

I

1

Input clock for SRAM, posedge active

cen

I

1

Chip enable for SRAM, active low

http://www.capital-micro.com

24

CME-M5 Family Data Sheet

Port Name

Type

Width

Description

wen

I

1

Write enable for SRAM, active low

addr

I

12

Address line for SRAM

datai

I

8/16

Data input for SRAM

datao

o

8/16

Input clock for SRAM

Table 16 SRAM Parameters

Parameters

Type

Description

data_width

string

SPRAM port data width, “8” or “16”

init_file

string

SPRAM initial file, the suffix name is .dat or .hex

Default: “”

2.6 Input/output Blocks

The Input/output Block (IOB) provides a programmable, bidirectional interface between an I/O pin and

the FPGA’s internal logic. The IOC is the function for an I/O pin. A simplified diagram of the IOC’s

internal structure appears in Figure 14. There are three main signal paths within the IOC: the output path,

input path, and tri-state path. Each path has its own pair of registers that can act as registers. The three

main signal paths are as follows:

The input path carries data from the pad, which is bonded to a package pin, through an optional

programmable delay element directly to the id line. There are alternate routes through a register to

the id line. The id line is lead to the FPGA’s logic.

The output path, starting with od, carries data from the FPGA’s internal logic through a multiplexer

and then a tri-state driver to the IOC pad. In addition to this direct path, the multiplexer provides the

path to registers.

The tri-state path determines when the output driver is high impedance. The oen line carries data

from the FPGA’s internal logic through a multiplexer to the output driver. In addition to this direct

path, the multiplexer provides the option to insert a register. When the oen line is asserted high, the

output driver is high-impedance (Floating, Hi-Z). The output driver is active-low enabled.

The output and tri-state paths entering the IOC have an inverter option. Any inverter placed on

these paths is automatically absorbed into the IOC.

http://www.capital-micro.com

25

CME-M5 Family Data Sheet

id_setn

0

1

id

Q

setn

rxd

D

CK

Qresetn

Level Shifters DOWN

clk

RXD_S

Vddc

Vddio

In

out

id_resetn

VDDIO

Schmitt Trigger

ESD

od

Pull

UP

od_setn

1

0

setn

D

clk

Q

CK

Q

resetn

1

0

2

3 txd

1

0

Single-ended

Transmitter (Driver)

Vddc

Vddio

In

out

Pad

od_resetn

Pull

DOWN

Level Shifters UP

oen

oen_setn

1

0

setn

D

clk

CK

Q

Q

resetn

0

1

Vddc

Vddio

In

out

2

3 txe

1

0

Bus

Beeper

VSS

oen_resetn

Figure 14 IOC

The IOC Symbol is shown in the following figure.

clk

clken

setn

rstn

oen

od

pad

IOC

id

Figure 15 IOC Symbol

Table 17 OC Port Definition

Port

Width

Direction

Description

clk

1

I

IO input clock

rstn

1

I

IO input reset, active low

setn

1

I

IO input set, active low

clk_en

1

I

IO clock enable

oen

1

I

IO output enable, active low

od

1

I

Output data from fabric

id

1

O

Input data from IO

pad

1

IO

IO pad

Parameters

is_en_used

string

Whether external enable is used. Default: false

reg_always_en

string

Register for id/od/oen enable setting. True or false,

default: false

is_rstn_inv

string

Reset input invert enable, true or false, default: false

http://www.capital-micro.com

26

CME-M5 Family Data Sheet

Port

Width

Direction

Description

is_setn_inv

string

Set input invert enable, true or false, default: false

is_clk_inv

string

Clock input invert enable, true or false, default: false

is_od_inv

string

Input data from fabric invert enable, true or false,

default: false

is_oen_inv

string

Output enable invert enable, true or false, default:

false

oen_sel

string

Output enable mux selection control from

bypass/register/vcc(1)/gnd(0)

Default: bypass

od_sel

string

IO input data mux selection control from

bypass/register/vcc(1)/gnd(0)

id_sel

string

IO output to fabric mux selection from

bypass/register

Default: bypass

oen_setn_en

string

Output enable register set enable

oen_rstn_en

string

Output enable register reset enable

od_setn_en

string

IO input register set enable

od_rstn_en

string

IO input register reset enable

id_setn_en

string

IO output register set enable

id_rstn_en

string

IO output register reset enable

2.6.1

Pull-Up/Down/Keeper Resistors

The optional pull-up and pull-down resistors are intended to establish logic High or Low, at unused I/Os.

The pull-up resistor optionally connects each IOB pad to VCCIO and the pull-sown resistor optionally

connects each IOB pad to GND. The resistors are about 50KΩ~100KΩ. Each I/O has an optional keeper

circuit that retains the last logic level on a line after all drivers have been turned off. This is useful to keep

bus lines from floating when all connected drivers are in a high-impedance state. These resistors are

used in a design using the “pull up”, “pull down” and “bus keeper “attributes in Primace .aoc file.

2.6.2

ESD Protection

The Electro-Static Discharge (ESD) protection circuitries protect all device pads against damage from

ESD as well as excessive voltage transients.

The VIN absolute maximum rating in Table 37 specifies the voltage range that I/Os can tolerate.

2.6.3

Drive Strength

CME-M5 I/O current drive strength is programmable 2, 4, 8, 12, 16mA

2.6.4

The Organization of IOBs into Banks

IOBs are allocated among 4 banks, so that each side of the device has one bank, as shown in Figure 1.

For all packages, each bank has independent VCCIO lines. For example, the VCCIO Bank 1 lines are

http://www.capital-micro.com

27

CME-M5 Family Data Sheet

separate from the VCCIO lines going to all other banks.

2.6.5

The I/Os During Power-On, Configuration, and User Mode

With no power applied to the FPGA, all I/Os are in a high-impedance state. The VCCINT and VCCIO

supplies may be applied in any order. Before power-on can finish, VCCINT, VCCIO must have reached

their respective minimum recommended operating levels. At this time, all I/O drivers also will be in a

high-impedance state.

VCCIO and VCCINT serve as inputs to the internal Power-On Reset circuit (POR). When the power is

applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally

asserts the Global Set-Reset (GSR), which asynchronously resets all IOB registers to a pull-up state. A

Low level applied to nCONFIG input also serves as a GSR.

At this point, the configuration data is loaded into the FPGA. The I/O drivers remain in a high-impedance

state (with pull-up resistors) throughout configuration. The signal is released during Start-Up, marking

the end of configuration and the beginning of design operation in the user mode. At this point, those I/Os

to which signals have been assigned go active while all unused I/Os remain in a high-impedance state.

2.7 Interconnect

All the CME-M5 family device tile includes Xbar that is interconnect, also called routing resources and

function element. The Xbar passes signals among the various functional tiles of CME-M5 family devices.

There are four kinds of interconnect: Octal lines, Triple lines, Single lines, and Diagonal lines.

Octal lines span the die both horizontally and vertically and connect to one out of every eight and four

Xbars (see Figure 16).

Triple lines connect to one out of every three, two and one Xbars horizontally and vertically (see Figure

16).

The octal and triple lines are very useful for one driver fanouting several tiles which span different tiles

numbers.

triple

xbar

xbar

xbar

xbar

xbar

xbar

xbar

xbar

triple

xbar

xbar

xbar

octal

xbar

xbar

xbar

xbar

xbar

xbar

octal

Figure 16 Octal and Triple Lines

Single and Diagonal lines directly connect lines route signals to neighboring tiles: vertically, horizontally.

These lines most often drive a signal from a "source" tile to an octal and triple line and conversely from

the longer interconnect back to a direct line accessing a "destination" tile.

http://www.capital-micro.com

28

CME-M5 Family Data Sheet

xbar

xbar

xbar

xbar

xbar

xbar

xbar

xbar

xbar

diagonal

single

Figure 17 Single and Diagonal Lines

2.8 PLL

2.8.1 PLL features

Input frequency:

PFD input frequency:

Output frequency:

VCO operating rang:

Clock bypass mode:

Power supply:

Output clock duty-cycle:

Run power current consumption:

Power down current:

Operation junction temperature:

PLL outputs:

Lock detection output

2.8.2

5~472.5 MHz

5 ~ 325 MHz

10 ~ 450 MHz

600 ~ 1200 MHz

Allow bypass of input clock directly to PLL output

DVDD: 1.0 ~ 1.2V, VDDA: 1.0 ~ 1.2V

45-55%

< 2mA

< 20uA (VDDA), < 10uA(DVDD)

-40 to 125 °C

CO0, CO1, CO2, CO3

PLL Hardware Description

CME-M5 family device contains two PLLs (PLL0 and PLL1) with advanced clock management features.

The main goal of a PLL is to synchronize the phase and frequency of an internal or external clock to an

input reference clock. The PFD produces an up or down signal that determines whether the

voltage-controlled oscillator (VCO) needs to operate at a higher or lower frequency. The output of the

PFD feeds the charge pump and loop filter, which produces a control voltage for setting the VCO

frequency. The loop filter also removes glitches from the charge pump and prevents voltage overshoot,

which filters the jitter on the VCO. A divide counter (m) is inserted in the feedback loop to increase the

http://www.capital-micro.com

29

CME-M5 Family Data Sheet

VCO frequency above the input reference frequency. VCO frequency (fVCO) is equal to (m+1) times the

input reference clock (fIN). The input reference clock (fIN) to the PFD is equal to the input clock (fIN)

divided by the pre-scale counter (N+1). Therefore, the feedback clock (fFB) applied to one input of the

PFD is locked to the fIN that is applied to the other input of the PFD. The VCO output can feed 4

post-scale counters (C[0..3]), while the corresponding VCO output from Top/Bottom PLLs can feed ten

post-scale counters (C[0..3]). These post-scale counters allow a number of harmonically related

frequencies to be produced by the PLL.

The figure below shows a simplified block diagram of the major components of the CME-M5 FAMILY

PLL.

pll_lock

Lock

fREF

fIN

clkin

fVCO

pre-divider

1/(n+1)

PFD

Charg

e

Pump

Loop

Filter

VCO

vco_divide_mod

e

DIV2

8

8

post-divider

1/(c0+1)

clkout0

1/(c1+1)

clkout1

1/(c2+1)

clkout2

1/(c3+1)

clkout3

fFB

1/(m+1

)

loop-divider

fbclkin

operation_mod

e

Figure 18 PLL Block Diagram

The dedicated pin CLK0~CLK3, XIN and OSC (internal configuration oscillator) and FPGA logic feed the

Bottom PLL0 clkin as the PLL clock input. The external feedback fbclkin must come from the dedicated

pin CLK0~CLK3 or internal clkout0 if the PLL is used as external feedback mode. The PLL generates

four clock outputs.

The Top PLL1 is same as the PLL0 only when the clkin and fbclkin are come from the dedicated pin

CLK4~CLK7.

2.8.3

PLL Primitive Port Signal Definitions

CME-M5 family PLLs primitive module port signal definition and parameter table are shown in the table

below. The CME-M5 family PLL can be generated using the Primace wizard.

Table 18 Port Definition

Port Name

Type

Description

clkin

Input

PLL reference clock input

fbclkin

Input

Feedback input to the PLL. Come from the dedicated CLK pin or

PLL clkout0.

clkout0

Output

PLL output 0 driving to the global clocks.

clkout1

Output

PLL output 1 driving to the global clocks.

http://www.capital-micro.com

30

CME-M5 Family Data Sheet

Port Name

Type

clkout2

Output

PLL output 2 driving to the global clocks.

clkout3

Output

PLL output 3 driving to the global clocks.

locked

Output

Lock output from lock detect circuit. Active high

pwrdown

Input

Description

Power down control.

1: Power on PLL

0: Power down PLL (default)

Table 19 Parameter Definition

Parameters

pwr_mode

operation_mode

rst_mode

bandwidth_type

vco_phase_shift

co0_enable

Type

Description

string

PLL power mode.

"always_off": make PLL always stay in power down status

"always_on": make PLL always stay in power on status

"mcu_ctrl": mcu control the PLL power

"fp_ctrl": FP control the PLL power

Default: "always_off",

string

PLL feedback source path.

"internal_feedback": select the internal PLL output as the feedback

source

"external_feedback": select the external dedicated CLK pin as the

source

default: "internal_feedback"

string

PLL reset mode

"auto": chip power on to reset the PLL automatically

"mcu_control": MSS 8051 mcu control the PLL reset

test_control: reserved for chip test

default: "auto"

string

PLL bandwidth setting

"low": filters out reference clock jitter but increases lock time

"medium": default

"high": provides a fast lock time and tracks jitter on the reference

clock source

string

VCO phase shift setting

VCO phase select from the "0", "45", "90", "135", "180", "225",

"270", "315" degree.

default: “0”

string

PLL CO0 output enable

"true": PLL CO0 output enable

"false" PLL CO0 output disable

default : "true"

http://www.capital-micro.com

31

CME-M5 Family Data Sheet

Parameters

Type

Description

string

PLL CO1 output enable

"true": PLL CO1 output enable

"false" PLL CO1 output disable

default : "false"

string

PLL CO2 output enable

"true": PLL CO2 output enable

"false" PLL CO2 output disable

default : "false"

co3_enable

string

PLL CO3 output enable

"true": PLL CO3 output enable

"false" PLL CO3 output disable

default : "false"

multiply_by(M)

decimal

PLL loop-divider setting, range is from 1 to 256

divide_by(N)

decimal

PLL pre-divider setting, range is from 1 to 256

co0_divide_by(C0)

decimal

PLL output 0 counter setting, range is from 1 to 256

co1_divide_by(C1)

decimal

PLL output 1 counter setting, range is from 1 to 256

co2_divide_by(C2)

decimal

PLL output 2 counter setting, range is from 1 to 256

co3_divide_by(C3)

decimal

PLL output 3 counter setting, range is from 1 to 256

co0_delay_by

decimal

PLL output 0 to counter delay the VCO cycles , range is from 0

to255

co1_delay_by

decimal

PLL output 1 to counter delay the VCO cycles , range is from 0 to

255

co2_delay_by

decimal

PLL output 2 to counter delay the VCO cycles , range is from 0 to

255

co3_delay_by

decimal

PLL output 3 to counter delay the VCO cycles , range is from 0 to

255

co0_phase_shift

string

PLL output 0 to counter phase shift to VCO, select from the 8

"0","45","90","135","180","225","270","315" degree phase

co1_phase_shift

string

PLL output 1 to counter phase shift to VCO, select from the 8

"0","45","90","135","180","225","270","315" degree phase

co2_phase_shift

string