MAEZLIN J AVILA-TAYLOR, ID 112003784 Friday, January

advertisement

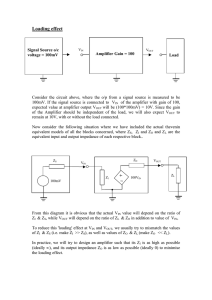

MAEZLIN J AVILA-TAYLOR, ID 112003784 Friday, January 30, Spring 2004 2.3 Lay out (using a path object in LASI or any other layout program) a nominally 250kilo-ohm resistor using the n-well and the serpentine pattern shown in Fig. 2.28. Assume that the maximum length of a segment is 100 and the sheet resistance is 2kiloohm/square. Design rule check the finished resistor. If the scale factor in the layout is 50nm, estimate the fabricated size of the resistor. L=250K*6/2K=750 Setting the Width of the path equal to 6 (the min) Setting all segments to a max of 100 means two horizontal segments will be equal to 100; the other two horizontal segments will be equal to 97, leaving 750-2*100-2*97= 366 to be drawn. Since each corner has only 60% of sheet resistance and there are 6 corners, the total length in corners is 0.6*6*6=21.6 leaving 366-21.6=344.4 to be drawn with vertical segments. There are only 3 vertical segments if we wish to draw a pattern like the one in Fig 2.28. It is impossible to draw 344.4 in length with only 3 segments of max 100. About 44.4 length would be left out of drawing. This results in a loss of 14.8 Kohms. The following figure shows the resulting 235.2Kohm resistor lay out in LASI: 235.2Kohm Resistor with FIGURE 2.28 exact pattern This design passed the DRC check. In order to draw a 250Kohm resistor with a max lenght of a segment 100, the serpentine pattern would have to have more than 3 vertical segments, or we would have to set the width to less than 6 which would not pass the DRC check. The pattern above would result in the 250K. It also passes the DRC check. The width is still 6 which would result in 50nm*6= 300nm. The horizontal length of each segment is 100*50nm=5micro-meters. The total vertical length is 162.5*50nm= 8.1micro-meters Justin Wood EE 4/510 Problem 2.7 2.7) Using the diode of Example 2.3 in the circuit of Figure 2.29, estimate the frequency of the input signal when the AC component of Vout is 707µV (i.e. estimate the 3dB frequency of the Vout/Vin). Figure 2.29 From Example 2.3 Cj = 1.120 pF 0.33 V (1 − D 0.759 V D = −VOUT ≈ −1V − 0.000707V = −1.000707V ∴C j = 1.120 pF − 1.000707 (1 − 0.759 0.33 = 848 fF The transfer function is determined by using the voltage divider as shown below. 1 jωC Vout = Vin 1 R + jωC 1 Vout jωC jωC 1 = = 1 jωC jωCR + 1 Vin R + jωC 1 jω C Vout = Vin 1 R+ jωC 1 1 Vout jωC jωC = = 1 jωC jωCR + 1 Vin R+ jω C Substituting : Vout = 0.000707 Vin = 0.001 0.000707 1 = 0.001 jωCR + 1 0.707 = 1 jωCR + 1 ωCR = 1 ω= f = 1 1 = = 117924528rad / s CR 848e − 15 *10000 ω = 18768271Hz 2π or − 3dB = 1 Vout = Vin jωCR + 1 − 3dB = 20 log10 = 0.707 = 1 jωCR + 1 1 jωCR + 1 ωCR = 1 ω= f = 1 1 = = 117924528rad / s CR 848e − 15 *10000 ω = 18768271Hz 2π By Vehid Suljic Problem 2.10 Estimate the delay through a 1 MEG resistor (10 by 2000) using the values given in Ex. 2.5. Verify the estimate with SPICE. From Ex. 2.5 we have that (10 x 10) square’s parameters are: C = 5 fF and R = 5 kΩ and l = 2000/10 = 200 Now we can estimate the delay through the resistor, td = 0.35 o R o C o (l ^ 2) ≅ 350n sec Figure 1 shows WinSpice plot of Vin and Vout vs. time. From the plot we can see that our delay (Vout is at 50% of Vin = 500mV) is about 400 nsec which is close to what we calculated above. Figure 1. Spice simulation results for problem 2.10 *** Problem 2.10 top level netlist*** .control destroy all run plot vin vout .endc .tran 1n 2u O1 Vin 0 Rload Vout 0 Vin vin 0 Vout 0 1G DC 0 .model TRC R=5k C=5f len=200 .end ltra TRC pulse 0 1 20n 0 KRISHNAMRAJU KURRA HW#3 DATE: 02/02/04 2.14: Estimate the storage time, that is ,the time it takes to remove the stored charge ina diode, when TT = 5 ns, VF = 5V, VR= -5V , Cjo = 0.5 pF and R = 1K. Verify the estimate using SPICE. Given: TT = 5ns VF= 5V VR = -5V Cjo= .5pF R=1k We have: ts = TT .ln[ (iF-iR)/(-iF)] Where iF=VF/R and iR=VR/R Under forward bias the voltage drop across the diode = 0.7V iF = (5 - 0.7)/1K = 4.3 mA When the diode is reversed biased, iR= (-5-0.7)/1K = -5.7 mA ts = 5 ns . ln[ (4.3 + 5.7)/ 5.7] = 2.81 ns Therefore ts = 2.81 ns Verification using Winspice: **8 krishnam- HW#3 Prob:2.14*** .control destroy all run let id= -i(vin)*1k plot vd vin id .endc .tran 100p 25n D1 R1 Vin vd Vin vin 0 vd 0 dtrr 1k Dc 0 pulse 5 -5 10n .1n .1n 20n 40n .Model Dtrr D tt=5E-9 cjo=5E-13 .end Plot showing Vin, Vd, id: