Lab 13: MOSFET differential stage

advertisement

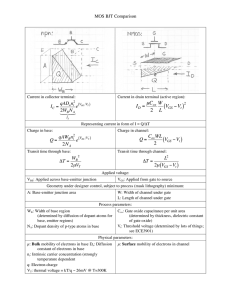

State University of New York at Stony Brook Department of Electrical and Computer Engineering ESE 211 Electronics Laboratory A 2011 ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ Lab 13: MOSFET differential stage 1. Objectives Study and characterize MOSFET-based differential stage: Understand the principles of operation of CS MOSFET amplifier; Understand the principles of operation of differential stage; Measure the differential gain, common mode rejection ratio and frequency response of a MOSFET-based differential amplifier with resistive load. 2. Introduction Transfer characteristics of both MOSFET in common-source (CS) and BJT in common-emitter (CE) configurations look very similar to each other qualitatively. There is quantitative difference though and it is not very surprising since MOSFET and BJT have very different internal structures and operation principles. For instance, BJT’s control electrode BASE have noticeable μA range current flowing into it while MOSFET’s control electrode GATE have zero (in reality not ideal zero but often negligible) DC current, so that the MOSFET DC current gain can be very very big (order of million). A small AC current flows into gate due to charging and discharging of the MOSFET’s gate capacitance. At the same time, in both BJT and MOSFET the output current (drain current in MOSFET and collector current in BJT) saturates over a wide range of output voltages (drain-to-source in MOSFET and collector-toemitter in BJT). The input voltage (gate-to-source in MOSFET and base-to-emitter in BJT) controls the value of this output current; hence the transconductance parameter gm can be introduced for MOSFET in a manner similar to BJT: gm I Dsat i D for VGS > VT, vGS VGS (1) where the parameter VT is called threshold voltage and for the enhancement mode MOSFETs from your lab kit VT is about 0.7 V. It should be noted though, that its similarity to the value of the base-to-emitter voltage in forward active mode of operation of BJT is occasional and MOSFETs can have different thresholds. Also, the slope of the MOSFET transconductance characteristics after the threshold is substantially less steep then that of BJT one. Consequently, one always needs to calculate (or at least to estimate) the value of the so-called overdrive voltage VGS-VT in MOSFET-based circuits, while for BJT-based circuits the value of the base-toemitter voltage can be assumed roughly equal to 0.7 V. The value of the overdrive voltage in n-MOSFET determines the saturation drain current according to equation: W ' VGS VT n , 2 L 2 ID (2) where W is MOSFET gate width, L – channel length and kn’ is transconductance process parameter. The equation (2) is the simplest expression to model the MOSFET current-voltage characteristics in saturation. 1 State University of New York at Stony Brook Department of Electrical and Computer Engineering ESE 211 Electronics Laboratory A 2011 ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ It ignores several important effects including finite output resistance. However, in many cases (2) is enough to perform preliminary estimation of the circuit bias and performance. The expression for voltage gain of MOSFET-based CS gain stage (with source terminal grounded for signal) is similar to that of BJT-based CE gain stage: AV vOUT g m RC , v IN (3) where RC is total resistance connected to drain-to-source current source top terminal (including the output resistance of MOSFET itself). The difference though is in value of transconductance that is usually smaller in MOSFET case. The minus sign indicates that the input and output signals are out of phase. When the source terminal is not grounded for signal (no bypass capacitor introduced across source bias resistor RS, see the lab on CE BJT amp for reference) the gain can often be approximated by: AV vOUT R C , v IN RS (4) In this lab we will study the differential amplifier constructed out of two n-channel MOSFETs in CS configuration (Figure 1). Figure 1 Resistor R1 and DC voltage source V2 bias both MOSFETs with constant equal currents IDsat1 and IDsat21. The input voltage is applied between the gates (floating). It increases the drain current in one MOSFET at the expense of the drain current in another MOSFET: IDsat1 = - IDsat2. In experiment with the CE BJT gain stage we used a resistor in the emitter path to stabilize the DC bias current. This resistor was bypassed with a capacitor to obtain a large voltage gain. The differential stage offers large voltage gain without bypass capacitor thanks to virtual ground at sources for fully differential input. 1 The DC bias current splits equally between transistors M1 and M2 provided both MOSFETs have identical parameters. Load resistor R2 makes almost no difference because of drain current saturation. 2 State University of New York at Stony Brook Department of Electrical and Computer Engineering ESE 211 Electronics Laboratory A 2011 ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ Redistribution of current between M1 and M2 for differential input signal does not change the total current through R1, and the voltage at the MOSFET sources does not change with the input signal (virtual ground for AC). Thus, the bypass capacitor can be eliminated since its function is performed by another transistor. Let us ground the gate of M1 in Figure 1. The output AC voltage will be out of phase with respect to vIN in accordance with equation (3), i.e. the gate of the M2 is an inverting input V-. Let us ground the gate of M2 now, then Vout = - IDsat2R2 = +IDsat1R2. Now the output AC voltage is in phase with vIN, the gate of M1 is a noninverting input V+. In accordance with (3) one can write for AC signal gain: vOUT g m R2 v IN (gate of M2 is on ground) (5) Assume now that the same signal is applied to both inputs simultaneously as shown in Figure 2. Figure 2 The output voltage should not change: vOUT 0 v IN (VIN = V+ = V-) (6) This is one of the most important advantages of the differential structural design – suppression of the common mode signal, i.e. noise or pickup do not get amplified. The ability of differential amplifier to reject the common mode signal while amplifying the differential one is characterized by the common mode rejection ratio (CMRR) – ratio of the differential mode gain to common mode gain. Ideally the differential gain stage amplifies only the voltage difference between the inputs and CMRR is infinite. In reality, spreads in transistor parameters as well as other nonidealities make the CMRR finite. For the particular circuit in Figure 2 the fact that R1 and V2 bias the circuit but not the ideal current source will lead to finite value of the CMRR even for perfectly matched transistors. Hence the bias is better be accomplished by transistor-based current mirror. Generally it is preferred in integrated circuits to eliminate any circuit elements except for transistors on a chip. 3 State University of New York at Stony Brook Department of Electrical and Computer Engineering ESE 211 Electronics Laboratory A 2011 ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ 3. Preliminary lab Sketch the chip layout and show the wiring connections based on the block diagram and pin configuration shown below in Figure 3. Figure 3 You must show the prelab work to the TA before starting the experiment. Please note that source and substrate (PIN V±) are different pins and are always connected in the experiments as in Figure 1. 4. Experiment The experiments will be performed with a 14-pin dual N-channel and dual P-channel matched MOSFET pair (ALD1103PB). The block diagram and PIN configuration are shown in Figure 3. DC measurements 1. Assemble the circuit in Figure 1 using R1 = 1 kΩ and R2 = 2 kΩ. Using DMM perform measurements of DC voltages to find the DC drain current. Show the results to the TA. Differential mode measurements 2. Measure the dependence of the output AC voltage on input AC voltage at an input frequency of 1 kHz using the oscilloscope. Plot the graph and show it to the TA. Determine the range where this dependence is linear and write down the maximum amplitude of undistorted output voltage. Do not exceed this range in the following measurements. 3. Perform measurement of the small signal voltage gain using the oscilloscope at the following frequencies (in Hz): 50k, 100k, 200k, 400k, 800k, 1.6M, 3.2M, and 6.4M. Make sure the output AC voltage does not saturate. Sketch the Bode magnitude plot. Determine the -3dB cut-off frequency and calculated the gainbandwidth product. Common mode and CMRR 4. Rearrange the circuit in accordance with Figure 2. Perform the same measurement as in part 3 for the common mode with an input AC voltage of 100 mV. Calculate the CMRR in dB. Plot the CMRR against frequencies in logarithmic scale. Comment on the change of the CMRR with frequency. Report: The report should include the lab goals, short description of the work, the experimental and simulated data presented in plots, the data analysis and comparison followed by conclusions. Please follow the steps in the experimental part and clearly present all the results of measurements. 4