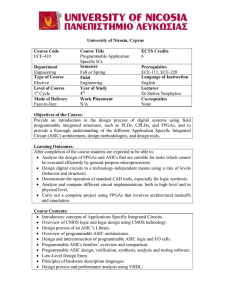

Field Programmable Gate Arrays SYLLABUS

The University of Toledo

EECS:6660/8660:001 Field Programmable Gate Arrays

Dr. Anthony D. Johnson

Lectures TTR 5.45-7:00PM PL-3200

Lab ?? 6:30-8:00PM NE-1026

Office hours MW 10.00-11.00AM NI-2049 s11s_fpga.fm - 1

Field Programmable Gate Arrays

SYLLABUS

Week Starting Subject

1. January 10 Introduction to programmable ASICs: PLDs, CPLDs, and FPGAs.

2.

January 17 Ch.4. Programmable ASICs.

3.

January 24 Ch.5. Programmable ASIC Logic Cells - 5.1 Actel ACT.

4.

January 31 Ch.5. Programmable ASIC Logic Cells - 5.2 Xilinx LCA 204, 5.3 Altera MAX.

5.

February 7 Ch.10/11. High Level Design Entry.

6. February 14 V2MB1000 protoboard and its XC2V1000 FPGA

Xilinx Virtex IV familiy of FPGAs

7.

February 21 Ch.6. Programmable ASIC I/O Cells.

8.

February 28 Ch.8.Programmable ASIC Design Software.

9.

March 14 Altera DE2 Develepment and Education protoboard

10.

March 21 Ch.12. Logic Synthesis. [Term projects assigned; phase #1]

11.

March 28 Ch.13. Simulation. Test Bench. [Project phase #2]

12.

April 4 Ch.7.Programmable ASIC Interconnect. Midterm Exam.

13.

April 11 Ch. 14. Test.[Project phase #3]

14.

April 18 Hardware debugers: ChipScope [Project phase #4]

15.

April 25 Public presentation of projects.

Goals:

Prerequisite:

Textbook:

Grading Policy:

Teacher:

G.A.:

Gainig a general overview and some vendor specific knowledge about FPGAs, as well as a practical experience with industrial grade design automation tools for the FPGA design cycle.

Digital VLSI Design I, or Digital VLSI Design II.

Michael S. Smith: Application Specific Integrated Circuits, Addison-Wesley,1997. (This same book is the course textbook for EECS:4630/5630 Physical Design of VLSI circuits and a Suggested reading book for EECS:4610/5610 Digital VLSI Design I.

Homeworks /Lab/ Midterm /Project = 12 /10/ 38 / 40.

Dr. Anthony D. Johnson, office NI-2049; phone: X-8176; email: anthony.johnson@utoledo.edu.

Ms.

The University of Toledo

EECS:6660/8660:001 Field Programmable Gate Arrays

Dr. Anthony D. Johnson

Lectures TTR 5.45-7:00PM PL-3200

Lab ?? 6:30-8:00PM NE-1026

Office hours MW 10.00-11.00AM NI-2049 s11s_fpga.fm - 2

Homework Schedule

4 o

5 o

6 o

Hwk# topic

1 o week assigned

Organizing the Course File System in the student Environment 1

2 o

3 o

Creating a Logic Model using the FrameMaker Editor 2

Using Language Templates: Hex to 7-Segment converter module.3

Introduction to Altera’s Quartus II Software System

Functional and Timing Simulation

Test Bench

4

5

8

Lab Schedule

Lab# Topic

1o

2o

3o

4 o

5 o

Quartus II schematic entry

Implementing Counters

Implementing Adder/Subtractor

DE2 System Interfaces: 7-segment & LCD panel

Memory implementation in Quartus II week assigned

8

9

6

7

11 week due

2

3

4

5

6

9 week due

7

8

9

11

12

Policy on the submission of Homework and Lab reports

1. To encourage a high quality work, and the successful completion of the term projects, up to one resubmitting of the reports will be accepted for full credit in the week following the regular due week.

2. All homework reports are due at the beginning of the second class of the week.

3. In order to discourage the practice of trying to finish the reports by working in a computer lab during the time scheduled for classes, the absolute deadline for turning in the reports is five minutes after the time scheduled for the beginning of the class.

4. All late submissions are accepted under equal terms until the beginning of the first class of the next week.

5. This policy promotes good working habits. Therefore, the fact that the server was down the morning before the second class of the week does not make a case for delaying the due time. Computers will always go down on us from time to time, we ought to be prepared for the day when it happens.