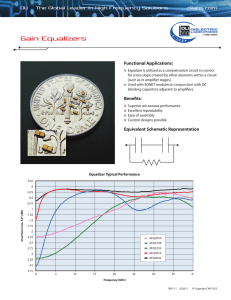

Eye opening monitor for optimized self-adaptation of low

advertisement