EECS 713 Homework # 5

advertisement

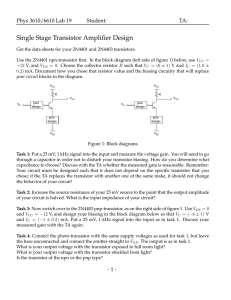

EECS 713 Homework # 5 (200 POINTS) Attached is a description and functional block diagram for a bit-error-rate tester (BERT) taken from the GigaBit Logic Databook. [Note: The device under test (DUT) may be a communications system, therefore this should be accessed through two connectors – one to output the pseudorandom serial data stream, the other to receive this serial data stream.] Your assignment is to complete the BERT design using ECL components from Micrel-Synergy Semiconductor. Information is available online at http://www.micrel.com The specific replacements of the GigaBit parts with Micrel-Synergy parts are: 100E141 (Shift Register) in place of the 10G022, 100E107 (Ex-OR) in place of the 10G002, 100E166 (9-bit Comparator) in place of the 10G045, and 100E101 (OR/NOR) as the clock gate. Specific deliverables under this assignment include: A) a complete schematic of the circuit including all reference designators and pin numbers. (50 PTS) B) a printed circuit (PC) board stack design that includes at least one ground plane, at least one VEE (-4.7 V) plane, at least one VTT (-2 V) plane, and at least two stripline routing layers. This board stack design should be documented as shown in figure 5.26, page 220 in the text. All signal traces will be routed on the internal stripline layers. (10 PTS) C) a set of routing design rules including: 50-ohm stripline transmission line width; pitch for a 50-ohm stripline transmission line with signal traces separated by three trace widths; and the required signal via diameters. (10 PTS) D) component placement and trace routes drawn at a scale of at least 2:1, i.e., a drawing element of 2" represents an actual feature size of 1". Be sure to include the component reference designators and pin 1 indicators. The trace width, tiny capacitors, and tiny resistors need not be drawn to scale. Determine the appropriate placement and values for the bypass and decoupling capacitors, and the appropriate placement for the termination resistors (chip resistors). (70 PTS) E) an analysis determining the worst-case, maximum operating frequency for the BERT including a timing diagram. (20 PTS) F) an analysis determining worst-case current requirements for each power supply. (10 PTS) G) a list of materials for this assembly. (10 PTS) H) an analysis of the cooling requirements. (20 PTS) Miscellaneous information For all ECL devices use the 28-lead PLCC. The ambient temperature range of interest is +25C (room temperature). All components are to be surface mount (no through-hole devices) and component placement is restricted to the top surface. The basic PC board layer has the following properties - thickness 0.010 inches, relative dielectric constant of 4.8, one ounce copper metal on both sides. Neatness counts ! Use of computer aided design tools is encouraged, though not required. PACKAGING INFORMATION SYNERGY SEMICONDUCTOR THERMAL MANAGEMENT SYNERGY SEMICONDUCTOR Semiconductor devices dissipate heat while operating. Device junction temperature is a function of : (1) the amount of power dissipated in the circuit, and (2) the net thermal resistance between the heat source and a reference point such as the surrounding ambient of still air. It has been well understood that the long-term reliability of a semiconductor device is a function of the junction temperature at which it is operated. It is, therefore, necessary to consider the thermal resistance of the IC package before mounting on to a printed circuit board. The thermal resistance of a package is a measure of the package’s ability to transfer heat from the device junction to the surrounding environment. The basic formula for the converting power dissipation to estimated junction temperature is as follows: TJ = TA + PD θJA or TJ = TA + PD (θJC + θCA) where: TJ = Device junction temperature, oC TA = Ambient temperature, oC PD = Power dissipation, Watt θJA = Thermal resistance, junction to ambient, oC/W θJC = Thermal resistance, junction to case (package), o C/W θCA = Thermal resistance, case to ambient, oC/W It is very important for user to understand all of the variables that contribute to junction temperature. The variables are both supplier and user defined. The variables controlled by the supplier include package design, packaging materials, die size and die attach method. Ambient temperature, air flow and related cooling techniques are the user controlled variables. However, printed circuit board substrate material, layout density, size of the airgap between the board and the package, amount of exposed copper interconnect, use of thermally-conductive epoxies and the number of boards in a system, can all have significant impacts on thermal performance of a system. The typical θJC and θJA values are listed in Table 1 for reference only. θJC and θJA may vary depending upon the variables mentioned above. © 1998 Synergy Semiconductor Corporation 10-2 Table 1. Thermal Resistance (oC/W) Package Cerdip Leads θJC θJA @ still air 24 8 58 Cerpack 24 4 130 Sidebraze 28 10 45 Flatpack 132 1.5 45 PDIP 28 18 50 SOIC 8 79 160 SOIC .150” 16 45 130 SOIC .300” 16 38 105 SOIC 20 30 90 SOIC 24 28 85 SOIC 28 25 80 PLCC 28 24 70 PLCC 32 22 67 PLCC 44 17 56 MQUAD-PLCC 28 8 50 MQUAD-PLCC 44 5 40 MQUAD-QFP 80 4 31 MQUAD-QFP 100 3 27 MQUAD-QFP 128 1.8 22 PQ2 128 0.5 20 PQ2 160 0.5 17 HQFP 100 0.8 33 TSSOP 8 — 206 TQFP 32 18 79 TQFP-PQ4 64 5 35 EDQUAD 64 2.1 35 Rev.: B Amendment: /0 Issue Date: March, 1998 PACKAGING INFORMATION SYNERGY SEMICONDUCTOR 28 LEAD PLASTIC LEADED CHIP CARRIER (J28-1) © 1998 Synergy Semiconductor Corporation 10-17 Rev.: B Amendment: 0 Issue Date: March, 1998 QUAD 4-INPUT OR/NOR GATE FEATURES SY10E101 SY100E101 DESCRIPTION ■ ■ ■ ■ 500ps max. propagation delay Extended 100E VEE range of –4.2V to –5.5V True and complementary outputs Fully compatible with industry standard 10KH, 100K I/O levels ■ Internal 75KΩ input pulldown resistors ■ Fully compatible with Motorola MC10E/100E101 ■ Available in 28-pin PLCC package The SY10/100E101 are quad 4-input OR/NOR gates designed for use in new, high-performance ECL systems. The E101 features both true and complementary outputs. Q1 D1d 18 Q2 D2c D2b VEE D2a 27 17 28 16 15 Q2 VCC Q1 14 Q1 D1d 3 13 Q0 D1c 4 12 Q0 2 D2a D2b D2c PLCC TOP VIEW J28-1 1 Q2 5 6 7 8 9 10 11 Q2 VCCO D1c Q1 26 D0c D0b D0a D1a D2d D1a D0d D1b VCCO Q3 Q3 25 24 23 22 21 20 19 Q0 D0d D0c Q0 D1b D0b D3a D0a D3b D3c D3d PIN CONFIGURATION BLOCK DIAGRAM D2d D3a D3b D3c Q3 Q3 D3d PIN NAMES Pin Function Dna, Dnb, Dnc, Dnd Data Inputs Q0-Q3 True Outputs Q0-Q3 Inverting Outputs VCCO VCC to Output Rev.: D 1 Amendment: /2 Issue Date: May, 1998 SY10E101 SY100E101 Micrel LOGIC EQUATION Qn = Dna + Dnb + Dnc + Dnd DC ELECTRICAL CHARACTERISTICS VEE = VEE(Min.) to VEE(Max.); VCC = VCCO = GND TA = –40°C Symbol Parameter IIH Input HIGH Current IEE Power Supply Current 10EL 100EL TA = 0°C TA = +25°C TA = +85°C Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. — — 150 — — 150 — — 150 — — 150 Unit µA mA — — 30 30 36 36 — — 30 30 36 36 — — 30 30 36 36 — — 30 35 36 42 AC ELECTRICAL CHARACTERISTICS VEE = VEE(Min.) to VEE(Max.); VCC = VCCO = GND TA = –40°C Symbol Parameter TA = 0°C TA = +25°C TA = +85°C Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit tPLH tPHL Propagation Delay to Output D to Q 150 — 550 200 350 500 200 350 500 200 350 500 ps tskew Within-Device Skew(1) Within-Gate Skew(2) — — 50 25 — — — — 50 25 — — — — 50 25 — — — — 50 25 — — ps ps tr tf Rise/Fall Time 20% to 80% 275 — 625 300 380 575 300 380 575 300 380 575 ps NOTES: 1. Within-device skew is defined as identical transitions on similar paths through a device. 2. Within-gate skew is defined as the variation in propagation delays through a single gate when driven from its different inputs. PRODUCT ORDERING CODE Ordering Code Package Type Operating Range SY10E101JC J28-1 Commercial SY10E101JCTR J28-1 SY100E101JC SY100E101JCTR Ordering Code Package Type Operating Range SY10E101JI J28-1 Industrial Commercial SY10E101JITR J28-1 Industrial J28-1 Commercial SY100E101JI J28-1 Industrial J28-1 Commercial SY100E101JITR J28-1 Industrial 2 QUINT 2-INPUT XOR/XNOR GATE SY10E107 SY100E107 DESCRIPTION FEATURES ■ ■ ■ ■ ■ 600ps max. propagation delay Extended 100E VEE range of –4.2V to –5.5V True and complementary outputs OR/NOR function outputs Fully compatible with Industry standard 10KH, 100K I/O levels ■ Internal 75KΩ input pulldown resistors ■ Fully compatible with Motorola MC10E/100E107 ■ Available in 28-pin PLCC package The SY10/100E107 offer five 2-input XOR/XNOR gates and are designed for use in new, high- performance ECL systems. The E107 also features a function output, F, which is the OR of all five XOR gate outputs, while F is the NOR. Both true and complementary outputs are provided. BLOCK DIAGRAM PIN CONFIGURATION VCCO F F NC D4a D4b D3a F 25 24 23 22 21 20 19 F Q1 D2a Q2 D2b Q2 D3a Q3 D3b Q3 D4a Q4 D4b Q4 16 15 VCC Q3 2 14 Q3 D1b 3 13 Q2 D0a 4 12 Q2 28 PLCC TOP VIEW J28-1 1 5 6 7 8 9 10 11 VCCO D1b Q4 Q1 Q1 Q4 17 Q1 D1a 18 27 Q0 Q0 26 D2a D2b VEE D1a Q0 D0b D3b VCCO Q0 D0b D0a PIN NAMES Pin Function Dna, Dnb Data Inputs Q0-Q4 XOR Outputs Q0-Q4 XNOR Outputs F OR Output F NOR Output VCCO VCC to Output Rev.: C 1 Amendment: /1 Issue Date: February, 1998 SY10E107 SY100E107 Micrel LOGIC EQUATION F = (D0a ⊕ D0b) + (D1a ⊕ D1b) + (D2a ⊕ D2b) + (D3a ⊕ D3b) + (D4a ⊕ D4b) F = Q0 + Q1 + Q2 + Q3 + Q4 DC ELECTRICAL CHARACTERISTICS VEE = VEE (Min.) to VEE (Max); VCC = VCCO = GND TA = 0°C Symbol Parameter IIH Input HIGH Current IEE Power Supply Current TA = +25°C Min. Typ. Max. MIin. Typ. 10E 100E TA = +85°C Max. Min. Typ. Max. Unit Condition µA — mA — Unit Condition ps — ps 1 ps — — — 200 — — 200 — — 200 — — 42 42 50 50 — — 42 42 50 50 — — 42 48 50 58 AC ELECTRICAL CHARACTERISTICS VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND TA = 0°C Symbol Parameter TA = +25°C Min. Typ. Max. Min. Typ. TA = +85°C Max. Min. Typ. Max. tPLH tPHL Propagation Delay to Output D to Q D to F 250 500 410 725 600 1000 250 500 410 725 600 1000 250 500 410 725 600 1000 tskew Within-Device Skew, D to Q — 75 — — 75 — — 75 — tr tf Rise/Fall Time 20% to 80% 275 300 450 475 700 700 275 300 450 475 700 700 275 300 450 475 700 700 Q F NOTE: 1. Within-device skew is defined as identical transitions on similar paths through a device. PRODUCT ORDERING CODE Ordering Code Package Type Operating Range SY10E107JC J28-1 Commercial SY10E107JCTR J28-1 Commercial SY100E107JC J28-1 Commercial SY100E107JCTR J28-1 Commercial 2 8-BIT SHIFT REGISTER DESCRIPTION FEATURES ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ SY10E141 SY100E141 700MHz min. shift frequency Extended 100E VEE range of –4.2V to –5.5V 8 bits wide Bi-directional Four selectable modes for full functionality Asynchronous Master Reset Fully compatible with industry standard 10KH, 100K ECL levels Internal 75KΩ input pulldown resistors Fully compatible with Motorola MC10E/100E141 Pin-compatible with E241 Available in 28-pin PLCC package The SY10/100E141 are 8-bit, full-function shift registers designed for use in new, high-performance ECL systems. The E141 performs serial/parallel in and serial/parallel out, shifting in either direction. The eight inputs D0–D7 accept parallel input data, while DL/DR accept serial input data for left/right shifting. The two select pins, SEL0 and SEL1 permit four modes of operation: Load, Hold, Shift Left and Shift Right, as shown in the Truth Table. Input data is clocked into the register on the rising clock edge after meeting the minimum set-up time. A logic HIGH on the Master Reset (MR) pin asynchronously resets all the registers to zero. BLOCK DIAGRAM DL BITS 1-6 D DR D0 Q D R D Q R Q0 R Q7 Q D Q D7 SEL1 SEL0 CLK MR Rev.: C 1 Amendment: /1 Issue Date: February, 1998 SY10E141 SY100E141 Micrel PIN NAMES D5 VCCO Q7 SEL0 DL D7 D6 PIN CONFIGURATION Pin Function D0-D7 Parallel Data Inputs DL, DR Serial Data Inputs SEL1 26 18 Q6 SEL0, SEL1 Mode Select Inputs CLK MR VEE DR 27 17 CLK Clock 28 16 Q5 VCC NC Q0-Q7 Data Outputs VCCO Q4 Q3 MR Master Reset VCCO VCC to Output 25 24 23 22 21 20 19 PLCC TOP VIEW J28-1 1 2 D0 3 D1 4 15 14 13 12 7 8 9 10 11 DL DR SEL0 SEL1 MR CLK Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Load X X L L L Z D0 D1 D2 D3 D4 D5 D6 D7 Shift Right X X L H L L H H L L Z Z L H Q0 L Q1 Q0 Q2 Q1 Q3 Q2 Q4 Q3 Q5 Q4 Q6 Q5 Shift Left L H X X H H L L L L Z Z L Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 Q5 Q5 L L H Hold X X X X H H H H L L Z Z Q0 Q0 Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 Q5 Q5 L L H H Reset X X X X H X L L L L L L L L D2 D3 Q0 Q1 Q2 6 D4 VCCO 5 TRUTH TABLE Function DC ELECTRICAL CHARACTERISTICS VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND TA = 0°C Symbol Parameter TA = +25°C Min. Typ. Max. Min. Typ. IIH Input HIGH Current IEE Power Supply Current 10E 100E TA = +85°C Max. Min. Typ. Max. Unit Condition µA — mA — — — 150 — — 150 — — 150 — — 131 131 157 157 — — 131 131 157 157 — — 131 151 157 181 2 SY10E141 SY100E141 Micrel AC ELECTRICAL CHARACTERISTICS VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND TA = 0°C Symbol Parameter TA = +25°C Min. Typ. Max. Min. Typ. TA = +85°C Max. Min. Typ. Max. Unit Condition MHz — ps — ps — ps — fSHIFT Max. Shift Frequency 700 900 — 700 900 — 700 900 — tPLH tPHL Propagation Delay to Output CLK MR 625 600 750 725 975 975 625 600 750 725 975 975 625 600 750 725 975 975 tS Set-up Time D SEL0 SEL1 175 350 300 25 200 150 — — — 175 350 300 25 200 150 — — — 175 350 300 25 200 150 — — — Hold Time D SEL0 SEL1 200 100 100 –25 –200 –150 — — — 200 100 100 –25 –200 –150 — — — 200 100 100 –25 –200 –150 — — — tRR Reset Recovery Time 900 700 — 900 700 — 900 700 — ps — tPW Minimum Pulse Width CLK, MR 400 — — 400 — — 400 — — ps — tskew Within-Device Skew — 60 — — 60 — — 60 — ps 1 tr tf Rise/Fall Time 20% to 80% 300 525 800 300 525 800 300 525 800 ps — tH NOTE: 1. Within-device skew is defined as identical transitions on similar paths through a device. PRODUCT ORDERING CODE Ordering Code Package Type Operating Range SY10E141JC J28-1 Commercial SY10E141JCTR J28-1 Commercial SY100E141JC J28-1 Commercial SY100E141JCTR J28-1 Commercial 3 9-BIT MAGNITUDE COMPARATOR FEATURES SY10E166 SY100E166 DESCRIPTION ■ 1100ps max. Propagation Delay A = B ■ Extended 100E VEE range of –4.2V to –5.5V The SY10/100E166 are 9-bit magnitude comparators designed for use in new, high-performance ECL systems. The E166 compares the binary value of two 9-bit words and indicates whether one word is greater than or equal to the other. ■ Fully compatible with industry standard 10KH, 100K ECL levels ■ Internal 75KΩ input pulldown resistors ■ Fully compatible with Motorola MC10E/100E166 ■ Available in 28-pin PLCC package BLOCK DIAGRAM A0–A8 VCCO A1 B0 A0 A2 B1 B2 PIN CONFIGURATION A>B 9 25 24 23 22 21 20 19 B>A B3 NC VEE 27 17 A4 B4 A5 28 2 7 8 NC 14 4 6 12 15 3 5 13 16 TOP VIEW PLCC J28-1 1 A=B NC VCC B>A VCCO A>B 9 10 11 B8 9 18 A8 B0–B8 A=B 26 B5 A6 B6 A7 B7 COMPARATOR A3 PIN NAMES Pin Function A0–A8 A Data Inputs B0–B8 B Data Inputs A>B A Greater than B Output B>A B Greater than A Output A=B A Equal to B Output (active-LOW) VCCO VCC to Output Rev.: C 1 Amendment: /1 Issue Date: February, 1998 SY10E166 SY100E166 Micrel DC ELECTRICAL CHARACTERISTICS VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND TA = 0°C Symbol Parameter TA = +25°C Min. Typ. Max. Min. Typ. IIH Input HIGH Current IEE Power Supply Current — 10E 100E — — — 150 113 113 136 136 — — — — 113 113 TA = +85°C Max. Min. Typ. Max. 150 150 136 136 — — — — 113 130 Unit Condition µA — mA — Unit Condition ps — ps — 136 156 AC ELECTRICAL CHARACTERISTICS VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND TA = 0°C Symbol Parameter tPLH tPHL Propagation Delay to Output D to A = B D to A < B, A > B tr tf Rise/Fall Time 20% to 80% TA = +25°C Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. 500 500 750 850 1100 1400 500 500 750 850 1100 1400 500 500 750 850 1100 1400 300 450 800 300 450 800 300 450 800 PRODUCT ORDERING CODE Ordering Code TA = +85°C Package Type Operating Range SY10E166JC J28-1 Commercial SY10E166JCTR J28-1 Commercial SY100E166JC J28-1 Commercial SY100E166JCTR J28-1 Commercial 2