CS98100

DVD Processor for Low Cost DVD Players

Features

Description

32-Bit RISC Processor, supported by RTOS, C/C++

compilers

32-bit DSP capable of AC-3, MPEG, DTS, MP3, and WMA

Progressive Scan (480p) with 3:2 pull down support or

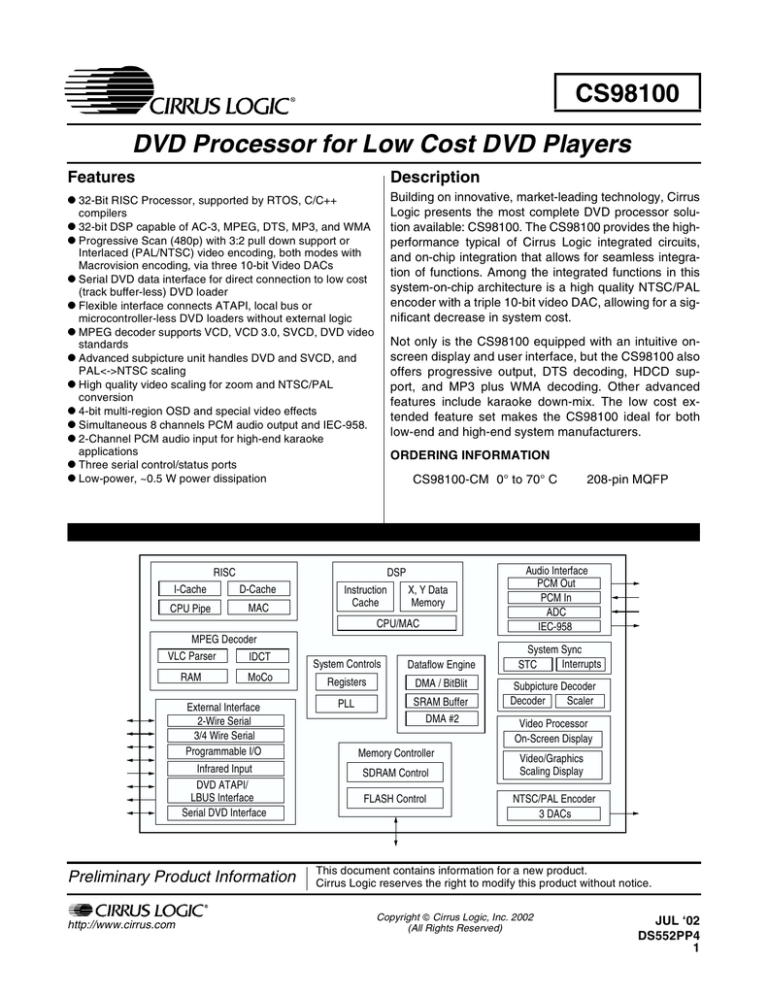

Building on innovative, market-leading technology, Cirrus

Logic presents the most complete DVD processor solution available: CS98100. The CS98100 provides the highperformance typical of Cirrus Logic integrated circuits,

and on-chip integration that allows for seamless integration of functions. Among the integrated functions in this

system-on-chip architecture is a high quality NTSC/PAL

encoder with a triple 10-bit video DAC, allowing for a significant decrease in system cost.

Interlaced (PAL/NTSC) video encoding, both modes with

Macrovision encoding, via three 10-bit Video DACs

Serial DVD data interface for direct connection to low cost

(track buffer-less) DVD loader

Flexible interface connects ATAPI, local bus or

microcontroller-less DVD loaders without external logic

MPEG decoder supports VCD, VCD 3.0, SVCD, DVD video

standards

Advanced subpicture unit handles DVD and SVCD, and

PAL<->NTSC scaling

High quality video scaling for zoom and NTSC/PAL

conversion

4-bit multi-region OSD and special video effects

Simultaneous 8 channels PCM audio output and IEC-958.

2-Channel PCM audio input for high-end karaoke

applications

Three serial control/status ports

Low-power, ~0.5 W power dissipation

Not only is the CS98100 equipped with an intuitive onscreen display and user interface, but the CS98100 also

offers progressive output, DTS decoding, HDCD support, and MP3 plus WMA decoding. Other advanced

features include karaoke down-mix. The low cost extended feature set makes the CS98100 ideal for both

low-end and high-end system manufacturers.

ORDERING INFORMATION

CS98100-CM 0° to 70° C

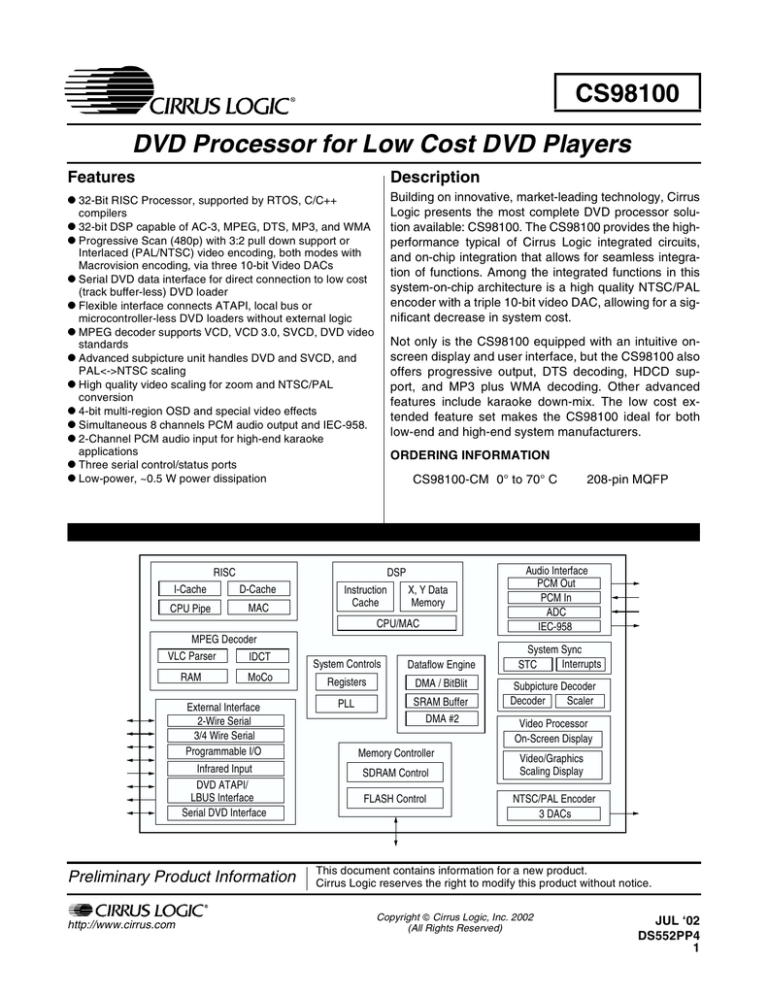

RISC

DSP

I-Cache

D-Cache

CPU Pipe

MAC

Instruction

Cache

X, Y Data

Memory

CPU/MAC

MPEG Decoder

VLC Parser

IDCT

RAM

MoCo

External Interface

2-Wire Serial

3/4 Wire Serial

Programmable I/O

Infrared Input

DVD ATAPI/

LBUS Interface

Serial DVD Interface

Preliminary Product Information

http://www.cirrus.com

System Controls

Dataflow Engine

Registers

DMA / BitBlit

PLL

SRAM Buffer

DMA #2

Memory Controller

SDRAM Control

FLASH Control

208-pin MQFP

Audio Interface

PCM Out

PCM In

ADC

IEC-958

System Sync

Interrupts

STC

Subpicture Decoder

Decoder

Scaler

Video Processor

On-Screen Display

Video/Graphics

Scaling Display

NTSC/PAL Encoder

3 DACs

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright Cirrus Logic, Inc. 2002

(All Rights Reserved)

JUL ‘02

DS552PP4

1

CS98100

TABLE OF CONTENTS

1. CHARACTERISTICS AND SPECIFICATIONS ........................................................................ 5

1.1 AC and DC Parametric Specifications ............................................................................... 5

1.1.1 Absolute Maximum Rating .................................................................................... 5

1.1.2 Recommended Operating Conditions ................................................................... 5

1.1.3 Electrical Characteristics ....................................................................................... 5

1.2 AC Characteristics ............................................................................................................. 7

1.2.1 ATAPI Interface ..................................................................................................... 7

1.2.2 SDRAM Interface .................................................................................................. 8

1.2.3 DVD Serial Interface Timing ................................................................................ 11

1.2.4 Digital Video Interface Timing ............................................................................. 12

1.2.5 Digital Audio Interface Timing ............................................................................. 13

1.2.6 ROM/NVRAM Interface ....................................................................................... 15

1.2.7 Miscellaneous Timings ........................................................................................ 17

2. TYPICAL APPLICATION ........................................................................................................ 18

2.1 CS98100 Device Summary ............................................................................................. 18

3. FUNCTIONAL DESCRIPTION ............................................................................................... 20

3.1 RISC Processor ............................................................................................................... 20

3.2 DSP Processor ................................................................................................................ 20

3.3 Memory Control ............................................................................................................... 20

3.4 Dataflow Control (DMA) ................................................................................................... 20

3.5 System Control Functions ................................................................................................ 20

3.6 DVD/ATAPI Interface ....................................................................................................... 21

3.7 Serial DVD Interface ........................................................................................................ 21

3.8 MPEG Video Decoding .................................................................................................... 21

3.9 Audio Processing ............................................................................................................. 21

3.10 Video Processing ........................................................................................................... 22

3.11 Video Encoder ............................................................................................................... 22

4. MEMORY MAP AND REGISTERS ......................................................................................... 23

4.1 Processor Memory Map ................................................................................................... 23

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find one nearest you go to www.cirrus.com/en/contacts/sales.

IMPORTANT NOTICE

“Preliminary” product information describes products that are in production, but for which full characterization data is not yet available. “Advance” product information

describes products that are in development and subject to development changes. Cirrus Logic, Inc. and its subsidiaries (“Cirrus”) believe that the information contained

in this document is accurate and reliable. However, the information is subject to change without notice and is provided “AS IS” without warranty of any kind (express

or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and

complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent

infringement, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information,

Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus

owns the copyrights of the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect

to Cirrus integrated circuits or other parts of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional

purposes, or for creating any work for resale.

An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material

and controlled under the “Foreign Exchange and Foreign Trade Law” is to be exported or taken out of Japan. An export license and/or quota needs to be obtained

from the competent authorities of the Chinese Government if any of the products or technologies described in this material is subject to the PRC Foreign Trade Law

and is to be exported or taken out of the PRC.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE

SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks

or service marks of their respective owners.

Purchase of I2C components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Phillips I2C Patent Rights to use those

components in a standard I2C system.

2

CS98100

4.2 Host Port Memory Map .................................................................................................... 23

4.3 Internal IO Space Map ..................................................................................................... 24

4.4 CS98100 Register Space ................................................................................................ 24

5. PIN DESCRIPTIONS .............................................................................................................. 37

6. PIN ASSIGNMENTS ............................................................................................................... 38

6.1 Miscellaneous Pins .......................................................................................................... 46

6.2 Serial Interface ................................................................................................................ 47

6.3 SDRAM Interface ............................................................................................................. 48

6.4 ROM/NVRAM Interface ................................................................................................... 49

6.5 Digital Video Output Interface .......................................................................................... 50

6.6 Audio Output/Input Interface ............................................................................................ 51

6.7 Host Master/ATAPI Interface ........................................................................................... 52

6.8 DVD I/O Channel Interface .............................................................................................. 53

6.9 DVD Serial Data Interface ............................................................................................... 54

6.10 Video Encoder Interface ................................................................................................ 55

6.11 General Purpose Input/Output (GPIO) .......................................................................... 56

6.12 Power and Ground ........................................................................................................ 57

7. 208 PIN MQFP PACKAGE SPECIFICATIONS ...................................................................... 58

LIST OF FIGURES

Figure 1. ATAPI Interface Timing Diagram ..................................................................................... 7

Figure 2. SDRAM Refresh Transaction........................................................................................... 8

Figure 3. SDRAM Burst Read Transaction ..................................................................................... 9

Figure 4. SDRAM Burst Write Transaction ..................................................................................... 9

Figure 5. CS98100 SDRAM Read and Write ................................................................................ 10

Figure 6. CS98100 DVD Serial Interface Timing Diagram............................................................ 11

Figure 7. CS98100 Digital Video Interface Timing Diagram ......................................................... 12

Figure 8. Digital Audio In Timing Diagram .................................................................................... 13

Figure 9. Digital Audio Out Timing Diagram.................................................................................. 14

Figure 10. ROM/NVRAM Reading Timing .................................................................................... 15

Figure 11. ROM/NVRAM Write Timing ......................................................................................... 16

Figure 12. Miscellaneous Timings................................................................................................. 17

Figure 13. CS98100 Application ................................................................................................... 18

Figure 14. CS98100 Pin Layout .................................................................................................... 37

Figure 15. CS98100 208-Pin MQFP Package Drawing ................................................................ 58

LIST OF TABLES

Table 1. ATAPI Interface Characteristics ........................................................................................ 7

Table 2. SDRAM Interface Characteristics ..................................................................................... 8

Table 3. CS98100 DVD Interface Characteristics......................................................................... 11

Table 4. CS98100 Digital Video Interface Characteristics ............................................................ 12

Table 5. Digital Audio In Characteristics ....................................................................................... 13

Table 6. Digital Audio Out Characteristics .................................................................................... 14

Table 7. RAM/NVROM Characteristics ......................................................................................... 15

Table 8. Miscellaneous Timing Characteristics............................................................................. 17

Table 9. Memory Map - RISC Processor ...................................................................................... 23

Table 10. Host Port Memory Map ................................................................................................. 23

Table 11. Internal IO Space Map .................................................................................................. 24

Table 12. CS98100 Register Map and Blocks .............................................................................. 24

Table 13. CS98100 Registers ....................................................................................................... 25

3

CS98100

Table 14. Pin Type and Direction Legend ..................................................................................... 37

Table 15. Pin Assignments............................................................................................................ 38

Table 16. Miscellaneous Interface Pins......................................................................................... 46

Table 17. Serial Interface Pin Assignments .................................................................................. 47

Table 18. SDRAM Interface Pin Assignments............................................................................... 48

Table 19. ROM/NVRAM Interface Pin Assignments ..................................................................... 49

Table 20. Video Output Interface Pin Assignments....................................................................... 50

Table 21. Audio Output Interface Pin Assignments....................................................................... 51

Table 22. Host Master Interface Pin Assignments ........................................................................ 52

Table 23. DVD I/O Channel Interface Pin Assignments ................................................................ 53

Table 24. DVD Serial Data Interface Pin Assignments ................................................................. 54

Table 25. Video Encoder Interface Pin Assignments .................................................................... 55

Table 26. General Purpose I/O Interface Pin Assignments........................................................... 56

Table 27. Power and Ground ........................................................................................................ 57

4

CS98100

1. CHARACTERISTICS AND SPECIFICATIONS

1.1

AC AND DC PARAMETRIC SPECIFICATIONS

(AGND, DGND=0V, all voltages with respect to 0V)

1.1.1

ABSOLUTE MAXIMUM RATING

Symbol

Description

Min

Max

Unit

VDDIO

Power Supply Voltage on I/O ring

-0.5

4.6

Volts

VDDCORE

Power Supply Voltage on core logic and PLL

-0.5

2.5

Volts

VI

Digital Input Applied Voltage (power applied)

-0.5

5.5

Volts

II

Digital Input Forced Current

-10

10

mA

IO

Digital Output Forced Current

-50

50

mA

TSOL

Lead Soldering Temperature

260

o

TVSOL

Vapor Phase Soldering Temperature

235

oC

TSTOR

Storage Temperature (no power applied)

-40

125

o

TAMB

Ambient Temperature (power applied)

0

70

oC

Ptotal

Total Power consumption

2

W

C

C

CAUTION: Operating beyond these Minimum and Maximum limits can result in permanent damage to

the device. Cirrus Logic recommends that CS98000 devices operate at the settings described in the next

table.

1.1.2

RECOMMENDED OPERATING CONDITIONS

Symbol

Min

Typ

Max

Units

Supply Voltage, IO

Parameter

VDD

3.0

3.3

3.6

Volts

Supply Voltage, core and PLL

VDD

1.62

1.8

1.98

Volts

Ambient Temperature (power applied)

TAMB

0

25

70

oC

Min

Typ

Max

Units

1.1.3

ELECTRICAL CHARACTERISTICS

Parameter

Symbol

Conditions

Power Supply

Supply Voltage, IO

VDD

3.0

3.3

3.6

Volts

Supply Voltage, core and PLL

VDD

1.62

1.8

1.98

Volts

Supply Current, IO

IDD

Normal Operating

45

mA

Supply Current, core and PLL

IDD

Normal Operating

210

mA

Digital Pins

Input Voltage, High

VIH

Input Voltage, Low

VIL

2.2

Volts

0.8

Volts

5

CS98100

Parameter

Symbol

Conditions

Min

Input Current

IIN

VIN = VDD or VSS

-1

Input Pull up/down resistor

RI

Output Voltage, High

VOH

@ buffer rating

Output Voltage, Low

VOL

@ buffer rating

High-Z-state Leakage

IOZ

VOUT = VSS or VDD

Analog Video Pins

Full Scale Current

IFS

RL = 37.5 Ω

34

mA

Output Voltage Range

VIO

RL = 37.5 Ω

1.28

Volts

2

%

DAC to DAC matching1

Output Voltage Range

Differential Gain

Differential Phase

Signal to Noise

Chrominance AM Noise

Chrominance PM Noise

1.Only applies each set of three.

6

Max

Units

+1

µA

75

MAT

Vout

DG

DP

SNR

AM

PM

Typ

KΩ

2.4

Volts

-1

RL= 37.5Ω

0.4

Volts

+1

µA

1.28

1

0.5

74

80

75

Volts

%

deg

dB

dB

dB

CS98100

1.2

AC CHARACTERISTICS

(TA= 25°C; VDD_PLL=VDD_CORE=1.8 V±10%, VDD_IO=3.3 V±10%)

1.2.1

ATAPI Interface

The CS98100 can interface with ATAPI-type slave loader gluelessly. Figure 1 illustrates a read ATAPI

transaction and a write ATAPI transaction. PIO mode 4 is implemented for sufficient data transfer rate between ATAPI device and the CS98100.

See Table 1 for the ATAPI symbols and characterization data.

Symbol

Description

Min

Typ

Max

Unit

tacyc1

Cycle Time

87

ns

t

aavr

Address Valid to HMRD-/HMWR- Setup

7

ns

t

ah

Address Hold from HMRD-/HMWR Setup 8

ns

tarww

H_RD/H_WR Pulse Width

58

ns

t

arec

H_RD/H_WR Recovery Time

19

ns

tawsu

H_WR Data Setup

20

ns

t

awh

H_WR Data Hold

4

ns

t

ardsu

H_RD Data Setup

20

ns

tarddh

H_RD Data hold

0

ns

t

ardts

H_RD Data three-state

7

ns

tarsu

H_RDY Setup Time

14

ns

t

H_RDY Hold Time

arh1

0

ns

Table 1. ATAPI Interface Characteristics

1.Values are guaranteed by design only

t acyc

H_A[2:0] ,

H_CS[3:0]

t aavr

t arww

t

H_RD/H_WR

ah

t arec

H_D[15:0](WRITE)

tawsu

tawh

H_D[15:0](READ)

tarsu

t arddh

tardsu

tardts

H_RDY(deasserted

before tarsu)

t arh

H_RDY(asserted

before tarsu)

Figure 1. ATAPI Interface Timing Diagram

7

CS98100

1.2.2

SDRAM Interface

The CS98100 interfaces with either SDRAM or SGRAM, for high data bandwidth transfer. Figure 5 and

Table 2 show the interface pin timing. Figure 2 shows the refresh cycle performed by the CS98100.

Figure 3 shows a burst read (length = 8) transaction, while Figure 4 shows a burst write (length=8) transaction. In both Figure 3 and Figure 4, CAS latency is programmed to 3.

Symbol

Description

tmco

Output Delay from DR_CKO active edge

t

DR_CKO Period

mper

Min

Typ

Max

9

11

12.2

ns

tmdow

DR_D[31:0] delay from DR_CKO

t

mhw

DR_D[31:0] valid time after DR_CKO

1.5

ns

t

msur1

DR_D[31:0] setup to DR_CKO

3.9

ns

tmsurd1

DR_D[31:0] setup to DR_CKO with delay 4.3

ns

t

DR_D[31:0] hold time after DR_CKO

ns

mhr1

tmhrd1

9.1

1.85

DR_D[31:0] hold time after DR_CKO with 1.3

delay

Table 2. SDRAM Interface Characteristics

1.Delay is programmable by selecting the DRAM_Input_Speed bit of the Command Register(0x000)

DR_CKO

DR_A[11:0]

DR_BS_N

DR_RAS_N

DR_CAS_N

DR_WE_N

DR_D[31:0]

DR_DQM_[3:0]

DR_AP

Figure 2. SDRAM Refresh Transaction

8

Unit

ns

ns

ns

CS98100

DR_CKO

DR_A_[11:0]

R0

C0

C1

C2

C3

C4

C5

C6

C7

D3

D4

DR_CKE

DR_RAS_N

DR_CAS_N

DR_WE_N

D0

DR_D[31:0]

DR_DQM[3:0]

F

D1

D2

D5

D6

D7

F

0

Figure 3. SDRAM Burst Read Transaction

DR_CKO

DR_A_[11:0]

R0

C0

C1

C2

C3

C4

C5

C6

D4

D5

D6

C7

DR_CKE

DR_RAS_N

DR_CAS_N

DR_WE_N

D0

DR_D[31:0]

DR_DQM[3:0]

F

D1

D2

D3

0

D7

F

Figure 4. SDRAM Burst Write Transaction

9

CS98100

tmco

tmper

DR_CKO

DR_RAS_N,DR_CAS_N

DR_W E_N,DR_AP,DR_DQM[3:0],

DR_CKE,DR_A[11:0]

tmdow

DR_D[31:0](WRITE)

DR_D[31:0](READ)

tmsur

tmhr

Figure 5. CS98100 SDRAM Read and Write

10

tmhw

CS98100

1.2.3

DVD Serial Interface Timing

Figure 6 and Table 3 illustrate the signal timing for the DVD serial interface input pins.

Symbol

Description

Min

Typ

Max

Unit

t

dsckper1

DVDS_CLK Period

33

tdsckl1

DVDS_CLK Low Time

40

50

%

t

dsckh1

DVDS_CLK High Time

40

50

%

t

dsdsu

DVDS_DATA Setup to DVDS_CLK active edge

4

ns

t

dsdhd

DVDS_DATA Hold after DVDS_CLK active edge 0

ns

t

dscdsu

DVDS_VLD,DVDS_SOS Setup to DVDS_CLK

3

ns

tdscdhd

DVDS_VLD,DVDS_SOS Hold after DVDS_CLK 0

ns

ns

Table 3. CS98100 DVD Interface Characteristics

1.Values are guaranteed by design only

t dsckper

DVDS_CLK

(Input)

tdsckl

t dsckh

t dsdsu

t dsdhd

DVDS_DATA

(Input)

t dscdsu

t dscdhd

DVDS_VLD, DVDS_SOS

(Input)

Figure 6. CS98100 DVD Serial Interface Timing Diagram

11

CS98100

1.2.4

Digital Video Interface Timing

Figure 7 illustrates the signal timing for the digital video interface pins. The clock is without a polarity to

show the clock may be inverted by register programming. This also illustrates that data is clocked out on

both clock edges in progressive mode. The data order is Cr,Y0,Cb,Y1, and the sync outputs may be programmed as active high or active low.

Symbol

Description

Min

Typ

t

VDAT[7:0] delay from CLK27_O

-10

10

ns

Vsync/Hsync delay from CLK27_O

-10

10

ns

covo12

37.037

Unit

CLK27_O period

tcovo22

Table 4. CS98100 Digital Video Interface Characteristics

1.Values are guaranteed by design only

2.It is recommanded that the output data should be taken at the opposite edge of the CLK27_O.

Tvocper

CLK27_O

(Output)

Tcovo1

VDAT[7:0]

(Output)

Tcovo2

VSYNC/HSYNC (Output)

Figure 7. CS98100 Digital Video Interface Timing Diagram

12

Max

tvocper1

ns

CS98100

1.2.5

Digital Audio Interface Timing

Figure 8 and Figure 9 illustrate the signal timing for the digital audio pins. The bi-directional AUD_XCK

pin clocks at 8x the frequency of the AUD_BCK pin. The AUD_BCK pin outputs at 32x or 48x of the

sample frequency, and transitions on the falling edge of the AUD_XCK pin. AUD_BCK is shown without

polarity to indicate the polarity is programmable.

Symbol

Description

Min

Typ

Max

Unit

tslri

AIN_LRCK setup to AUD_BCK active edge

25

-

ns

t

sdi

AIN_DATA setup to AUD_BCK active edge

25

-

ns

thsdi

AIN_DATA hold time after AUD_BCK active edge 1

-

ns

Table 5. Digital Audio In Characteristics

*AUD_BCK (Output)

t lrts

AIN_LRCK (Input)

t sdsus t sdhs

AIN_DATA (Input)

* Active clock edge is programmable. Timing is referenced from active edge.

Figure 8. Digital Audio In Timing Diagram

13

CS98100

Symbol

Description

Min

Typ

Max

AUD_XCLK High Time (AUD_XCLK is Input/Output) 40

50

%

taxcl1

AUD_XCLK Low Time (AUD_XCLK is Input/Output) 40

50

%

t

axper

AUD_XCLK period (Input/Output)

todbck

AUD_BCK delay from AUD_XCLK(output) active

edge

10

ns

t

AUD_BCK delay from AUD_XCLK(input) active

edge

21

ns

odbck

27

ns

taoper

AUD_BCK period

216

ns

t

odlr2

AUD_LRCK delay from AUD_BCK active edge

-10

10

ns

todsd2

AUD_D[3:0] delay from AUD_BCK active edge

-10

10

ns

Table 6. Digital Audio Out Characteristics

1.Values are guaranteed by design only

2.It is recommanded that the output data should be taken at the opposite edge of the AUD_BCK.

t

axper

AUD_XCLK(Input/Output)

t

t

axcl

axch

AUD_BCK(Output)

t

odbck

t aoper

* AUD_BCK(Output)

t odlr

AUD_LRCK(Output)

t odsd

AUD_DO[3:0] (Output)

* Active clock edge is programmable. Timing is referenced from active edge.

Figure 9. Digital Audio Out Timing Diagram

14

Unit

taxch1

CS98100

1.2.6

ROM/NVRAM Interface

Symbol

Description

Min

Typ

Max

trc

Read Cycle Time

t

cds

CE to Data Setup

80

ns

t

ods

OE to Data Setup

70

ns

tads

Address to Data Setup

90

ns

t

aws

Address to WE setup (Write)

20

ns

tcws

CE to WE setup (Write)

5

ns

t

wp

WE Pulse Width (Write)

160

ns

t

wdo

CE to Data Output (Write)

tdh

98

Unit

ns

-5

WE to Data Hold (Write)

10

ns

ns

Table 7. RAM/NVROM Characteristics

Note:Read timing based on 10.5 ns memory clock and 4 programmed wait states.

t rc

A d d re ss

M _ A [11 :0 ],

M _ D [27 :1 6]

t cds

N V M _ C E _N

t ods

NVM_OE_N

(M _A P )

tads

M _D [7 :0 ]

NVM_W E_N

Figure 10. ROM/NVRAM Reading Timing

15

CS98100

t aw s

A dd re ss

M _A [1 1:0 ],

M _D [2 7:1 6]

N V M _C E _ N

tc w s

tw p

N V M _W E _ N

t w do

M _D [7 :0]

N V M _O E _ N

(M _ A P )

Figure 11. ROM/NVRAM Write Timing

16

t w dh

CS98100

1.2.7

Miscellaneous Timings

Symbol

txclper

1

Description

Min

XTLCLK period

Typ

37.037

Max

Unit

ns

trstl

RST_N Low Pulse Width

1000

ns

tgph

GPIO PW High

50

ns

tgpl

GPIO PW Low

50

ns

Table 8. Miscellaneous Timing Characteristics

1.XTLCLK must meet the requirement of external the video encoder for correct chroma (27 MHz ± 1 KHz).

t xccper

XT L CL O C K

t rstl

RESET-N

GPIO

tgph

t gpl

Figure 12. Miscellaneous Timings

17

CS98100

2. TYPICAL APPLICATION

Figure 13 shows an example of a complete high-end DVD solution using the CS98100.

Front Panel

27M XTAL

(4)Audio

DACs

Audio

ADC

Audio

CS98100

AudioUp to 8 Channels

S/PDIF

IR

Composite Video

S-Video

DVD Loader

(IO Channel,

ATPAI or

Serial)

ROM/

FLASH

1/

-1MB

SDRAM

4-8MB

Component Video

2

Power

Reg.

Switch

Power

Figure 13. CS98100 Application

2.1

CS98100 Device Summary

RISC-32

•

•

•

•

•

•

•

•

•

•

•

Powerful 32-bit RISC processor

Optimizing C compiler and source level debugger

Big or little endian data formats supported

MAC multiply/accumulate in two cycles with

C support.

4 Kbyte instruction cache, 2 Kbyte data cache.

Single cycle instructions run at 90 MHz.

•

DSP-32

•

•

Powerful 24/32-bit DSP processor

24-bit fixed point logic, with 54-bit accumulator.

Single-cycle throughput, 2-cycle latency multiply accumulate, 32-bit simple integer logic.

8 Kbyte instruction cache, 12 Kbyte program

visible local memory

Single cycle instructions run at 90 MHz.

•

•

•

•

•

DATA FLOW ENGINE

•

SYSTEM CONTROLS

•

•

18

Include several hardware lockable semaphore

registers

General-purpose registers for inter-processor

communication

32-bit timers for I/O and other uses, with programmable interval rates

Both hardware and software interrupts on data

or debug

Performance monitors which measures DRAM

bandwidth, usage, and RSK performance

Built in PLLs generate all required clocks from

27 MHz input clock.

Memory Controller

Supports SDRAM, and SGRAM, from 2

MBytes to 32 MBytes.

Supports multiple banks of FLASH and ROM

up to 32 MBytes.

32-bit data bus for DRAM, 8 or 16-bit data bus

for ROM.

•

•

Two DMA controllers – local memory based

and direct memory-to-memory

2432 bytes of internal memory, DMA to/from

main RAM into local SRAM.

Supports endian conversion and byte, short,

CS98100

•

•

•

•

•

long data formats on DMA.

Supports block transfers for graphics bit blits.

•

MPEG VIDEO DECODER

•

Supports VCD1.0, 1.1, 2.0 and 3.0, SVCD, and

DVD video standards.

Supports trick features, including smooth 2x

forward play.

Special anti-tearing logic controls picture decode and presentation.

Advanced error concealment hardware.

VIDEO PROCESSOR

•

•

SYSTEM SYNCHRONIZATION

•

•

•

•

•

•

System time clock (STC) for audio/video synchronization

Flexible interrupt structure for controlling decode and presentation times

Hardware scheduling of sub-picture and highlight events

•

AUDIO INTERFACE

•

Supports 8 channels PCM, I2S at up to 24 bits

and 96 kHz output rate.

Simultaneous IEC-958 output with programmable channel status and user data

Also supports S/PDIF receiver for high performance applications

•

•

•

•

•

•

•

•

2-wire serial master and slave port, second 2wire master port for controlling DVD device.

3- or 4-wire serial master/slave port.

Large number of programmable bi-directional

I/O pins.

All pins not used for other function can be reassigned as general purpose I/O pins

8 pins can be used as edge or level detection interrupt pins.

Hardware-assisted support for infrared remote

devices, such as remote control, infrared keyboard, mouse, printer, and more.

Programmable parallel host master interface

supports formats including ATAPI, ISA, and

more.

On screen display module supports 2-bit or 4bit, pixel modes. It supports 3 separate regions

and 16 transparency overlay levels

High quality scaling using 16 tap polyphase

programmable vertical and horizontal filters, to

support any size image up to 768x576.

Multiple video plain overlays (main video /

subpicture / picture-in-picture / on-screen display).

Gamma Correction.

Progressive scan video output

VIDEO ENCODER

•

•

•

•

EXTERNAL INTERFACE

•

IO channel interface supports standard DVD

loader protocols

Separate serial DVD interface to support lowcost (track buffer-less) loaders

•

•

Three 10-bit video DACs, drive 37.5Ω load directly without external buffering

Supports PAL (B,D,G,H,I,N) and NTSC

Component (RBG or YUV) or composite + SVideo output

Progressive or interlaced mode output

Macrovision 7.1 support (interlaced) and Macrovision 1.03 support (progressive)

Wide-screen signaling support (interlaced and

progressive) and CGMS support

Closed captioning support

SUB-PICTURE PROCESSOR

•

•

•

•

•

•

•

•

Run-length decode DVD sub-pictures and

SVCD OGT formats

Hardware vertical scaling supports NTSC-PAL

format conversion

16 level alpha blending

System Functions

208-pin MQFP package.

All I/O pins are 3V with 5V tolerance.

Advanced 0.18 micron CMOS technology.

Chip runs at 90 MHz

Supports Low power modes and clock shutoff.

19

CS98100

3. FUNCTIONAL DESCRIPTION

3.1

RISC Processor

The CS98100 includes a powerful, proprietary 32bit RISC processor with optimizing C compiler

support. The RISC has a MIPS-compatible instruction set, as well as a MAC engine which performs

multiply/accumulate in 2 cycles in a pipelined fashion with C support, effectively achieving single cycle throughout. The CS98100 fully supports many

Real Time Operating Systems (RTOS). The RISC

processor co-ordinates on-chip multi-threaded

tasks, as well as supervises system activities such

as remote control and VFD front panel control.

3.2

DSP Processor

The CS98100 contains a proprietary digital signal

processor (DSP) which is optimized for audio applications. The DSP performs 32-bit simple integer

operations, and has a 24-bit fixed point logic unit,

with a 54-bit accumulator. There are 32 generalpurpose registers, and eight independent address

generation registers, featuring: post-increment

ALU, linear and circular buffer operations, bit reverse ALU operations, and dual operand read from

memory. The multiply-accumulator has single-cycle throughput, with two cycle latency. The DSP is

optimized for bit packing and unpacking operations. The interface to main memory is designed for

bursting flexible block sizes and skip counts.

3.3

Memory Control

The DRAM Interface performs the SDRAM control and arbitration functions for all the other modules in the CS98100. The DRAM interface services

and arbitrates a number of clients and stores their

code and/or data within the local memory. This arbitration and scheduling guarantees the allocation

of sufficient bandwidth to the various clients. The

DRAM Interface supports up to 32 MByte. For a

typical DVD player application, CS98100 requires

8 MByte of SDRAM and 1 MByte of FLASH.

20

Sharing the same interface, the CS98100 also supports flash ROM, OTP, or masked ROM interface.

Code is stored in ROM. After the system is booted,

the code is shadowed inside DRAM for execution.

FLASH ROM interface is provided so that the code

can be upgraded in field once the communication

channel is established via, for example, CD-R or

serial port. Utility software will be provided to debug and upgrade code for the system manufacturer.

3.4

Dataflow Control (DMA)

The DMA controller moves data between the external memory and an internal memory. The external

memory address can be specified using a register,

or in FIFO mode, using start and end address registers. Separate start/end address registers are used

for DMA read and write operations. The DMA interface also has a block transfer function, which allows for the transfer of one block of data from one

external memory location to another external memory location. In effect, combining a DMA read and

write into one operation. In addition, the DMA

write operation allows for byte, short, word, and

other types of masking. A second dedicated DMA

controller provides for fast memory-to-memory

transfers.

3.5

System Control Functions

The system control functions are used to coordinate

the activities of the multiple processors, and to provide the supporting system operations. Four 32-bit

communication registers are available inter-processor communication, and eight semaphore registers are used for resource locking. Timers are

available for general-purpose functions, as well as

more specialized functions such as watchdog timers and performance monitoring. The large number

of general purpose I/Os offers flexibility in system

configurations.

Three separate serial interfaces, conforming to industry-standard protocols, are available for a vari-

CS98100

ety of system interface functions. Interrupts can be

generated on specific or generic events. Infrared inputs can be filtered of glitches or stored unfiltered

into memory. Power-down control of the internal

clocks is also possible. Internal PLLs are used to

generate the internal system and memory clocks,

and audio clocks of any widely used frequency.

3.6

DVD/ATAPI Interface

The CS98100 has a programmable interface port,

which can be configured to connect to industry

standard CD/DVD loaders without external glue

logic. The CD/DVD interface fully supports a wide

range of popular CD/DVD loaders. The interface

consists of DVD control and data ports, and an optional CD control/data port. The CS98100 hardware manages the DVD interface and moving data

to an arbitrary size input FIFO in DRAM.

The same interface pins can be optionally configured as a generic 16-bit host master port. In this

mode, the CS98100 can control up to four devices

(using 4 chip select outputs), each of which may

use different protocol and timing. The interface can

be set up in ATAPI mode, to connect directly to any

ATAPI DVD loader (using two chip selects). Simultaneously, the other two chip selects can be

configured to connect to other devices, such as a

super I/O chip or hard disk.

A third option is to configure the interface for micro-less DVD loader operation, which may also be

configured to connect without external glue logic.

3.7

Serial DVD Interface

The CS98100 has a 4-pin serial port which interfaces to the data port of popular low-cost DVD loaders. This type of loader provides for low system

cost by eliminating the track buffer, interface

FIFO, and flow control logic. The CS98100 contains a large internal SRAM to handle high burst

data rates, without requiring reverse flow control.

The track buffer resides in the CS98100 SDRAM,

which reduces system complexity and simplifies

the software architecture. The CS98100 performs

error detection, sector number tracking, and interrupt generation.

3.8

MPEG Video Decoding

Compressed MPEG data is read from the DVD disk

into an input FIFO in DRAM. The data flow

(DMA) controller moves Video packets from the

input FIFO into the MPEG decoder’s input FIFO

(also in DRAM). The DMA controller can also perform advanced functions such as start code search,

relieving the RISC processor. The System Sync

function is used to control the timing of MPEG picture decoding. The MPEG Video decoder processes I, B and P frames, and writes to video frame

buffers in DRAM, for output to the display. Special

anti-tearing logic ensures currently displayed

frame buffers are not overwritten.

3.9

Audio Processing

Compressed Audio data is read from the DVD disk

into an input FIFO in DRAM. The data is decompressed, then written to a PCM output FIFO, also in

DRAM. Presentation time stamps (PTS) are extracted from the stream to update the STC, in order

to maintain audio/video synchronization. The

DMA and decompression stages of audio processing can be done with a combination of the DMA

unit, DSP and RISC processors. The DSP is optimized for audio processing, so most common formats can be handled by the DSP alone, including

AC-3, MPEG2 audio, and others. The DSP has

enough reserve bandwidth to handle the Karaoke

echo-mix and pitch shift, and AC-3 down-mix

functions.

The audio output data is written into a DRAM

FIFO in 16, 18, 20 or 24-bit PCM format. A flexible audio output stage can simultaneously output 8

channels of PCM data to audio DACs, plus an IEC958 encoded output, at up to 96 kHz. The IEC-958

output has fully programmable channel status

(commercial), and provides a flexible solution to

support all IEC-958 modes for User Data.

21

CS98100

The audio interface also includes a flexible PCM

input interface, which can input a wide range of

protocols from IEC-958 receiver. Another, lowcost approach for audio input is the internal sigmadelta demodulator. This module inputs a digital

PWM version of the audio input, which can be created on the board using an inexpensive ramp generator and comparator. The sigma-delta demodulator

uses a set of programmable filters to reconstruct 9bit (mono) audio data at up to 12 kHz sampling frequency.

3.10 Video Processing

The CS98100 Video processor is a powerful, fully

programmable video post processing engine that

displays video on an interlaced TV or a progressive

HDTV. A 16-tap polyphase vertical filter is fully

programmable on a line-by-line basis, to provide

high quality vertical scaling and interlaced field

conversion. Horizontal filtering is done with a programmable 16-tap polyphase filter. This advanced

filter processing is used for de-interlacing, zoom,

and frame size conversion.

Source mode of interlaced or progressive is determined from the disk type automatically. For progressive source detection, 3:2 pulldown is detected

from status flags in the video stream to ensure optimized playback. Interlaced video source is filtered up to progressive size output using the

bilinear vertical filter. This is visibly superior to

simple line doubling. Each 240 line field being filtered and output at 480p. Progressive video source

is output at the full progressive resolution. Each

480 line frame output at 480p. Source mode of interlaced or progressive is determined from the disk

type. For progressive source detection, 3:2 pulldown is simply detected from status flags in the

video stream.

Zoom is fully programmable, from 1X to 500X

zoom, with any value in between. Frame type conversion, from NTSC to PAL, or PAL to NTSC, is

done with a the bilinear vertical filter, reducing

22

flicker and jaggies.

There is a programmable gamma-correction lookup table for the final output. Cirrus Logic provides

some easy to use utilities in order to get the best advantage of the powerful video filtering capabilities

of the CS98100. The video encoder sends progressive or interlaced digital video data to the internal

video encoder, and can output parallel digital data

to an external video encoder.

The video processor also allows multiple video

plain overlay (main video / sub-picture / on-screen

display). The sub-picture unit is a hardware-only

solution which performs high-quality vertical scaling for PAL/NTSC conversion, and full support for

DVD (sub-picture) and SVCD (OGT) modes. The

on-screen display unit features 2-bit and 4-bit pixels, 16 transparency levels, and three independent

regions of up to full-screen size. The picture-in-picture unit can place a 1/2 or 1/4 screen sized window

anywhere on the screen. This feature can be used

for special effects, such as snapshot freeze and

zoom assist.

3.11 Video Encoder

The video encoder uses three 10-bit DACS to convert digital data to component (RGB or YPRPB) or

composite (composite plus S-Video) analog video.

The output can be interlaced (PAL/NTSC) or high

resolution progressive. In progressive mode, the

video encoder will typically drive YPRPB to a 525line television at 59.94 Hz, although other output

modes are possible, such as 625 lines and RGB.

The encoder performs the Macrovision copy protection function for all modes (revision 7.1 for interlaced, revision 1.03 for progressive). Other

features include built-in voltage reference, color

bar generator, individual power-down control for

each DAC, programmable baseband filters, color/contrast/tint controls, Closed Captioning (interlaced modes), wide screen signalling (PAL mode),

and Copy Generation Management System (NTSC

and progressive modes).

CS98100

4. MEMORY MAP AND REGISTERS

4.1

Processor Memory Map

The CS98100 externally supports up to 32 Mbytes DRAM and 16 Mbytes ROM/NVRAM. Table 9 lists

the memory map as viewed by the RISC processor, and identifies whether each segment is mapped or

cacheable.

Processor byte address

Description

Cacheable

0000_0000 – 07FF_FFFF

DRAM (mapped)

Y

8000_0000 - 81FF_FFFF

DRAM (32 Mbytes)

Y

9400_0000 – 9CFF_FFFF

16 bit NVRAM write (16 Mbytes)

N

9C00_0000 – 9CFF_FFFF

16 bit NVRAM/ROM (16 Mbytes)

Y

9D00_0000 – 9DFF_FFFF

8 bit NVRAM/ROM (16 Mbytes)

Y

A000_0000 – A1FF_FFFF

DRAM (32 Mbytes)

N

B000_0000 – B003_FFFF

Internal I/O (256 Kbytes)

N

B400_0000 – BCFF_FFFF

16 bit NVRAM write (16 Mbytes)

N

BC00_0000 – BCFF_FFFF

16 bit NVRAM/ROM (16 Mbytes)

N

BD00_0000 – BDFF_FFFF

8 bit NVRAM/ROM (16 Mbytes)

N

C000_0000 – FFFF_FFFF

DRAM (mapped)

Y

Table 9. Memory Map - RISC Processor

4.2

Host Port Memory Map

Table 10 lists the memory map as viewed by host slave port.

Host byte address

Description

0000 0000 – 003F FFFF

Internal I/O Space

1000 0000 – 13FF FFFF

DRAM space (16 Mbytes)

1400 0000 – 17FF FFFF

NVRAM space (16 Mbytes)

Table 10. Host Port Memory Map

23

CS98100

4.3

Internal IO Space Map

Table 11 shows how the Internal IO space is mapped between general registers, internal SRAM ports, and

the RISC processor debug port.

Byte address offset

Description

0_0000 – 0_2FFF

General registers

0_3000 – 1_FFFF

General Internal SRAM

2_0000 – 2_FFFF

RISC Internal SRAM/Registers

Table 11. Internal IO Space Map

4.4

CS98100 Register Space

Table 12 lists the register groups, and how they are split among the main CS98100 functional blocks.

CS98100 Register

Block

000xx, 010xx

General

001xx

Host

002xx

DRAM Controller (DRC)

003xx

DMA

004xx

CD/DVD Interface

005xx

Serial DVD (DVDS)

006xx

DSP

007xx

Sync Control

008xx

MPEG Video Decoder

00Axx

Picture-in-picture

00Bxx

Video Processor

00Cxx

Subpicture Display

00Dxx

On-screen Display

00Exx

PCM In/Out

02xxxx

RISC Processor

Table 12. CS98100 Register Map and Blocks

Table 13 lists all the registers for the CS98100 and their addresses, and indicates whether the registers are

read/write (R/W), read only (RO) or write only (WO).

24

CS98100

Address

Type

Function

Register Name

0

R/W

General

Command

10

R/W

General

InterProc_Comm_Register_0

14

R/W

General

InterProc_Comm_Register_1

18

R/W

General

InterProc_Comm_Register_2

10C

R/W

General

InterProc_Comm_Register_3

20

R/W

General

Semaphore_Register_0

24

R/W

General

Semaphore_Register_1

28

R/W

General

Semaphore_Register_2

02C

R/W

General

Semaphore_Register_3

30

R/W

General

Semaphore_Register_4

34

R/W

General

Semaphore_Register_5

38

R/W

General

Semaphore_Register_6

03C

R/W

General

Semaphore_Register_7

40

RO

General (Genio)

GenIO_Read_Data

44

R/W

General (Genio)

GenIO_Write_Data

48

R/W

General (Genio)

GenIO_Three_State_Enable

04C

R/W

General (Genio)

GenIO_Positive_Edge

50

R/W

General (Genio)

GenIO_Negative_Edge

54

R/W

General (Genio)

GenIO_Interrupt_Status

58

R/W

General (Genio)

GenIO_Positive_Edge_Mask

05C

R/W

General (Genio)

GenIO_Negative_Edge_Mask

60

R/W

General (Genio)

GenIO_Level_Mask

1040

RO

General (Genio)

GenIO2_Read_Data

1044

R/W

General (Genio)

GenIO2_Write_Data

1048

R/W

General (Genio)

GenIO2_Three_State_Enable

1064

R/W

General (Genio)

GenIO2_Mode

1068

RO

General (Genio)

GenIODVD_Read_Data

106C

R/W

General (Genio)

GenIODVD_Write_Data

Table 13. CS98100 Registers

25

CS98100

Address

Type

Function

Register Name

1070

R/W

General (Genio)

GenIODVD_Three_State_Enable

1074

R/W

General (Genio)

GenIODVD_Mode

68

R/W

General (Serial IF1)

Ser1_Mstr_Byte_Read_Subaddress_Write

06C

R/W

General (Serial IF1)

Ser1_Mstr_Write_1Byte

70

R/W

General (Serial IF1)

Ser1_Mstr_Write_2Bytes

74

R/W

General (Serial IF1)

Ser1_Mstr_Control

78

RO

General (Serial IF1)

Ser1_Mstr_Status

07C

RO

General (Serial IF1)

Ser1_Mstr_Read_Data

80

R/W

General (Interrupt)

RSK_Interrupt_Mask

84

WO

General (Interrupt)

RSK_Interrupt_Set

88

R/W

General (Interrupt)

RSK_Interrupt_Status

08C

RO

General (Interrupt)

RSK_Interrupt_Cause

90

R/W

General (Interrupt)

DSP_Interrupt_Mask

94

WO

General (Interrupt)

DSP_Interrupt_Set

98

R/W

General (Interrupt)

DSP_Interrupt_Status

09C

RO

General (Interrupt)

DSP_Interrupt_Cause

0A0

R/W

General (Interrupt)

RSK_Interrupt_Mask2

0A4

WO

General (Interrupt)

RSK_Interrupt_Set2

0A8

R/W

General (Interrupt)

RSK_Interrupt2_Status

0AC

RO

General (Interrupt)

RSK_Interrupt_Cause2

0B0

R/W

General (Interrupt)

DSP_Interrupt_Mask2

0B4

WO

General (Interrupt)

DSP_Interrupt_Set2

0B8

R/W

General (Interrupt)

DSP_Interrupt2_Status

0BC

RO

General (Interrupt)

DSP_Interrupt_Cause2

0C0

R/W

General (Timer)

Timer_0

0C4

R/W

General (Timer)

Timer_1

0C8

R/W

General (Timer)

Timer_2

0CC

R/W

General (Timer)

Timer_3

0D0

R/W

General (Timer)

Timer_Control

0D4

RO

General (Timer)

Performance_Monitor_Count

Table 13. CS98100 Registers (Continued)

26

CS98100

Address

Type

Function

Register Name

0D8

R/W

General (Timer)

Timer_M_Over_N

0DC

R/W

General (IR)

IR_Glitch_Max

0E0

R/W

General (IR)

IR_Control

0E4

R/W

General (IR)

IR_Dram_Start_Address

0E8

R/W

General (IR)

IR_Dram_End_Address

0EC

RO

General (IR)

IR_Dram_Write_Address

0F0

R/W

General (PLL)

PLL_Control_Register1

10F0

R/W

General (PLL)

Low_Power_Clock_Control

0F4

R/W

General (PLL)

PLL_Control_Register2

0F8

R/W

General (PLL)

PLL_Turn_Off

10F8

R/W

General (PLL)

PLL_Monitor

0FC

R/W

General (PLL)

PLL_Clock_Divider

1000

R/W

General (DMA)

DMA2_Source_Addr

1004

R/W

General (DMA)

DMA2_Dest_Addr

1008

R/W

General (DMA)

DMA2_Size

10B0

R/W

General (Serial IF2)

Ser2_Mstr_Write_Data_0

10B4

R/W

General (Serial IF2)

Ser2_Mstr_Write_Data_1

10B8

R/W

General (Serial IF2)

Ser2_Mstr_Write_Data_2

10BC

R/W

General (Serial IF2)

Ser2_Mstr_Write_Data_3

10C0

RO

General (Serial IF2)

Ser2_Mstr_Read_Data_0

10C4

RO

General (Serial IF2)

Ser2_Mstr_Read_Data_1

10C8

RO

General (Serial IF2)

Ser2_Mstr_Read_Data_2

10CC

RO

General (Serial IF2)

Ser2_Mstr_Read_Data_3

10D0

R/W

General (Serial IF2)

Ser2_Mstr_Setup

10D4

R/W

General (Serial IF2)

Ser2_Mstr_Command_Status

10E0

R/W

General (Serial IF2)

Ser3_Control

10E4

R/W

General (Serial IF3)

Ser3_Write_Data

10E8

RO

General (Serial IF3)

Ser3_Read_Data

100

R/W

Host

Device_1_Control

104

R/W

Host

Device_2_Control

Table 13. CS98100 Registers (Continued)

27

CS98100

Address

Type

Function

Register Name

108

R/W

Host

Device_3_Control

10C

R/W

Host

Device_4_Control

110

R/W

Host

Write_Data_Port

114

RO

Host

Read_Data_Port

120

R/W

Host

Host_Start_Address

124

R/W

Host

Dram Start Address

128

R/W

Host

Stream_Transfer_Size

12C

R/W

Host

DRAM_Burst_Threshold

134

R/W

General

Ser1_Slave_Address

13C

R/W

Host

Host_Master_Control

200

R/W

Dram controller

DRAM_Controller_Priority0

204

R/W

Dram controller

DRAM_Controller_Priority1

208

R/W

Dram controller

DRAM_Controller_Priority2

20C

R/W

Dram controller

DRAM_Controller_Priority3

210

R/W

Dram controller

DRAM_Controller_Priority4

214

R/W

Dram controller

DRAM_Controller_Setup

218

R/W

Dram controller

DRAM_Command

21C

R/W

Dram controller

DRAM_Controller_Mb_Width

220-224

R/W

Dram controller

DRAM_Controller_Debug

300

WO

DMA

DMA_Enable

304

R/W

DMA

DMA_Control

308

RO

DMA

DMA_Status

30C

R/W

DMA

Xfer_Byte_Cnt

310

R/W

DMA

Dram_Byte_Start_Addr

314

R/W

DMA

Sram_Byte_Start_Addr

318

R/W

DMA

Fifo_Start_Rd_Addr

31C

R/W

DMA

Fifo_Start_Wr_Addr

328

R/W

DMA

Search_Control

32C

RO

DMA

Search_Status

330

R/W

DMA

Fifo_End_Rd_Addr

Table 13. CS98100 Registers (Continued)

28

CS98100

Address

Type

Function

Register Name

334

R/W

DMA

Fifo_End_Wr_Addr

338

R/W

DMA

Lines_and_Skip

33C

R/W

DMA

Mask_Pattern_Match

400

R/W

CD/DVD

DVD_Control

404

R/W

CD/DVD

DVD_Fifo_Base_Address

408

R/W

CD/DVD

DVD_Fifo_Size

40C

R/W

CD/DVD

DVD_Sector

410

RO

CD/DVD

DVD_Start_of_Sector

414

RO

CD/DVD

DVD_Current_Dram_Address

418

R/W

CD/DVD

CD_Control

41C

R/W

CD/DVD

CD_Error_Status

438

RO

CD/DVD

DVD_Status

440

R/W

CD/DVD

DCI_Control_Reg

444

RO

CD/DVD

DCI_Status

448

R/W

CD/DVD

DCI_Dram_Rd_Start_Addr

44C

R/W

CD/DVD

DCI_Dram_Wr_Start_Addr

450

R/W

CD/DVD

DCI_Mbytes_Sent

454

R/W

CD/DVD

DCI_Mbytes_Switch

458

RO

CD/DVD

DCI_Diagnostic

45C

R/W

CD/DVD

DCI_Active

500

R/W

DVDS

DVDS_Control

504

R/W

DVDS

DVDS_DataSwap _Mode

508

R/W

DVDS

DVDS_Flow_Control_Ref

510

R/W

DVDS

Track_Buffer_Base

514

R/W

DVDS

Track_Buffer_End

518

RO

DVDS

Track_Buffer_Current_Address

534

RO

DVDS

DVDS_Sector_ID

53C

RO

DVDS

DVDS_Bad_Sector_ID

544

R/W

DVDS

Interrupt_Status

548

R/W

DVDS

Interrupt_Enable

Table 13. CS98100 Registers (Continued)

29

CS98100

Address

Type

Function

Register Name

54C

R/W

DVDS

DRAM_Underflow_Status

550

R/W

DVDS

Input_Data_Counter

600

WO

DSP

DSP_Boot_Code_Start_Address

604

WO

DSP

DSP_Run_Enable

6XX

RO

DSP

DSP_Program_CntRun_Status

700

R/W

Sync Control

Audio_Sync_Control

704

R/W

Sync Control

Video_Sync_Control

708

RO

Sync Control

Video_Sync_Status

70C

R/W

Sync Control

Wait_Line

710

R/W

Sync Control

Frame_Period

714

R/W

Sync Control

STC_Interval

718

R/W

Sync Control

System_Time_Clock

71C

R/W

Sync Control

Top_Bits

720

R/W

Sync Control

Video_PTS_FIFO_Start_Address

724

R/W

Sync Control

Video_PTS_FIFO_End_Address

728

R/W

Sync Control

Video_PTS_FIFO_Write_Address

72C

RO

Sync Control

Video_PTS_FIFO_Read_Address

730

R/W

Sync Control

Subpicture_PTS_FIFO_Start_Address

734

R/W

Sync Control

Subpicture_PTS_FIFO_End_Address

738

R/W

Sync Control

Subpicture_PTS_FIFO_Write_Address

73C

RO

Sync Control

Subpicture_PTS_FIFO_Read_Address

740

R/W

Sync Control

Highlight_Start_PTS

744

R/W

Sync Control

Highlight_End_PTS

748

R/W

Sync Control

Button_End_PTS

74C

RW

Sync Control

Highlight_Control_Information_Address

750

R/W

Sync Control

Video_PTS

754

R/W

Sync Control

Audio_PTS

758

RO

Sync Control

Subpicture_PTS

75C

RO

Sync Control

Audio_Time

760

RO

Sync Control

Video_Sync_Debug

Table 13. CS98100 Registers (Continued)

30

CS98100

Address

Type

Function

Register Name

764

R/W

Sync Control

SP_DRC_VPTS_Debug

768

R/W

Sync Control

Frame_Count_Interrupt

76C

R/W

Sync Control

Video_DTS

770

RO

Sync Control

Sync_Interrupt_Status

774

R/W

Sync Control

Sync_Interrupt_Control

778

WO

Sync Control

Sync_Interrupt_Set

77C

WO

Sync Control

Sync_Interrupt_Clear

800

R/W

MPEG Vid. Decoder

MPEG_Video_Control

804

R/W

MPEG Vid. Decoder

MPEG_Video_Setup

808

R/W

MPEG Vid. Decoder

MPEG_Video_FIFO_Start_Address

80C

R/W

MPEG Vid. Decoder

MPEG_Video_FIFO_End_Address

810

RO

MPEG Vid. Decoder

MPEG_Video_FIFO_Current_Address

814

RO

MPEG Vid. Decoder

MPEG_Video_Horiz_Pan_Vector

818

WO

MPEG Vid. Decoder

MPEG_Video_FIFO_Add_Bytes

81C

RO

MPEG Vid. Decoder

MPEG_Video_FIFO_Curr_Bytes

820

R/W

MPEG Vid. Decoder

MPEG_Video_FIFO_Interrupt_Bytes

824

RO

MPEG Vid. Decoder

MPEG_Video_FIFO_Total_Bytes

828

RO

MPEG Vid. Decoder

MPEG_Video_Status

82C

R/W

MPEG Vid. Decoder

Macroblock Width_Height

830

RO

MPEG Vid. Decoder

MPEG_Video_Debug

834

R/W

MPEG Vid. Decoder

MPEG_U_Offset

83C

R/W

MPEG Vid Decoder

MPEG_I_Base_Register

840

R/W

MPEG Vid Decoder

MPEG_P_Base_Register

844

R/W

MPEG Vid Decoder

MPEG_Dest_Control

848

RO

MPEG Vid Decoder

MPEG_Software_Flags

84C

R/W

MPEG Vid Decoder

MPEG_V_Offset

854

R/W

MPEG Vid Decoder

MPEG_AntiTearWindow

858

R/W

MPEG Vid Decoder

MPEG_Error_Pos

A00

R/W

PIP

PIP_Control

A04

R/W

PIP

PIP_VidBrdStartX

Table 13. CS98100 Registers (Continued)

31

CS98100

Address

Type

Function

Register Name

A08

R/W

PIP

PIP_VidBrdEndX

A0C

R/W

PIP

PIP_VidBrdStartY

A10

R/W

PIP

PIP_VidBrdEndY

A14

R/W

PIP

PIP_BorderClr

A18

R/W

PIP

PIP_Vscale

A1C

R/W

PIP

PIP_Line_Offnum_Bot

A20

R/W

PIP

PIP_FrBaseY

A24

R/W

PIP

PIP_FrBaseU

A28

R/W

PIP

PIP_FrBaseV

A2C

R/W

PIP

PIP_Line_Width

A30

R/W

PIP

PIP_ Line_Offnum_Top

A34

R/W

PIP

PIP_Frame_Size

B00

R/W

Video Processor

Video_Processor_Control

B04

R/W

Video Processor

Video_DRAM_Line_Length

B08

R/W

Video Processor

Display_ActiveX

B0C

R/W

Video Processor

Display_ActiveY

B10

R/W

Video Processor

Blank_Color

B14

R/W

Video Processor

Internal_Hsync_Count

B18

R/W

Video Processor

Internal_Vsync_Count

B1C

R/W

Video Processor

Horizontal_Y_Offset

B20

R/W

Video Processor

Horizontal_UV_Offset

B24

R/W

Video Processor

Vertical_Offset

B28

R/W

Video Processor

Video_Line_Size

B2C

R/W

Video Processor

Frame_Buffer_Base

B30

R/W

Video Processor

Video_Line_Mode_Buffer

B34

R/W

Video Processor

Horizontal_Vertical_Filter

B38

R/W

Video Processor

Source_X_Offset

B3C

R/W

Video Processor

Horizontal_Video_Scaling

B40

R/W

Video Processor

Frame_V_Buffer_Compressed_Offset

B44

WO

Video Processor

Mb_Width

Table 13. CS98100 Registers (Continued)

32

CS98100

Address

Type

Function

Register Name

B48

WO

Video Processor

Anti-Flicker

B4C

WO

Video Processor

Anti-Flicker

B50

WO

Video Processor

Anti-Flicker

B54

WO

Video Processor

Anti-Flicker

B58

WO

Video Processor

Anti-Flicker

B5c

WO

Video Processor

Gamma Control

B60

WO

Video Processor

Gamma Control

B64

WO

Video Processor

Gamma Control

B68

WO

Video Processor

Gamma Control

B6C

WO

Video Processor

Gamma Control

B70

WO

Video Processor

Gamma Control

B74

WO

Video Processor

Gamma Control

B78

WO

Video Processor

Gamma Control

B7C

R/W

Video Processor

ENC_Field_at_EAV

C00

R/W

Subpicture

Subpicture_Color0

C04

R/W

Subpicture

Subpicture_Color1

C08

R/W

Subpicture

Subpicture_Color2

C0C

R/W

Subpicture

Subpicture_Color3

C10

R/W

Subpicture

Subpicture_Color4

C14

R/W

Subpicture

Subpicture_Color5

C18

R/W

Subpicture

Subpicture_Color6

C1C

R/W

Subpicture

Subpicture_Color7

C20

R/W

Subpicture

Subpicture_Color8

C24

R/W

Subpicture

Subpicture_Color9

C28

R/W

Subpicture

Subpicture_Color10

C2C

R/W

Subpicture

Subpicture_Color11

C30

R/W

Subpicture

Subpicture_Color12

C34

R/W

Subpicture

Subpicture_Color13

C38

R/W

Subpicture

Subpicture_Color14

C3C

R/W

Subpicture

Subpicture_Color15

Table 13. CS98100 Registers (Continued)

33

CS98100

Address

Type

Function

Register Name

C40

R/W

Subpicture

Subpicture_DCI_Address

C44

R/W

Subpicture

Subpicture_HLI_Address

C50

R/W

Subpicture

Subpicture_Control

C54

R/W

Subpicture

Subpicture_Display_Offset

C58

R/W

Subpicture

Subpicture_Display_Scale

D00

RO

On Screen Display

OSD_Status

D04

R/W

On Screen Display

OSD_Control

D08

R/W

On Screen Display

OSD_Color_Number

D0C

R/W

On Screen Display

OSD_Color_Data

D10

R/W

On Screen Display

OSD_Region1_Control

D14

R/W

On Screen Display

OSD_Region1_Hlimits

D18

R/W

On Screen Display

OSD_Region1_Vlimits

D1C

R/W

On Screen Display

OSD_Region1_DramBase

D20

R/W

On Screen Display

OSD_Region2_Control

D24

R/W

On Screen Display

OSD_Region2_Hlimits

D28

R/W

On Screen Display

OSD_Region2_Vlimits

D2C

R/W

On Screen Display

OSD_Region2_DramBase

D30

R/W

On Screen Display

OSD_Region3_Control

D34

R/W

On Screen Display

OSD_Region3_Hlimits

D38

R/W

On Screen Display

OSD_Region3_Vlimits

D3C

R/W

On Screen Display

OSD_Region3_DramBase

D40

R/W

On Screen Display

OSD_Blend

D44

R/W

On Screen Display

OSD_Debug1

D48

R/W

On Screen Display

OSD_Debug2

E00

R/W

PCM

PCM_Run_Clear

E04

R/W

PCM

PCM_Output_Control

E08

R/W

PCM

PCM_Out_FIFO_Start_Address

E0C

R/W

PCM

PCM_Out_FIFO_End_Address

E10

R/W

PCM

PCM_Out_FIFO_Interrupt_Address

E14

RO

PCM

PCM_Out_FIFO_Current_Address

Table 13. CS98100 Registers (Continued)

34

CS98100

Address

Type

Function

Register Name

E18

R/W

PCM

IEC958_Channel_Status

E20

R/W

PCM

PCM_Input_Control

E24

R/W

PCM

PCM_In_FIFO_Start_Address

E28

R/W

PCM

PCM_In_FIFO_End_Address

E2C

R/W

PCM

PCM_In_FIFO_Interrupt_Address

E30

R/W

PCM

PCM_Out_FIFO_Interrupt_Address2

E34

R/W

PCM

PCM_Out_FIFO_Interrupt_Address3

E38

RO

PCM

PCM_In_FIFO_Current_Address

E3C

R/W

PCM

IEC958_Output_Control

E40

R/W

PCM

IEC958_Output_FIFO_Start_Address

E44

R/W

PCM

IEC958_Output_FIFO_End_Address

E48

RO

PCM

IEC958_Output_FIFO_Current_Address

E4C

R/W

PCM

IEC958_Output_FIFO_Interrupt_Address

E50

R/W

PCM

IEC958_Output_FIFO_Add_Blocks

E58

R/W

PCM

Reserved

E5C

R/W

PCM

Reserved

E60

R/W

PCM

User_Data_Start_Frame

E64

R/W

PCM

User_Data_DRAM_Address

E68

R/W

PCM

User_Data_Interrupt_Frame

E6C

RO

PCM

User_Data_Current_Address

F00

R/W

Video Encoder

VidEnc_PowerDown

F04

RO

Video Encoder

VidEnc_Status

F40

R/W

Video Encoder

Video_Mode

F44

R/W

Video Encoder

Video_Sync

F48

R/W

Video Encoder

Video_Setup

F4C

R/W

Video Encoder

Contrast

F50

R/W

Video Encoder

Brigthness

F54

R/W

Video Encoder

Chroma_Saturation

F58

R/W

Video Encoder

Tint

F5C

R/W

Video Encoder

VideoDAC_Select

Table 13. CS98100 Registers (Continued)

35

CS98100

Address

Type

Function

Register Name

F60

R/W

Video Encoder

Test

F64

R/W

Video Encoder

Test

F68

R/W

Video Encoder

Test

F6C

R/W

Video Encoder

Burst_Gain

F70

R/W

Video Encoder

Component_Mode

F74

R/W

Video Encoder

Sync_Attenuation

F78

R/W

Video Encoder

Sync_Offset

F7C

R/W

Video Encoder

Test

F80

R/W

Video Encoder

Closed_Caption_Control

F84

R/W

Video Encoder

Closed_Caption_Data0

F88

R/W

Video Encoder

Closed_Caption_Data1

F8C

R/W

Video Encoder

Closed_Caption_Data2

F90

R/W

Video Encoder

Closed_Caption_Data3

F94

R/W

Video Encoder

WideScreen_Data0

F98

R/W

Video Encoder

WideScreen_Data1

F9C

R/W

Video Encoder

WideScreen_Data2

FA0-FFC

R/W

Video Encoder

Reserved

2xxxx

R/W

RISC

RISC Processor Registers

Table 13. CS98100 Registers (Continued)

36

CS98100

5.

PIN DESCRIPTIONS

.

DVD IF /

ATAPI IF

(27 pins)

Serial DVD

(4 pins)

Misc.

(13 pins)

Serial I/O

(8 pins)

H_D[15:0]

H_CS[3:0]

H_A[2:0]

H_ALE

H_RD

H_WR

H_RDY

DVDS_CLK

DVDS_DAT

DVDS_VLD

DVDS_SOS

M_A[11:0]

DR_BS_N

M_D[31:0]

DR_DQM[3:0]

DR_RAS_N

DR_CAS_N

DR_WE_N

DR_AP

DR_CKE

DR_CKO

NVM_CE_N

NVM_OE_N

NVM_WR_N

CS98100

HSYNC

VSYNC

CLK27_O

VDAT[7:0]

Y_G_Y

U_B_C

V_R_YC

RSET

COMP

VREF

XTLCLK_I

XTLCLK_O

RST_N

IR_IN

MFG_TST

GPIO[7:0]

SER_CLK

SER_CS

SER_DO

SER_DI

MS_SCL1

MS_SDA1

M_SCL2

M_SDA2

Memory IF

(58 pins)

Video out

(17 pins)

AUD_XCK

AUD_BCK

AUD_LRCK

AUD_DO[3:0]

IEC958_O

Audio Out

(8 pins)

AIN_DATA

AIN_LRCK

Audio In

(2 pins)

Figure 14. CS98100 Pin Layout