RS780 Family Product

Errata

Silicon Errata for RS780, RS780C, RS780L, RS780D, RS780E

RS780M, RS780MC, RS780MN, and RX781

P/N: ER_RS780B7

2008 Advanced Micro Devices, Inc.

© 2008 Advanced Micro Devices, Inc. All

rights reserved.

The contents of this document are provided in connection with

Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no

representations or warranties with respect to the accuracy or

completeness of the contents of this publication and reserves the right

to make changes to specifications and product descriptions at any time

without notice. No license, whether express, implied, arising by

estoppel, or otherwise, to any intellectual property rights are granted by

this publication. Except as set forth in AMD’s Standard Terms and

Conditions of Sale, AMD assumes no liability whatsoever, and

disclaims any express or implied warranty, relating to its products

including, but not limited to, the implied warranty of merchantability,

fitness for a particular purpose, or infringement of any intellectual

property right.

AMD’s products are not designed, intended, authorized or warranted

for use as components in systems intended for surgical implant into the

body, or in other applications intended to support or sustain life, or in

any other application in which the failure of AMD’s product could

create a situation where personal injury, death, or severe property or

environmental damage may occur. AMD reserves the right to

discontinue or make changes to its products at any time without notice.

Trademarks

AMD, the AMD Arrow logo, ATI, ATI logo, and Radeon, are trademarks of Advanced Micro Devices,

Inc.

Other product names used in this publication are for identification purposes only and may be

trademarks of their respective companies.

Revision History

Date

Revision

Description

July 31, 2008

ER_RS780B7

• Added applicability to all RS780 variants

May 27, 2008

ER_RS780B6

• Updated item # 17 and # 22

March 10, 2008

ER_RS780B5

• Added item # 24

January 29, 2008

ER_RS780B4

• Added details to item # 23

• Added item # 23

January 24, 2008

ER_RS780B3

• Changed document title

• Updated Table 1

• Updated the description of item # 22

• In item # 3, the upper bound of the recommended HT3

speed changed from 2.4GHz to 2.2GHz

January 11, 2008

ER_RS780B2

• Additional detail and clarifications added to item # 17

• Added errata # 18 through # 22

December 4, 2007

ER_RS780B1

2008 Advanced Micro Devices, Inc.

• Initial release

Page 3

RS780 Family Product Errata

Product Errata Summary

Except where otherwise noted, this product errata is applicable to RS780 family of north bridge devices

including the RS780, RS780C, RS780L, RS780D, RS780E, RS780M, RS780MC, RS780MN, and RX781.

A unique errata reference number (ERN) has been assigned to each erratum within this document for user

convenience in tracking the errata within specific revision levels. Table 1 cross-references the revisions of the

part to each erratum. An “X” indicates that the erratum applies to the revision. The absence of an “X”

indicates that the erratum does not apply to the revision. An “*” indicates advance information that the

erratum has been fixed but not yet verified. “No fix planned” indicates that no fix is planned for current or

future revisions of the ASIC.

Note: There may be missing errata numbers. Errata that have been resolved from early revisions of the ASIC

have been deleted

.

Table 1:

Cross-Reference of Product Revision to Errata

ASIC Revision

#

ERN #

Errata Description

A11

1

RS780-001

HT PHY Common Mode Voltage

X

2

RS780-002

Internal Graphics Instability at HT3 Speeds > 1.2GHz

X

3

RS780-003

HT3 Instability at 1.2GHz

X

4

RS780-004

DisplayPort AUX Channel Read Failures

X

5

RS780-005

LVDS GPIOs are not Tri-stated During Boot-up.

X

Write-Combining for All Graphics Clients is Non-Functional

A12

X

6

RS780-006

7

RS780-007

X

8

RS780-008

Intermittent System Hangs When Using Message Signal Interrupts

X

9

RS780-009

System Hangs When Enabling C1e

X

10

RS780-010

Display Corruption when Spread Spectrum is Enabled

X

11

RS780-011

The VBIOS is Unable to Access NBMISCIND Registers

X

12

RS780-012

Read-Back of DisplayPort and DirectTMDS (HDMI/DVI) Registers

X

13

RS780-013

UVD Engine Byte (Endian) Swapping Support

X

14

RS780-014

Intermittent Video Playback Hang

X

15

RS780-015

Intermittent Hangs During UVD Accelerated Video Playback

X

16

RS780-016

UVD FIFO Data Overflow

X

17

RS780-017

Native PCIE Hot Plug and Native PME Wake-up Interrupt Delivery

X

18

RS780-018

APC Bridge Subsystem Vendor ID Decode Conflict

19

RS780-019

Software-initiated Interrupt Support

X

X

20

RS780-020

External PCIE Graphics Hang with L1 Enabled

X

X

21

RS780-021

Memory Controller FIFO Overflow at Reduced Engine Speeds

X

X

22

RS780-022

Dropped Host Read

X

X

23

RS780-023

DAC Output Imbalance

24

RS780-024

CLMC Warmboot Failure

Graphics Corruption in WHQL D3D Depth Bias Test

2008 Advanced Micro Devices, Inc.

A13

X

X

X

*

No Fix Planned

X

X

Page 4

RS780 Family Product Errata

X

X

RS780 Product Errata

3

(ERN # RS780-003)

HT3 Low Speed Instability

Description

HT3 instability has been observed when running the HT link at speeds between 1.2 GHz and 1.6 GHz. This

problem, which only affects some ASICs, has been identified as an issue with the receiver DLL in the HT PHY

when running in this frequency range.

Potential Effect on System

For an ASIC that does exhibit this sensitivity, the system will show a high retry count on the HT link which may

result in system failures, including system hangs (black screen), screen corruption, or a frozen screen.

Suggested Workaround

For all configurations, HT3 speeds should be limited to running between 1.8 GHz and 2.2 GHz.

Fix Planned

Yes. To be implemented in A13 silicon

2008 Advanced Micro Devices, Inc.

Page 5

RS780 Family Product Errata

8

Intermittent System Hangs When Using Message Signal

Interrupts

(ERN # RS780-008)

Description

Intermittent system hangs are observed when enabling Message Signal Interrupts (MSI). The root cause has

been determined to be due to an unaligned bus-master write in the DMA request to the CPU when a device

sends an interrupt using the MSI method.

Potential Effect on System

Intermittent system hangs will occur when enabling Message Signal Interrupts (MSI) initiated by the north

bridge. Any MSI initiated by other devices will not be affected.

Suggested Workaround

The display driver workaround implemented for A11 is also required for A12. All current driver revisions

(including older drivers that supported only A11) include this workaround for both A11 and A12.

Fix Planned

Yes. To be implemented in A13 silicon

2008 Advanced Micro Devices, Inc.

Page 6

RS780 Family Product Errata

17

Native PCIE Hot Plug and Native PME Wake-up Interrupt Delivery

(ERN # RS780-017)

Description

A logic issue has been identified in the north bridge that prevents internally generated MSI (Message Signal

Interrupts) and external PME (Power Management Event) messages from propagating to the CPU.

Potential Effect on System

This issue only affects new PCIE native features in which control of PME and hot plug is turned over to the

Vista Operating System instead of to the BIOS firmware. As such, only Vista native mode PME and native

mode hot plug features will be affected. Wake-up using PME is still supported via normal ACPI methods (nonnative PCIE mode) which continues to be fully supported by the RS780 and SB700. ACPI-based hot plug, for

example, for ExpressCards continues to be supported via normal ACPI methods (General Purpose Event

triggered SCI and BIOS ASL code event handler).

Suggested Workaround

For Vista, platforms should implement legacy hot plug and legacy PME features as per normal ACPI methods.

From a hardware perspective, this includes the implementation of the sideband connections (CPPE# and

WAKE#) from the ExpressCard interface to the south bridge GEVENT pins.

Fix Planned

Yes, fixed in A13 silicon. However, software support for native hot plug and PME is still under development,

requiring that customer designs continue to support the legacy methods. As such, the sideband connections

mentioned above must be maintained when using A13 silicon.

2008 Advanced Micro Devices, Inc.

Page 7

RS780 Family Product Errata

18

APC Bridge Subsystem Vendor ID Decode Conflict

(ERN # RS780-018)

Description

Overwriting the sub-system vendor ID (offset 0xB4) in the APC configuration space will result in the vendor ID

(offset 0x0) being erroneously overwritten in the APC configuration space.

Potential Effect on System

If the register is overwritten, any utilities that references the APC configuration space will report back the

updated vendor ID (OEM data instead of AMD data).

Suggested Workaround

Do not overwrite the SSID/SVID values in the APC configuration space. If required, OEM-specific SSID/SVID

data should be programmed in the internal graphics PCI configuration space (bus1, dev5, func0).

Fix Planned

None

2008 Advanced Micro Devices, Inc.

Page 8

RS780 Family Product Errata

19

(ERN # RS780-019)

Software-Initiated Interrupt Support

Description

Software-initiated (display driver and VBIOS) interrupts do not function on A12 silicon.

Potential Effect on System

Features that would typically employ the use of software-triggered interrupts cannot be implemented using

software-triggered interrupts. These features include:

•

Display switch requests (e.g., display hotkey switch support)

•

Expansion mode change requests (e.g., center/expansion hotkey switch support)

•

Forced power state change requests

•

System power source change requests

•

Display configuration change request (e.g., display mapping change due to docking/ undocking)

Suggested Workaround

A display driver polling scheme (which is enabled via a driver packaging option) is available as a workaround

to this issue. Apart from the change to the driver packaging options, this workaround is transparent to the

OEM/ODM implementation. All of the existing functionality that relies on the software interrupt will continue to

function through the use of the polling method.

Fix Planned

Yes. To be implemented in A13 silicon

Note: This erratum is not applicable to the RX781 which does not support internal graphics

2008 Advanced Micro Devices, Inc.

Page 9

RS780 Family Product Errata

20

External PCIE Graphics Hang with L1 Enabled

(ERN # RS780-020)

Description

When a PCIE graphics endpoint device issues a PM_REQ (request entry to L1) and the root complex (i.e.,

north bridge) issues a TLP (data packet) prior to issuing a PM_REQ (ack entry to L1), the endpoint will enter

L1 without acknowledging the TLP. Under this condition, the north bridge will issue replays and eventually

hang because it has not received an ACK to its TLP.

Potential Effect on System

Although ATI/AMD PCIE graphics boards are not subject to this problem, non-AMD graphics boards have

been observed to hang when L1 is enabled. Please note, however, that the non-AMD graphics boards that

were tested did not support L1 and this issue was only observed after overriding the setting for the L1

capability in the configuration space of the add-in board. As such, there is no end-user impact as a result of

this issue until which time non-AMD PCIE graphics card vendors may enable L1 support.

Suggested Workaround

Disable L1 for the PCIE graphics link in the SBIOS upon detecting A12 silicon in combination with a nonAMD/ATI PCIE graphics vendor ID.

Fix Planned

Yes. To be implemented in A13 silicon

2008 Advanced Micro Devices, Inc.

Page 10

RS780 Family Product Errata

21

Memory Controller FIFO Overflow at Reduced Engine Speeds

(ERN # RS780-021)

Description

An issue has been identified that results in an overflow of an internal memory controller FIFO when a specific

traffic pattern is exercised. This pattern consists of a non-write-combined transaction followed by a writecombined transaction. The problem is only exposed when write-combining is enabled in conjunction with the

PowerShift engine clock frequency scaling feature.

Potential Effect on System

This issue may cause system hangs and/or general system instability on platforms supporting a sideport

memory interface.

Suggested Workaround

Exposure to this failure is eliminated by adjusting the PowerPlay table in the VBIOS such that the minimum

PowerShift engine frequency is set to 300MHz.

Fix Planned

Yes. To be implemented in A13 silicon

Note: This erratum is not applicable to the RX781 which does not support internal graphics

2008 Advanced Micro Devices, Inc.

Page 11

RS780 Family Product Errata

22

(ERN # RS780-022)

Dropped Host Read

Description

A host read may get dropped by the north bridge if it was preceded by a non-posted host memory write under

certain highly specific traffic and timing conditions. When the north bridge I/O controller’s (IOC) host request

buffer is full, an incoming non-posted host memory write will be internally completed and a response will be

returned to the processor prior to the IOC actually executing and completing the write which is then queued in

a buffer in front of the IOC. In this state, a subsequent host read request received from the processor will try

to claim the buffer location that is filled with the pending non-posted write resulting in the read getting dropped.

Any forward progress by the IOC’s host request buffer during the time between the non-posted write and the

read will bring the device out of the previously described state and allow for correct execution.

Potential Effect on System

This issue may cause system hangs and/or general system instability during system stress testing.

Suggested Workaround

A system BIOS workaround is used to set all transactions as non-posted and removes all south bridge devices

from the CPU MMIO map. This workaround was originally introduced in RS780 CIM-X version 2.0.2. It has

been recently updated in CIM-X version 4.1.0 to account for compatibility issues involving a limited number of

non-HD PCI audio hardware. Testing and qualification has confirmed that there is no performance impact as

a result of this workaround.

Fix Planned

Yes. To be implemented in A13 silicon

2008 Advanced Micro Devices, Inc.

Page 12

RS780 Family Product Errata

23

(ERN # RS780-023)

DAC Output Imbalance

Description

Due to an unbalanced power bus IR drop, the voltage level mismatch between the RGB channels of the DAC

may be marginally higher on RS780 A13 ASICs. Specifically, the Red (VGA interface) and Composite (TV-out

interface on mobile ASICs) gun output levels are higher in comparison to the other channels.

Potential Effect on System

This imbalance or level of mismatch is only marginally higher on RS780 A13 ASICs, and no visual effects or

colour distortion has been observed as a result of this mismatch. This imbalance may, however, result in

mismatches that will exceed the allowable 6% variation of any output voltage over the full voltage range

defined in the VESA VSIS Ver1 Rev2 RGB Video Channel to Channel Mismatch requirement.

Required Workaround

To address this issue, termination resistors on the Red and Composite channels must be modified to correct

the imbalance. The required modification involves changing the two 150Ω terminations on the Red channel to

140Ω (1%), and, if implemented on mobile platforms, also changing the two 150Ω terminations on the TV-out

Composited channel to 137Ω (1%). Only platforms using A13 silicon will need to implement this BOM change.

In order to accommodate mobile designs using existing docking stations that support non-RS780 platforms,

the diagram and table below outline the recommended resistor value changes for various configurations. All

resistor values shown below are in units of ohms with a tolerance of 1%.

RS780

Red

VGA

R1

R2

COMP

R3

R4

R5

R1

R2

VGA

140

140

TV-out

(with dualparallel

termination)

TV-out

(with single

termination)

TV

Out

Isolation

Switch

Dock

Non-Docking

Configuration

TV

Out

R6

R4

137

137

68.1

Docking Required

R1

R2

VGA

133

150

TV-out

(with dual-parallel

termination)

TV-out

(with single

termination)

VGA

R3

R3

R4

127

150

68.1

Note: This erratum is not applicable to the RX781 which does not support internal graphics

2008 Advanced Micro Devices, Inc.

Page 13

R6

150

Fix Planned

No.

R5

RS780 Family Product Errata

150

75

24

(ERN # RS780-024)

CLMC Warmboot Failure

Description

An issue has been identified on CLMC-enabled mobile platforms that will result in a warmboot hang. Under

normal CLMC operation, LDT_STOP# is driven by the RS780 whenever the CPU and north bridge are idle. In

the RS780 architecture, the flip-flop that drives the output enable of the LDT_STOP# output buffer is not reset

and will not store the intended reset value until NB_RST# is de-asserted.

In the case where LDT_STOP# is asserted prior to reset, this flip-flop will retain the asserted value (logic “1”)

causing LDT_STOP# to remain asserted until reset is de-asserted. Approximately 50-100ns is required for

this state change to be reflected at the board level. This behaviour violates the HT specification requirement

to have LDT_STOP# de-asserted 1µs before RESET de-assertion. Consequently, the CPU’s core control

logic is placed in an unexpected state resulting in the hang condition during the boot sequence. The specific

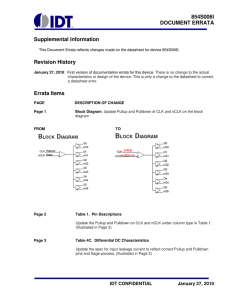

failure sequence is detailed in Figure 24-1 below.

Either NB_RST# or LDT_RST# can

be asserted while LDT_STOP# is

asserted during warmboot

50ns – 100ns

NB_RST#

LDT_RST#

LDT_STOP#

Normal Operation – LDT_STOP# is

asserted when CPU/NB is idle

Figure 24-1:

The HT specification requires that LDT_STOP# be deasserted 1µs before LDT_RST# de-assertion

Warmboot Failure Condition

Potential Effect on System

This issue will result in intermittent warmboot failures, typically observed within 100 warmboot cycles if CLMC

is enabled.

Although the failing sequence has only been observed during warmboot cycling, the identification of the root

cause of this issue does indicate that the same failing condition may be possible during S3, S4 or coldboot

scenarios where the power is sequenced prior to reset. In general, flip-flops are designed to power up in the

logic “0” state but this is not 100% guaranteed. Although no S3, S4 or coldboot failures have ever been

attributed to this during the platform qualification, there exists the possibility that the flip-flop that drives the

output enable of the LDT_STOP# output buffer will power up in the logic “1” state. This would result in the

north bridge actively driving LDT_STOP# prior to reset, resulting in the same failure condition as described

above.

2008 Advanced Micro Devices, Inc.

Page 14

RS780 Family Product Errata

Required Workaround

To workaround this issue, it is required to skew the north bridge and CPU resets. The SB700 has two

separate resets (as shown in Figure 24-2 below) which are initialized, by default, to have a 2ms skew.

Figure 24-2:

SB700 RESET Connectivity

At the PCB level, SYSRESET# of the north bridge and RESET_L of the CPU must be connected to the SB700

A_RST# and LDT_RST#, respectively. In addition, the CpuRstCtrl register of the SB700 (PM_Reg:D5h) must

be left at its default setting of “00” which forces LDT_RST# to be de-asserted 2ms after A_RST#. With this

workaround in place, the corrected reset timing sequence is shown below in Figure 24-3.

Figure 24-3:

Reset Timing With Workaround

Fix Planned

No.

2008 Advanced Micro Devices, Inc.

Page 15

RS780 Family Product Errata