A Broadband Two-stage MMIC Medium-power Amplifier

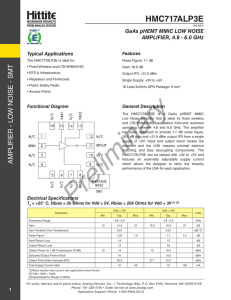

advertisement

PIERS Proceedings, Beijing, China, March 23–27, 2009 646 A Broadband Two-stage MMIC Medium-power Amplifier Yuanyuan Li and Long Jin Research Institute of Electronic Science and Technology University of Electronic Science and Technology of China, Chengdu, China Abstract— A broadband two-stage MMIC medium-power amplifier operating from 6–20 GHz is developed for EW and communication applications using 0.15 µm low-noise PHEMT process. The amplifier use a single 3-volt DC power supply, each gain stage is self-biased for class-A operation for optimal power output with minimal distortion, the two-stage feedback power amplifier has 16.5 dB small signal gain with 2.0 typical noise figure and input and output VSWRs less than 1.7 over 6–20 GHz, the output power at 1 dB compression is 16.0 dBm at 20 GHz. 1. INTRODUCTION The current trend in microwave technology is toward circuit miniaturization high-level integration, improved reliability, low power consumption, cost reduction, and high volume applications. Component size and performance are prime factors in the design of electronic systems for satellite communications, phased-array radar systems, electronic warfare, and other military applications, while small size and low cost drive the consumer electronics market. The broadband MMIC medium-power amplifiers based on PHEMT technology just agree with the above requirements. They play an increasing role in consumer electronics and military applications [1]. There are various techniques used to realize broadband power amplifiers: balanced circuit [2], feedback [3], active matching [4], resistive matching [5], distributed approach [6, 7]. The negative feedback topology has a drawback of the degradation of the gain. Generally, the chip size of the distributed and balanced amplifier is limited by the bandwidth of the transmission line and the coupler [8]. In this paper, a broadband two-stage MMIC medium-power amplifier from 6–20 GHz is developed for EW and communication applications using 0.15 µm low-noise PHEMT process. The first stage PHEMT with gate width of 6 × 30 µm was used to drive the second stage PHEMT with gate width of 6 × 70 µm. With a single 3-volt DC power supply, each gain stage is self-biased for class-A operation for optimal power output with minimal distortion, the two-stage feedback medium-power amplifier has 16.5 ± 0.5 dB small signal gain with 2.0 typical noise figure and input and output VSWRs are less than 1.7 over 6–20 GHz. The output power at 1 dB compression are 16.0 dBm at 20 GHz, the designing simulation results indicate that this method is simple and feasible. 2. PHEMT DEVICE The MMIC was implemented using a commercial PHEMT MMIC foundry (UMS), which supports 0.15 µm gate length technology. Figure 1 shows the schematic diagram of the GaAs PHEMT structure. Figure 2 shows the small signal model for 0.15 µm PHEMT. The extraction of the parasitic parameters using cold-FET method and the intrinsic parameters using hot-FET method in small signal model for the 0.15 µm PHEMT is based on Ref. [9]. G Lg Rd Cgs N+ GaAs N+ GaAs Rg Tau Gm Vgs N+ AlGaAs Ld D Rds Cds Rj Undoped AlGaAs Undpoed InGaAs 2DEG Rs Undoped GaAs Ls bikeside of substrate S Figure 1: The Schematic diagram of the GaAs PHEME structure. Figure 2: PHEMT. The Small-signal model of 0.15 µm Progress In Electromagnetics Research Symposium, Beijing, China, March 23–27, 2009 647 3. CIRCUIT DESIGN Figure 3 shows the schematic drawing of the whole amplifier including the first drive stage and the second power stage. For single voltage purpose, the self bias circuit is used by adding resistor to the source port of each device. The first matching network for a power amplifier is the output matching network which is designed to transfer maximum output power from the FET to a 50 Ω system. Lossy matching techniques in the inter-stage network were used to provide additional gain slope compensation and to provide the optimum impedance level for power matching. Finally, the input network is designed to flatten the small signal gain and improve impedance match for better input return loss. Based on these essential matching networks, an optimization and EM simulation are performed to achieve the required circuit performance. One of the most important amplifier design criteria is unconditional stability at any frequency and at any source and load conditions. The requirements of characteristics of MMIC circuit designing are as follows: the circuit should be reasonable, simple, reliable; distributing every stage’s power and gain target reasonably; reducing the stages of amplifier and using linearization technology cautiously in order to minimize the area of chip and increase the ration of eligibility. Based on the analysis above and the research about the designing of MMIC broadband power amplifier before, this paper has been given prominence to several points of consideration below, and adopt corresponding technology methods: (1) In order VD2 VD1 OUT IN PHEMT PHEMT Figure 3: The topology of the medium-power amplifier. 20 20 20GHz 13GHz 6GHz 18 15 16 10 14 5 )) 2, 2( S( B d )) 1, 1( S( B d )) 1, 2( S( B d 12 3t 2t 1t u u u o o o PPP dB(S(2,1)) 0 dB(S(1,1)) 10 dB(S(2,2)) 8 -5 6 -10 Pout1 4 Pout2 -15 2 Pout3 0 -20 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 -10 -8 -6 -4 -2 freq, GHz 0 2 4 6 8 RFpower (a) (b) 20 15 ni m 10 F N m1 freq= 13.00GHz NFmin=2.047 5 m1 0 4 6 8 10 12 14 16 18 20 22 24 freq, GHz (c) Figure 4: (a) Small-signal performance. (b) Output power vs. input power for various frequency. (c) Noise figure of amplifier. 648 PIERS Proceedings, Beijing, China, March 23–27, 2009 to realize high gain, low noise figure, we try to use 0.15 µm low-noise PHEMT process to realize the design of this MMIC medium-power amplifier; (2) Considering practical use in engineering, the amplifier use a single 3.0-volt DC power supply, each gain stage is self-biased for class-A, thus simplify the matching and minimize the area of chip and costs; (3) Considering the target of designing in all, we use two-stage amplifier, based on the requirements of gain, output power, technical model, the first stage PHEMT with gate width of 6 × 30 µm was used to drive the second stage PHEMT with gate-width of 6 × 70 µm; (4) The two stages of amplifier employ negative feedback method, thus ensures that the amplifier has flat gain and unconditional stability over 6– 20 GHz; (5) The output power’s performance can be advanced through perfect inter-stage matches, simple but useful input and output matching networks make perfect input and output VSWRs. 4. PERFORMANCE The gain and return-loss performance of the two-stage MMIC medium-power amplifier are shown in Figure 4(a). The amplifier has about 16.5 dB of small gain with good flatness over 6–20 GHz. The input return losses (S11 ) and the output return losses (S22 ) are less than −12 dB over 6–20 GHz. Figure 4(b) shows the output power as a function of input power. The amplifier has an advantage, the noise figure shown in Figure 4(c) is low. 5. CONCLUSION This paper use 0.15 µm low-noise PHEMT process to realize the design of a 6–20 GHz broadband medium-power amplifier. Through load pull’s analysis, optimal bias voltage is only 3-volt, lower than ordinarily power amplifier, and accord with currently low voltage application trend. The paper emphasize the design of feed-back networks, inter-stage matching network and bias circuits, to exert the power characteristics of active device under the condition of broadband. The combination of series-wound inductance feedback and shunt-wound negative feedback can obtain low noise figure, low input VSWR, high gain and perfect output power characteristic. The two-stage MMIC mediumpower amplifier achieve a small-signal gain (S21 ) of 16.5 dB, the average output power is around 16.0 dBm, both the input return loss and the output return loss are less than −12 dB over 6–20 GHz REFERENCES 1. Bahl, I. and P. Bhartia, Microwave Solid State Circuit Design, Vol. 1, Second edition, John Wiley & Sons, New Jersey, Hoboken, 2003. 2. Lim, J. S., S. C. Kang, and S. Nam, “MMIC 1 watt wideband power amplifier chip set using PHEMT technology for 20/30 GHz communication systems,” Asia Pacific Microwave Conference, Vol. 2, 425, 1999. 3. Kim, Y. G., S. J. Maeng, J. H. Lee, et al., “A PHEMT MMIC broad-band power amplifier for LMDS,” RAWCON Proceedings, 121, 1998. 4. Peterson, W. C., et al., “A monolithic GaAs 0.1 to 10 GHz amplifier,” IEEE Int. Microwave Symp. Dig., 354, 1981. 5. Arell, T. and T. Hongsmatip, “A unique MMIC broadband power amplifier approach,” IEEE J. Solid-State Circuits, Vol. 28, No. 10, 1005, 1993. 6. Platzker, A., K. T. Hetzler, and J. B. Cole, “Highly dense dual-channel C-X-Ku and 6–18 GHz MMIC power amplifier,” IEEE GaAs IC Symp. Digest, 339, 1991. 7. Barnes, A. R., M. T. Moore, and M. B. Allenson, “A 6–18 GHz broad-band high power MMIC for EW application,” IEEE MMT-S Digest, 1429, 1997. 8. Vendelin, G. D., A. M. Pavilo, U. L. Rohde, et al., Microwave Circuit Design, John Wiley & Son, 253, 1990. 9. Zang, S. J., R. Yang, X. Gao, et al., “The large signal modeling of GaAs HFET/PHEMT,” Chinese Journal of Semiconductors, Vol. 28, No. 3, 439, 2007.