Analysis of Depletion Region Width and Breakdown Voltages of 6H

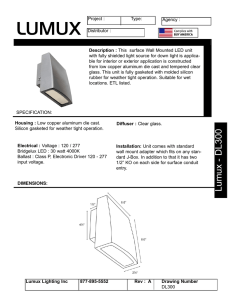

advertisement