High Performance Lateral Schottky Collector Bipolar Transistors on

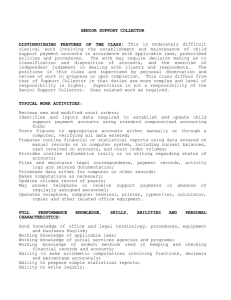

advertisement