Randomness Analysis of Pseudo Random Noise Generator

2014 Fifth International Conference on Intelligent Systems, Modelling and Simulation

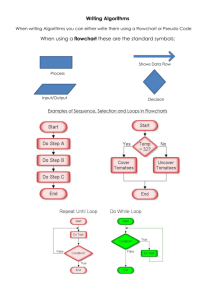

Randomness Analysis of Pseudo Random Noise Generator Using 24-bits LFSR

Siti Hazwani

Department of Electrical and Computer Engineering

Kulliyyah of Engineering, International Islamic

University Malaysia (IIUM) hazwani_me@yahoo.com

Mohammad Umar Siddiqi

Department of Electrical and Computer Engineering

Kulliyyah of Engineering, International Islamic

University Malaysia (IIUM) umarsiddiqi@iium.edu.my

Mohamed Hadi Habaebi

Department of Electrical and Computer Engineering

Kulliyyah of Engineering, International Islamic

University Malaysia (IIUM) habaebi@ieee.org

Sheroz Khan

Department of Electrical and Computer Engineering

Kulliyyah of Engineering, International Islamic

University Malaysia (IIUM) sheroz@iium.edu.my

Khalid A.S. Al-Khateeb

Department of Electrical and Computer Engineering

Kulliyyah of Engineering, International Islamic

University Malaysia (IIUM) khateeb222@yahoo.com

Zeeshan Shahid

Department of Electrical and Computer Engineering

Kulliyyah of Engineering, International Islamic

University Malaysia (IIUM) zeesh_87@hotmail.com

Abstract

—

We have described in previous work the generation of PN-sequence by employing a 4-bit shifted Linear Feedback

Shift Register (LFSR) for application into Direct Sequence

Spread Spectrum (DSSS) system by simulation. In this paper, is proposed a pseudo random number generator (PRNG) circuit consisting of 24-bit shift registers (LFSR) which has much longer period to improve statistical properties. We simulated the LFSR circuit by using Multisim 11.0 and the pseudo random sequence generated is tested with statistical test of NIST Test suite. The sequence is passed the entire selected test and we concluded that our pseudo random sequence has long enough period to be considered as random.

Keywords

—

Linear feedback shift register (LFSR), Pseudo random number generator (PRNG), pseudo random sequence, randomness tests, NIST SP800-22.

I.

I

NTRODUCTION

LFSRs are frequently used as Pseudo Random Number

Generators (PRNG) to generate a random number sequence of 1s and 0s. Such PRNG are commonly used as key elements in cryptographic applications. Having a good statistical properties, low implementation cost, low complexity and high speed are the reasons of wider acceptance of its usage [1, 2, 4, 5]. However, improper configuration of LFSR components and insufficient number of registers might not be able to recover a PRNG from the weakness of LFSR.

Since the LFSR is a linear system, they lead to be attacked by easy cryptanalysis tools. Therefore, the alternative solution such introducing the non-linearity in the system might work otherwise the period of pseudo random sequence should be long enough to ensure the security of the system. An LFSR with a short period will result to encode the different portion of data stream with the same key stream [1]. In this paper, we propose the PRNG circuit of 24-bit shift registers with maximal length of 16 777 215 states sufficient to be applied for key generation in secure data communication system.

LFSR based PN sequences [3,4] are essentially deterministically generated sequences. However, they have many of the properties possessed by a truly random binary sequence, hence the name pseudo-random or pseudo-noise sequences. The random sequences generated by PRNG play essential roles in secure cryptographic systems. It is because of the non-randomness of pseudo random sequence used in a system that might give adverse but important clue attacking the systems. For the reasons of convincing the pseudo random sequence generated is secure enough for a system, some test are proposed to show the evidence of its randomness. We can say the more tests a random sequence is passed through, the more strong the system will be. The

National Institute of Standards and Technology (NIST) have released NIST SP800-22 [3] in 2001, which is the standard test suite for randomness in the field of data security. The test suite provides a good method with strong theoretical and practical support .

The remainder of this paper is organized as follows. Section II describes the generation of pseudo random sequence. Section III describes the randomness tests.

The testing results are discussed in section IV. The conclusion is given in section V.

2166-0662/14 $31.00 © 2014 IEEE

DOI 10.1109/ISMS.2014.141

772

II.

RANDOM NUMBER GENERATOR

In this paper, a pseudo random number generator

(PRNG) circuit employing the Linear Feedback Shift

Register (LFSR) is designed and simulated using Multisims

11.0. An LFSR register is able to produce binary sequences n-bit shift register which pseudo-randomly scrolls between 2 n

-1 values [4]. Normally, the code has finite length and repeats periodically. For our case, a 24-bit

PRNG sequence generates the maximum length of 2

24

-1 =

16, 777, 215 values. The process is done very quickly because of minimal combination logic involved in the design. Once it reaches its final state, it traverses the sequence exactly as before.

Figure 1 shows the simulated circuit diagram of the proposed pseudo random noise generator making use of three 8-bit shift registers which equal to 24 bits shifted. A couple of 4015 flip-flops (U2A and U2B) represent as an 8 bit shift registers. In other words, it requires (2

24

-1) =

16777215 clock pulses before it repeats. Since the clock frequency used in this work is 1MHz, it takes about 17 seconds to repeat. Figure 2 is the generated pseudo random sequence captured from oscilloscope (XSC 1) which running in 10µs/Div timebase with amplitude of 5V/Div.

This pseudo random sequence has 1µs time period or we can say the code rate is equal to 1Mbps.

Figure1: Schematic circuit of 24-bit LFSR pseudo random number generator

Figure 2: Pseudo Random Sequence of 24-bit LFSR pseudo random number generator within 180µs to 280µs and 10V amplitude.

We have been designed the 24-bit LFSR pseudo random number generator. However, we need to have some results testifying the utility of the circuit before its applications in secure data communication. For that purpose, the pseudo random sequence generated as in Figure 2 is interpreted into binary number (0’s and 1’s) with a desired length (as the maximum length is extremely large to work on manually).

The next section provides the description summary of the selected tests.

III.

RANDOM NUMBER GENERATION TEST

For the purpose of analysis the NIST randomness test has been performed as a set of six tests. The selected minimum of 120 consecutive binary bits of LFSR pseudo random number generator output, are tested in the following sections:

A.

Frequency Mono-bit Test

This is very basic test to determine whether number of

0’s and 1’s in a sequence is about the same, i.e., fraction of

1’s is about ½ [5]. The sequence is considered random if the complementary error function ( erfc ) of S obs

/2 is larger or equal to 0.01 (pvalue ≥ 0.01). All the subsequent tests depend on the passing of this test.

B.

Frequency Test within a block

In this test, the tested stream is divided into multiple blocks each having length, M. The purpose of this test is to determine that th e frequency of 1’s in an M -bit block is approximately M/2 as would be expected under an assumption of randomness. The measurement of χ

2

( obs

) will tell how well the observed proportion of 1’s within M -block matches the expected proportion of ½ [5]. The χ

2

( obs

) will be applied into incomplete gamma function ( igamc ) with the number of block N. If the calculated value is falling into

(0.01-0.99) then one can conclude the sequence to be random, else otherwise.

C.

Runs Test

The purpose of the runs test is to determine whether the number of runs of 1’sand 0’s of various lengths is as expected for a random sequence. Particularly, this test determines whether the oscillation between such 0’s and 1’s is too fast or too slow. The large value for V n

( obs

) would indicate the fast oscillation in the string and vice versa [5].

The same decision rule of p-value as frequency mono-bit test is considered.

D.

Test for the Longest Run of Ones in a Block

The test is to determine whether the length of the longest run of 1’s within the tes ted stream is consistent with the length of that would be expected in a truly random stream.

The χ

2

( obs

) will be applied into incomplete gamma function

( igamc ) with the number of degree of freedom, K . If the calculated value is falling into (0.01, 0.99) then conclude that the sequence is random and otherwise.

773

E.

Maurer’s “Universal Statistical” Test

The purpose of this test is to detect whether or not the sequence can be significantly compressed without loss of information. A random sequence is concluded to be not significantly compressible [5,8]. As pvalue ≥ 0.01, the sequence is accepted as random.

F.

Linear Complexity Test

This test is related to a kind of PRNG which called

Linear Feedback Shift Register LFSR. The purpose of this test is to determine whether or not the stream is complex enough to be considered random [5,7]. Berlekamp-Massey algorithm is employed to determine the linear complexity of the sequence. The same decision rule as test D is considered.

IV.

RANDOMNESS TEST RESULT

In this section, we present the testing result of a set of random number generation tests as described in previous section. Table1 shows the summary of the types of tests discussed, its reference distribution (either normal distribution or chisquare (χ

2

) distribution, the parameters and the calculated p-values. Since all the p-values obtained are greater than or equal to 0.01 (pvalue ≥ 0.01) and close to 1, the results shows the randomness tests passed.

Test

T ABLE 1: NIST SUITE TEST R ESULTS FOR PRNG

Frequency

(Monobit) Test

Frequency Test within a block

Runs Test

Parameter Statistics P-value n=120,

S n

=-2 n=120,

M=24,

χ

2

( obs

)=2.83 n=120,

π=0.51,

V n

( obs

)=62

M=8,

N=16, K=3,

χ

2

( obs

)=0.86

χ

2

χ

2

χ

2

0.85

0.73

0.71

Success/

Fail

Success

Success

Success

Test for longest run of ones in a block

χ

2

0.84 Success

Maurer’s

“Universal

Statistical” Test

Linear

Complexity Test

L=2, Q=5, n=24

N=240,

M=24,

χ2(obs)=2.7

normal

χ

2

0.03

0.85

Success

Success

For a system using LFSR, it is necessary to pass the Linear Complexity Test which guarantees the sequence is complex enough to be considered as random. As we compare to the system’s test result in [2] which having p value of 0.1252, our system has much more value which tend to 1( p-value of 0.85) for Linear Complexity Test. This means that our sequence period is sufficiently long enough for a reliable system. Other tests are shown better result such as Frequency Monobit Test, Runs Test and Test for longest run of ones in a block.

V.

CONCLUSION & RECOMMENDATION

This paper has described the generation of pseudo random number sequence using 24-bits shift LFSR and tested the pseudo random sequence with some statistical test. As can be seen from Table 1, the p-value for all the tests are ≥ 0.01 and considered passe d the randomness.

Moreover, some tests shows better performance compared to others work. Thus, we can conclude that our pseudo random sequence has long enough period to be considered as random. In further work, as this such PRNG has a good performance in randomness, it can be extensively applied in any secure communication system such spread spectrum and

Ultra Wideband (UWB).

REFERENCES

[1].

F.Massodi, S.Alam and M.U. Bukhori, “An analysis of Linear

Feedback Shift Registers in stream chippers”, International Journal of Applications(0975-8887), Vol.46, No.17, May 2012,pp.46-49.

[2].

H.Rahimov, M. Babaei, M. Farhadi, “Cryptographic PRNG based on Combination of LFSR and Chaotic Logistic Map”, Applied

Mathematics, 2011, 2, pp.1531-1534.

[3].

Simon Haykin, "Pseudo-Noise Sequences", Section 7.2, Chapter 7,

Communication Systems, 4th Ed, John-Wiley & Sons, Inc., New

York, 2001.

[4].

Mark Goresky and Andrew Klapper, "Pseudonoise Sequences Based on Algebraic Feedback Shift Registers", IEEE TRANSACTIONS

ON INFORMATION THEORY, VOL. 52, NO. 4, APRIL 2006, pp.

1649 - 1662

[5].

A.Rukhtin, J.Soto, J. Nechvatal, “A Statistical Test Suite for

Random and Pseudorandom Number Generators for Cryptographic

Applications.” NIST Special Publication 800 -22 (May 15, 2011)

[6].

J. Lan, W. L. Goh, Z. H. Kong and K. S. Yeo, “ A Random number generator for low power cryptographic application”, ISOCC 2010

978-1-4244-8631-1/10/$26.00©2010 IEEE, pp.328-331.

[7].

M. Puczko, V. N. Yarmolik, “Designing cryptographic key generators with low power consumption”, Proceedings of the Third

IEEE International Workshop on Electronic Design, Test and

Applications (DELTA’06)

[8].

R. Kadir and M.A. Maarof, “ Randomness Analysis of Pseudo

Random Bit Sequence”, 2009 International Conference on

Computer Engineering and Applications IPCSIT vol.2(2011) ©

(2011) IACSIT Press, Singapore, pp.390 – 394.

[9].

K. Hamano, F. Sato and H. Yamamoto, “ A New Randomness Test

Based on Linear Complexity Profile”, IEICE Trans. Fundamentals,

Vol.E92-A, No.1, January 2009, pp. 166 – 172.

[10].

U. M. Maurer, “A Universal statisti cal Test for Random Bit

Generators”, Journal of Cryptology, vol. 5, no.2, 1992, pp.89

-105.

774