Document

advertisement

Automotive Entertainment

& Navigation

Will Zhang

High Performance Analog

Texas Instruments Semiconductor

Technologies (Shanghai)

Mar.25.2007

1

Diversity of Media Player

Performance

PMP+DVR

Game PMP

PMP

PMP+GPS

Game MP3

HDD

MP3

Video

MP3

MP3

2007

2

WHAT GPS IS

4 GPS:

4 Global Positioning System

4 How it Works:

4 GPS satellites circle the earth twice a day in a very precise orbit

and transmit signal information to earth.

4 GPS receivers take this information and use triangulation to

calculate the user's exact location. Essentially, the GPS receiver

compares the time a signal was transmitted by a satellite with the

time it was received.

4 Distance=Cxdt

4 Distance={(Xs-Xu)2+(Ys-Yu)2+(Zs-Zu)2}1/2

4 t, x, y, z parameters to be determined.

4 4 satellites signal at least

3

GPS Family

GPS Monitor

GPS

GPS Navigator

GPS Timing

4

Block Diagram--GPS Portable Navigator

Audio In

Audio Process

Mix+

Audio Codec

LCD Driver

uP

TFT Video

Display

S3C244x

MSP430

CIR Remote

Control

Power

5V,2A

Audio

OP

IIS/AC97/PCM

GPS Module

UI

Audio out:

HP: Stereo

Spk: Mono

T/S

3.5” T/S panel

Power Manager

System Power

AFE GAUGE

Lithium Battery

SDRAM

64MB

Flash

64 MB

USB 2.0

Client

Memory Storage

SD Card

Socket

5

GPS –Signal Chain

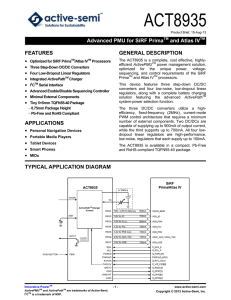

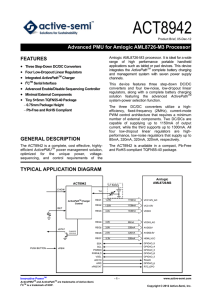

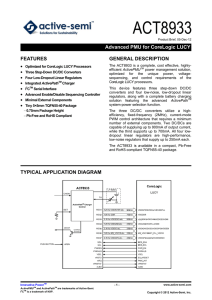

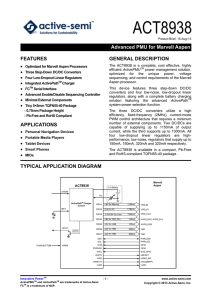

Centrality Atlas Family

UART

BT

Transceiverr

Atlas

PCM

GPS Base Band

GPS

Receiver

UART

ARM 9

Processor

Go Back

Must Have

TSC

TSC2005

I2S

Codec

AIC32

APA

TPA2012D2

Optional

6

GPS –Signal Chain

Go Back

Must Have

7

Power Architecture of GPS

Down

Converter

5v

LED

Back light

Charger

30V@20mA

LED

Backlight

Bq24070

14.4V+40V Peak

Audio

Amplifier

1 Li+

Cell

3.3V@600mA

Digital I/O

DC-DC

Vmain

TPS6202x

Bias

Regulator

TPS6202x

PMU: TPS6505x

Vgh

Vgl

TFT Panel

TPS65120

1.3V@600mA TPS65150

DC-DC

Vcore

TPS730xx

2.5V@0.3A

Vram

LDO

TI Parts

TPS717xx

On/off

Reset

3..0V@ 0.3A

LDO

RF Module

8

Power for GPS

9

Automotive Power Environment

Voltage Transition

10

Automotive Power Design

Voltage Rating: 36V,Transient >40V,

12V System 60V~80V@100ms

24V System 80~100V@100ms

Choker in series 、Bulb Capacitor Buffered

Fast Response

Other Requirements

Minimize components number,

Anti-shock

-40~+85C

Minimize soldering,

Anti-thermal shock

Soldering, Pad as big as possible

Minimize heat dissipation

Standby Current<1mA

Considering portable application always

11

Power Design for GPS

Low EMI

RF Front-end: -159db Receiving environment

Low Heat Dissipation

Minimize Temp Drift

Dynamic Voltage Control Preferred

Minimize power consumption during media playing

Maximize performance during navigation

12

GPS Charger, Always Charging?

+

Adapter

or USB

Charger

ISYS

IBAT

System

Current (A)

ICHG

1

0.8

ICHG

IBAT

0.6

0.4

0.2

ISYS

ITERM

0

当充电芯片在恒压模式时:

1. 充电电流将逐步降低

2. 系统用电超过设定的终止电流监测阈值old

3. 充电芯片稳定在设定的电压上,但 ICHG > ITERM

20

¾ 检测不到终止

¾ 安全定时器溢出

Solution:

关闭定时器或考虑外加分流电路为系统供电

13

40

60 80

Time

Power Path: Potential Issue

IADP

Adapter

+

Q1

Controller

VOUT

System Current

ISYS

System Current

ICHG

ISYS

Q2

IBAT

C1

System

IADP

Charging

Battery

Adapter current limit

Input current : IADP = IBAT + ISYS

Adapter

voltage

collapses

-

VADP

Issues:

• Input voltage collapses

Time

14

Dynamic Power Path Manag’ t(DPPM)

IADP

+

Adapter

or USB

Output

Control

Current

Control

ISYS

ISYS

DPPM

Mode

IADP

AC adapter current limit

Q2

ICHG

C1

System

当(Isys + Ichg) > IAC_LIMIT外部电压下降

太大的瞬间系统电流将导致外部供电电压明显的跌

落,从而导致系统复位或性能下降

ICHG

DPPM :

当供电电压低于设定值的时候, 减小充电电流 “发现”

交流适配器的最大电流 !!!

电池补充模式

System Voltage

VDPPM

VBAT

Time

15

BQ24070—DPPM Charger Management

26V Hi Voltage

• 交流适配器或 USB 可以在给系统供电,同时充电:

•节省两个MOSFET和电压监测器

• 更小的,更低成本的交流适配器

• 给系统提供经过稳压的供电

• 减少了内部DC-DC和外部高电压的接触,提高可靠性,降低了成本

• 延长了电池的寿命和安全性

16

TPS65050

Dual Step-down converter with 4LDOs

TPS65050

TPS65050

DCDC1 externally adjustable

DCDC1 output current: 600mA

DCDC2 externally adjustable

DCDC2 output current: 600mA

LDO voltage selectable with

DEFLDOx pins according to

table A

Output cap discharge for LDOs

PB_ONOFF functionality

4mm x 4mm 32-Pin QFN

package 0.4mm pitch

VINDCDC1/2

1R

Vbat

VCC

10uF

1uF

2.2uH

DCDC1 (I/O)

L1

STEP-DOWN

CONVERTER

600mA

FB_DCDC1

EN_DCDC1

ENABLE

MODE

DEFLDO1

DEFLDO2

DEFLDO3

DEFLDO4

PGND1

R1

Cff

10uF

R2

Interface

L2

DCDC2 (core)

STEP-DOWN

CONVERTER

600mA

EN_DCDC2

ENABLE

VLDO2

EN_LDO2

ENABLE

PGND2

VIN_LDO3/4

VLDO3

ENABLE

ENABLE

R4

4.7uF

VLDO2

4.7uF

400mA LDO

VIN

10uF

400mA LDO

VIN_LDO2

VIN

R3

DEFDCDC2

VLDO1

EN_LDO1

ENABLE

2.2uH

VLDO1

VIN_LDO1

VIN

VDCDC2

EN_LDO3

200mA LDO

EN_LDO4

VLDO4

VLDO3

2.2uF

BP

0.1uF

VLDO4

2.2uF

200mA LDO

I/O voltage

Vbat

PB_IN

Flipflop with

32ms debounce

default

turned on

AGND

17

PB_OUT

R19

TPS65050

Dual Step-down converter with 4LDOs

PREVIEW

TPS65050-LDO voltages table A

DEFLDO1

DEFLDO2

DEFLDO3

DEFLDO4

VLDO1

VLDO2

VLDO3

VLDO4

400mA LDO

400mA LDO

200mA LDO

200mA LDO

1.8V- 5.5V

Input

1.8V- 5.5V

Input

1.5V-5.5V

Input

1.5V-5.5V

Input

3.3V

3.3V

1.85V

1.85V

3.3V

3.3V

1.5V

1.5V

3.3V

2.85V

2.85V

2.7V

3.3V

3.3V

2.85V

2.85V

2.85V

2.85V

2.5V

1.85V

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

3.3V

3.3V

2.85V

2.85V

1.85V

1.5V

1.85V

1.5V

0

1

1

1

3.3V

2.85V

1.5V

1.3V

1

0

0

0

3.3V

2.85V

1.1V

1.3V

1

0

0

1

2.85V

2.85V

1.85V

1.85V

1

0

1

0

1

0

1

1

2.7V

2.5V

3.3V

3.3V

1.2V

1.5V

1.2V

1.5V

1

1

0

0

2.5V

3.3V

1.5V

1.3V

1

1

0

1

1

1

1

0

1.85V

1.8V

1.85V

2.5V

1.35V

3.3V

1.35V

2.85V

1

1

1

1

1.2V

1.8V

1.1V

1.3V

18

TPS65051

Dual Step-down converter with 4LDOs

TPS65051

VINDCDC1/2

1R

Vbat

VCC

2.2uH

1uF

TPS65051

DCDC1 externally adjustable

DCDC1 output current: 1A

DCDC2 externally adjustable

DCDC2 output current:

600mA

LDO externally adjustable

Output cap discharge for

LDOs

Reset (/Respwron) with

adjustable threshold and

hysteresis

4mm x 4mm 32-Pin QFN

package 0.4mm pitch

ENABLE

MODE

EN_DCDC1

DCDC1 (I/O)

L1

STEP-DOWN

CONVERTER

1A

FB_DCDC1

R1

22uF

Cff

10uF

R2

PGND1

MODE

L2

DCDC2 (core)

ENABLE

VIN

ENABLE

VIN

ENABLE

STEP-DOWN

CONVERTER

600mA

EN_DCDC2

VDCDC2

2.2uH

R3

10uF

DEFDCDC2

PGND2

R4

VLDO1

VIN_LDO1

VLDO1

FB1

EN_LDO1

400mA LDO

VIN_LDO2

VLDO2

EN_LDO2

400mA LDO

R5

4.7uF

R6

VLDO2

FB2

R7

4.7uF

R8

VIN

ENABLE

VIN_LDO3/4

VLDO3

EN_LDO3

200mA LDO

VLDO3

FB3

BP

R9

2.2uF

R10

0.1uF

ENABLE

VLDO4

EN_LDO4

200mA LDO

VLDO4

FB4

R11

R12

2.2uF

I/O voltage

R19

/RESET

THRESHOLD

HYSTERESIS

RESET

AGND

19

TPS65052

Dual Step-down converter with 4LDOs

PREVIEW

TPS65052

VINDCDC1/2

1R

TPS65052

DCDC1 fixed at 3.3V

DCDC1 output current: 1A

DCDC2 fixed at 1.0V / 1.3V

DEFDCDC2 = low: 1.0V

DEFDCDC2 = high: 1.3V

DCDC2 output current: 600mA

Samsung processor compatible

LDO voltage selectable with

DEFLDOx pins according to

table A

Output cap discharge for LDOs

Reset (/Respwron) with

adjustable threshold and

hysteresis

4mm x 4mm 32-Pin QFN

package 0.4mm pitch

Vbat

VCC

10uF

1uF

ENABLE

MODE

DEFLDO1

DEFLDO2

DEFLDO3

DEFLDO4

ENABLE

1.0V / 1.3V

VIN

ENABLE

VIN

ENABLE

VIN

ENABLE

ENABLE

2.2uH

DCDC1 (I/O)

L1

STEP-DOWN

CONVERTER

1A

FB_DCDC1

EN_DCDC1

10uF

PGND1

Interface

L2

DCDC2 (core)

STEP-DOWN

CONVERTER

600mA

EN_DCDC2

DEFDCDC2

VDCDC2

2.2uH

10uF

PGND2

VLDO1

VIN_LDO1

VLDO1

EN_LDO1

4.7uF

400mA LDO

VIN_LDO2

VLDO2

EN_LDO2

VLDO2

4.7uF

400mA LDO

VIN_LDO3/4

VLDO3

EN_LDO3

200mA LDO

EN_LDO4

VLDO4

VLDO3

2.2uF

BP

0.1uF

VLDO4

2.2uF

200mA LDO

I/O voltage

R19

/RESET

THRESHOLD

HYSTERESIS

RESET

AGND

20

TPS65054

Dual Step-down converter with 4LDOs

PREVIEW

TPS65054

VINDCDC1/2

1R

Vbat

VCC

2.2uH

1uF

TPS65054

DCDC1 externally adjustable

DCDC1 output current:

600mA

DCDC2 fixed to 1.05V / 1.3V

DEFDCDC2 = low: 1.3V

DEFDCDC2 = high: 1.05V

DCDC2 output current:

600mA

OMAP1710 compatible

LDO externally adjustable

Reset (/Respwron) with

adjustable threshold and

hysteresis

4mm x 4mm 32-Pin QFN

package 0.4mm pitch

ENABLE

MODE

EN_DCDC1

DCDC1 (I/O)

L1

STEP-DOWN

CONVERTER

600mA

FB_DCDC1

R1

22uF

Cff

10uF

R2

PGND1

MODE

L2

DCDC2 (core)

ENABLE

1.3V / 1.05V

VIN

ENABLE

VIN

ENABLE

STEP-DOWN

CONVERTER

600mA

EN_DCDC2

DEFDCDC2

VDCDC2

2.2uH

10uF

PGND2

VLDO1

VIN_LDO1

VLDO1

FB1

EN_LDO1

400mA LDO

VIN_LDO2

VLDO2

EN_LDO2

400mA LDO

R5

4.7uF

R6

VLDO2

FB2

R7

4.7uF

R8

VIN

ENABLE

VIN_LDO3/4

VLDO3

EN_LDO3

200mA LDO

VLDO3

FB3

BP

R9

2.2uF

R10

0.1uF

ENABLE

VLDO4

EN_LDO4

200mA LDO

VLDO4

FB4

R11

R12

2.2uF

I/O voltage

R19

/RESET

THRESHOLD

HYSTERESIS

RESET

AGND

21

TPS65056

Dual Step-down converter with 4LDOs

TPS65056

VINDCDC1/2

1R

Vbat

VCC

2.2uH

1uF

TPS65056

DCDC1 fixed at 3.3V

DCDC1 output current: 1A

DCDC2 fixed at 1.0V / 1.3V

DEFDCDC2 = low: 1.0V

DEFDCDC2 = high: 1.3V

DCDC2 output current: 600mA

Samsung processor compatible

LDO voltage externally

adjustable

Output cap discharge for LDOs

Reset (/Respwron) with

adjustable threshold and

hysteresis

4mm x 4mm 32-Pin QFN

package 0.4mm pitch

ENABLE

MODE

EN_DCDC1

DCDC1 (I/O)

L1

STEP-DOWN

CONVERTER

1A

FB_DCDC1

22uF

10uF

PGND1

MODE

L2

DCDC2 (core)

ENABLE

1.0V / 1.3V

VIN

ENABLE

VIN

ENABLE

STEP-DOWN

CONVERTER

600mA

EN_DCDC2

DEFDCDC2

VDCDC2

2.2uH

10uF

PGND2

VLDO1

VIN_LDO1

VLDO1

FB1

EN_LDO1

400mA LDO

VIN_LDO2

VLDO2

EN_LDO2

400mA LDO

R5

4.7uF

R6

VLDO2

FB2

R7

4.7uF

R8

VIN

ENABLE

VIN_LDO3/4

VLDO3

EN_LDO3

200mA LDO

VLDO3

FB3

BP

R9

2.2uF

R10

0.1uF

ENABLE

VLDO4

EN_LDO4

200mA LDO

VLDO4

FB4

R11

R12

2.2uF

I/O voltage

R19

/RESET

THRESHOLD

HYSTERESIS

RESET

AGND

22

TPS65053

Dual Step-down converter with 3LDOs

PREVIEW

TPS65053

VINDCDC1/2

1R

TPS65053

DCDC1 externally adjustable

DCDC1 output current: 600mA

VCC

1uF

DCDC1 (I/O)

ENABLE

EN_DCDC1

STEP-DOWN

CONVERTER

600mA

MODE

FB_DCDC1

R1

PGND1

R2

optionally: 1A

DCDC2 externally adjustable

DCDC2 output current: 600mA

3LDOs

LDO1, 400mA, externally

adjustable

LDO2, 200mA, externally

adjustable

LDO3, 200mA, fixed voltage

TBD

threshold input and /Reset

output

4mm x 4mm QFN package,

0.5mm pitch, 24pins

Cff 10uF

2.2uH

DCDC2 (core)

ENABLE

EN_DCDC2

STEP-DOWN

CONVERTER

600mA

DEFDCDC2

optionally: 1A

22uF

2.2uH

L1

VIN

ENABLE

VIN

ENABLE

VIN_LDO1

VLDO1

EN_LDO1

400mA LDO

L2

FB_DCDC2

PGND2

R3

Cff 10uF

R4

VLDO1

FB1

R5

4.7uF

R6

VIN_LDO2/3

VLDO2

EN_LDO2

200mA LDO

VLDO2

FB2

R7

2.2uF

R8

ENABLE

EN_LDO3

VLDO3

VLDO3

2.2uF

200mA LDO

I/O voltage

THRESHOLD

/Reset

RESET

AGND

23

R19

TPS6512x 1Inductor,4outputs

• Main Output, VMAIN

Adjustable Voltage from 3.0V to

5.6V @ 20mA max.

Post-Regulated for Low Ripple

Noise (5mV)

±0.8% Typical Accuracy

Efficiency up to 83%

• Positive / Negative Gate Voltage

Outputs, VGH / VGL

Adjustable Voltage Up To +20V / 18V @ 2mA

±3% Typical Accuracy

• Auxiliary 1.8V / 3.3V Linear

Regulator

• Automatic or Programmable OutputSequencing

• No forward leakage

• Output Short-Circuit Protected

•

•

•

•

•

•

Ultra-small solution

Fewest External components

easy to implement

High accuracy for best picture quality

High efficiency extends battery life

High Reliability

small inductor

(1608 case size)

QFN-16

3x3x0.9mm3

24

No CFF

required

small

caps

GPS – Power Chain

P/N

RTM

*Automotive Catalog; Qualified for Automotive Applications

Description

Li+ Charger

BQ24032A/70

Now

Dual/Single input 1-cell (4.2V) Li-Ion Charger w/ Power Path

Now

Single Inductor Quad output SFF TFT LCD Panel Bias

TPS6505x

Now

Dual buck+4LDO+1POR+On-off

TPS62400

Now

Dual Buck

Now

150mA, superhigh PSRR RF LDO

Now

1A Boost from 3.6V to 5V for USB host and 2W audio

Panel Bias

TPS65120

Buck

LDO

TPS717

Boost

TPS61027

25

Audio Design for GPS

26

Audio Design Highlight

High Volume During Navigation

Audio Performance conflict with RF Design

Small signal layout

Clock jitter

High Performance Act as Media Player

Spk: Mono, H/P: stereo

27

Audio Codec : TLV320AIC32

• 14mW stereo 48ksps playback

• Stereo DAC 8-96ksps 100dB SNR !

Stereo ADC 8-96 ksps 92dB SNR !

• Programmable digital audio processor

• Six single-ended microphone or line inputs

• Integrated microphone bias, preamp, AGC

• Integrated phase locked loop

• Speaker & cap-free headphone drivers

• Audio interface: I2S, DSP and TDM

Control interface: I2C

• Ultra low power for extended battery run time

• Ultra low noise for excellent audio quality

•

•

•

•

•

•

3D, bass, treble, EQ, and de-emphasis effects

Conversion Rate Change

Seamless interface to electret microphones

No ext crystal required, use 512kHz-50MHz input clks

High integration - fewer external components

Flexible interfaces and ability to multiplex devices

• 5mm x 5mm 32-pin QFN (RHB)

ADC

Single-Ended

Single-Ended

DAC

Volume

Control

Equalizer

Audio Effects

ADC

DAC

3D

Single-Ended

Single-Ended

PLL

Control Bus

Differential

or

Single-Ended

Differential

or

Single-Ended

Headphone

Speaker

Power Supply Voltages

Analog: 2.7 – 3.6V

Digital Core: 1.525 – 1.95V

Digital I/O: 1.1 – 3.6V

Differential

Single-Ended

Mixer

Mic or Line

Inputs

• MP3/PMP/GPS/PDA/Cell phones

Audio Bus

Stereo

Line-outs

Mic or Line

Inputs

• Small footprint, saving board space and cost

28

TSC2101-- Touch Screen Controller & Audio Codec

Key Features

4

4

4

4

4

Temp Msmt

AUX Msmt

Battery

Bias

PGA/AGC

Mono

ADC

Mic (x2)

Headphones

SAR

ADC

SPI Port

4

4

support rates up to over 50ksps

400mW Mono BTL 8 Ω speaker amplifier

40mW Stereo 16Ω headphone amplifiers

with cap-less interface support

Dual Mic Inputs with bias, preamp, AGC

Programmable PLL for flexible audio clock

generation

Programmable digital audio

Bass/Treble/EQ/De-emphasis

On-chip 12-Bit SAR ADC for

Battery/Temp/Aux Measurement

4-Wire Intelligent Touch Screen Controller

TSC2101

Touch

Screen

VCM

Stereo

DAC

CPU

I2S Port

4 98dB Stereo Audio DAC, mono Audio ADC

PLL

8Ω Spkr

Key Differentiators

7 Analog Inputs, 4 Analog Outputs, 3 Amps

H/S Auto

Detect

19 mW Stereo Playback at 48 ksps

48-lead 7x7mm QFN

1ku price - $4.95

29

Audio Power Amp: TPA203xD1

Packaging

4 ~1.5x1.5mm WCSP (YZF) [Pb-Free]

PVDD

Internal

Oscillator

VDD

INPulse

Width

Modulator

Differential

Input

Grain of rice

TPA203xD1

IN+

SHUTDOWN*

VoH-Bridge

Vo+

Bias

Circuitry

PGND

GND

WCSP

(Top view of PCB)

1.8V Low-Voltage Logic

VIH and VIL Levels

Integrated

300KΩ Pull-down Resistor

Features

4

4

4

4

4

4

4

4

4

Benefits

Fixed Gain of: 2V/V, 3V/V, or 4V/V

Only 1 external component required

Fully differential, Filter-Free Class-D amplifier

2.5 W into 4Ω at 5V

Supply Voltage: 2.5 to 5.5 V

~84dB PSRR (estimated #)

~75dB Ksvr at 217Hz (estimated #)

Smallest available packaging option

No input coupling caps required

4

4

4

4

4

4

4

Almost a drop in replacement for TPA2010D1

Longer battery life compared to class-AB

Reduces RF rectification

No LC Filter required

Direct-Connect to battery

4 More power

4 Higher efficiency

Saves board space

Reduces external components

30

HOME

Audio Power Amp: TPA2013D1

R1

1.6 to 5.5V

To Battery

Vdd SW

FB VccOUT VccIN

1nF

CIN

Differential

Input

GPIO

Vout+

ININ+

Vout-

4

4

4

4

4

4

4

4

FERRITE

1nF

Gain

ShutDown Boost

SDZb

ShutDown ClassD

SDZd

GND

PGND

Features

4

FERRITE

TDK

MPZ1002S121

1uF

CIN

Gain (Vcc/GND/float)

4

1uF

22uF

Coilcraft

4.7uH

DO3314-472MX

10uF

4

Packaging

4 ~2.4x2.4mm WCSP (YZH) [Pb-Free]

R2

High Output Power from Low Voltage Supply

1.8W @ 3.6V into 8Ω load

1.6 to 5.5V supply Voltage

90dB KSVR at 217Hz

High Power with High Efficiency ~80%

Combines Parts needed for High Power Solution

Very High PSRR

Standby low power mode

Very small WCSP packaging

Internal gains of 2V/V, 6V/V, and 10V/V

Independent shutdown control for the class D

and boost converter

Benefits

4

4

4

4

4

4

4

4

No extra High Voltage Supply Rail Required

Longer battery life

Fewer silicon component solution

Direct Battery Connect

Lower battery power consumption when idle

No LC filter required

Independent boost converter can drive external

components that require high voltage

Small total solution size (~6.5 x 6.5 mm)

31

HOME

TPA2005D1

1.4W into 8Ω Class-D

RI

Differential

Input

RI

IN-

PWM

Packaging

VDD to Battery

Internal

Oscillator

2.5x2.5mm BGA (GQY) [Pb]

4 2.5x2.5mm BGA (ZQY) [Pb-Free]

4 3x3mm QFN (DRB)

4

CS

HVo+

Bridge

Vo-

IN+

GND

SHUTDOWN

Bias

Circuitry

Filter-Free Class D

Features

4 580 mW into 8Ω at 3.6V

4 Supply Voltage: 2.5 to 5.5 V & ~75dB

4

4

4

4

PSRR

Filter-Free modulation

No input coupling caps

Fully differential amplifier

Pin Pin Compatible to

TPA6204D1(1.7W), TPA6211D1(3.1W)

in QFN

Benefits

4

Longer battery life compared to class-AB

Powers hands-free mode

Direct-Connect to battery

4 More power

4 Even higher efficiency

Saves board space

Only 3 external components

4

Reduces RF rectification

4

4

4

4

32

Audio Power Amp: EMI?

CC

F

ses

s

a

P

CE

d

an

-B

s

s

cla

EMI measured in 3m chamber

1cm speaker wire

5cm power supply wire

8 ohm load

3.6V LiIon battery

500mW output power

Little to no radiation at 1.7GHz and above

33

TSC2003 Touch Screen Controller

4-wire Touch Screen Controller Similar to ADS7846, Only I2C Interface

• I2C Simplifies Processor Interface

providing low cost and small size

• Supports full I2C standards

• Low power consumption

• Direct battery Monitoring

• Ratiometric conversion

eliminates gain & offset errors

• Supports Pressure &

Temperature Measurement

•WinCE Driver

Support!

1S Startup

35

Benefit of 1S Startup

Minimize the risk during reading/writing flash

memory

Minimize the waiting time during on/off

Improve end user experience

Friendly environment for open operation system

Easily install/remove software

Fast operation

No firmware issue

36

关机/开机处理

1. MCU监测到关机信号

切断外围电路供电:GPS, Audio, 屏幕等

数据保持标志位置1

SDRAM进入 Self-refresh模式

主时钟停振(实时时钟保持)

关闭DC-DC,改用LDO供电维持系统运行

开机触发键唤醒

中断处理程序—主振启动,SDRAM进入活动模式

检查数据保持标志位决定是否跳过初始化

是, 距离上次关机4小时以内,开启外围模块供电

1S启动完成

37

1S启动主要开销

维持关机状态下的耗电

CPU漏电

SDRAM耗电

DC-DC或LDO耗电

MCU或RTC耗电

外围I/O漏电

38

主要漏电计算

CPU及外设I/O漏电:100uA

RTC or MCU, 30uA

RAM: 200uA~600uA

LDO/DC-DC

110uA/channel LDO, 3通道约330uA

DC-DC, 16uA~600uA, 2通道,约1200uA

最差合计:2260uA

最佳合计:462uA

电池容量1800mAh, 3.0V后约5%即90mAh, 最佳情况下可以保持

190小时,最差情况下约40小时

39

Thanks for your time !

www.ti.com.cn

40