ADVANCED POWER ELECTRONICS PACKAGING

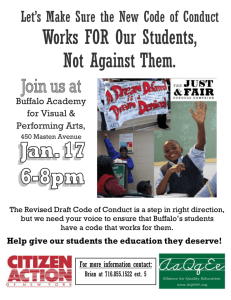

advertisement

Integrated Packaging Techniques Douglas C. Hopkins, Ph.D. Dir., Electronic Power and Energy Research Laboratory Assoc. Dir. Electronic Packaging Laboratory University at Buffalo 332 Bonner Hall Buffalo, NY 14620-1900 607-729-9949, fax: 607-729-7129 www.DCHopkins.Com APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins OUTLINE Part I - Introduction & Housekeeping Part II - Framework • Understanding interdependencies of electrical, thermal and mechanical circuits. Analogs and equivalents • Board to floor packaging of mW to MW, the same technical issues. Part III - Power Electronic Challenges • Understanding parasitic effects • Component and substrate interactions Part IV - Module Packaging • Methods and approaches to power packaging (mW to MW) • Organics (PCBs) to Heavy Metals (bus bars) • Kilo-Volts and Kilo-Amps packaging • Selecting and integrating multiple packaging approaches Part V - Advanced topics • Extended temperature packaging for <250C • High temperature packaging for >250C APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Integrating power on-board and beyond The Point-of-Load Alliance (POLA) was formed by Artesyn, Texas Instruments and Astec Power in June 2003 Full Brick 4.6”X2.3” HB 2.4”X2.28” QB EB 2.28”X1.45” 2.28”X0.8” 84-85 90-91 APEC’09, Washington, DC 94-95 2002 … 05-07 DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Integrating onto Level-0 PSiP - Power Supply in Package PwrSoC - Power Supply on Chip Study by Power Sources Manufacturers Assoc. (PSMA) 25Jan’08 • Phase-I Report - “Market and Technical Report on Power-Supply-in-aPackage and Power-Supply-on-a-Chip” • Phase-II underway at Tyndall, Cork, Ireland APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Int’l Technology Roadmap - Semiconductors: 2006 Low cost/hand held (A) Cost performance (A) High performance (A) Harsh (A) APEC’09, Washington, DC 2.8 101 324 13 3.3 123 406 15 3.3 148 449 15 3.8 184 556 17 4.3 194 583 17 5.0 238 817 18 5.0 238 858 22 DCHopkins@Eng.Buffalo.Edu 5.0 249 800 24 6.0 274 960 28 © 2009, D. C. Hopkins Realizing physical systems - Integrating Energy Processes in the Physical World “If you are not processing information, you are processing power…” APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Comprehensive Packaging Approach The “Energy Packaging Framework” shows that all technical challenges come from managing energy flow along interconnect paths and between packaging levels. Interface & Pathway Packaging Level Energy Form The term “energy” in packaging is used in the broadest context to concurrently include chemical, electrical, mechanical and thermal energies. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins First focus: Energy Forms A physical realization of the system integrates an: Chemical circuit, Electrical circuit, Mechanical circuit, Thermal circuit, etc. I&P “Energy circuits” have: 1.Components 2.Topologies 3.Controls P.L. APEC’09, Washington, DC Energy Forms Advancing one form, impacts, usually negatively, other forms Barriers in one form may be overcome in other forms DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Components for every energy form Form Components Characteristics Electrical R, L, C Transmission Line Mode Lumped/Distributed Para. Resonance Mechanical Mass, Spring, Dash-pot(tension, compression) Resonance (see Acoustics) Air Mass, Material elasticity (vacuum, compression) Acoustic Thermal Mass APEC’09, Washington, DC Resonance? DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Analogies Form Parameters Electrical V, I, [R] Thermal T(temperature), q(heat flow), [R!] R" = R" = V [Volts ] [ ] T oC ! Mechanical (elastic modulus) " (stress), #(strain) E= q[Watts] [ " N m2 ! APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu ! I [ Aamps ] ] # [ m m] © 2009, D. C. Hopkins Pressure, Flow & CTE Symmetric Structure # &( R = "% L $ t •W ' If L = W, then Rsq = " Asymmetric Structure (potato chipping) t APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins ! Levels of Packaging Lvl-0:System - on - Chip • (silicon integration) Lvl-1:Chip -in- package • (component packaging) Lvl-2:Package -on- Board • (board level packaging) Lvl-3:Board -in- Rack • (box level packaging) I&P Packaging Levels APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu E.F. © 2009, D. C. Hopkins PSMA Special Project PSiP2PwrSoC Objective Undertake first detailed study of the evolution in products and technology from Power Supply in Package to Power Supply on Chip (PwrSoC) Scope High-end Consumer Non-isolated 1Watt to 30Watts (30Amps) 6.5m ! 2m! Sync. FET Programme Outline Phase 1: July 2007 to Dec 2007. Phase 2: Mar 2008 to Dec 2008. Phase 2 Sponsorship – 50/50 – PSMA / Member Companies Crane Aerospace & Electronics, Fairchild Semiconductor Corporation. Leader Electronics, Murata Power Solutions, ON Semiconductor Corporation. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins PSiP - Power Supply in Package 2 Number of Components 7 13 25 35 33 Source: PSMA PSIP2PwrSoC Phase 2 Study -2009 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins PSiP - Power Supply in Package Power ASIC + Custom Inductor/Integrated Leadframe Paving the way to PwrSoC 12 x 10 x 1.85mm Source: PSMA PSIP2PwrSoC Phase 2 Study -2009 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins PSiP - Power Supply in Package Paving the way to PwrSoC Power ASIC + Chip Inductor on Leadframe 6 x 4 x 0.85mm Source: PSMA PSIP2PwrSoC Phase 2 Study -2009 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Efficiency Trends for Products PSiP Efficiency Trend 100% 95% 90% 85% 80% 75% 70% 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 2012 2013 2014 Source: PSMA PSIP2PwrSoC Phase 2 Study -2009 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Switching Frequency Trend for Products Switching Frequency Trend 9000 8000 7000 6000 5000 4000 3000 2000 1000 0 2001 2003 2005 2007 2009 Year Introduced Source: PSMA PSIP2PwrSoC Phase 2 Study -2009 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Current Density Trend -+$$"'(%."'/0(1%2$"'* "!!! &%!! &$!! &#!! &"!! &!!! %!! $!! #!! "!! ! "!!" "!!' "!!# "!!( "!!$ "!!) "!!% "!!* "!&! "!&& !"#$%&'($)*+,"* Source: PSMA PSIP2PwrSoC Phase 2 Study -2009 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Switching Frequency vs. Current Density PSiP 9000 8000 7000 6000 5000 4000 3000 2000 1000 0 0 500 1000 1500 Current Density (A/in2) Source: PSMA PSIP2PwrSoC Phase 2 Study -2009 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Level 1 and 1.5 Power ASIC chip on board with wire bonding Level 1: Component(s) in Package. (Module) Level 1.5: Chip on Board PQFN 3x3 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Level 2 Level 2: Package on Board STANDARD SIPS 5/12V INPUT; 5A, 10A, 15A APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Level 3 Level 3: Board in Rack 1600W Front-ends 4.8kW shelf APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Levels 4-5... Level 4: Rack in Cabinet. Level 5: Multiple Cabinets (in room) 6: Room in building 7: Building in community APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Addressing multiple packaging levels Level-2: Board-level or “floorlevel” packaging have common physics of gradients, e.g. high voltage field gradients across air, ceramic or organic dielectrics. Level-1: Component in Package Single components or Mutichip power modules Level-2: Package on Board APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins The technical driver - Energy Flow All technical issues are found at the “interfaces” and in the “pathways” of ENERGY flow Interfaces & Pathways Any technical issue is subdivided into the four+ energy forms Mapping technologies to address an issue in one energy form impacts (usually negatively) the other energy forms E.F. •(e.g. higher temperature solders are more brittle and induce greater stress.) P.L. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Levels of Packaging - Strategy Each level has Components and Topologies. Strategy - combine levels downward for • Decreased: cost, thermal resistance, stress • Increased: density, reliability, manufacturability Module vs Partition Modularization is subdividing circuit functionality for repeated use in multiple products. Circuit Partitioning is subdividing circuit fabrication along packaging levels to improve manufacturability. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins ‘Interfaces and Pathways’ (I&P) All technical issues are reduced to I&P Interface issues occur for energy transfer between levels, Pathway issues occur for energy transfer within a level. Allows concurrent investigation of all concerns APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins I&P at the interface Example: Interface (between levels) for Level-2 (package on board) I&P ISSUES Electrical solder impedance of components Magnetic proximity of components Mechanical Thermal component adhesion heatsink attach APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Grouping Requirements Characteristic Unspoken Expectations Articulated Needs Unexpected Features Taxonomy Technical Environmental Financial Legal Social APEC’09, Washington, DC MATRIXED DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Leading to specifications Taxonomies Characteristics Technical Characteristics Energy Forms Conditions Start-up Shut-down Normal operation Fault operation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Understanding the Power Electronics Challenge second - The physical circuit APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Typical Electrical Structure Lead Inductance Finite resistance Skin Effect Inter-Conductor Capacitance Coupled Capacitance APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Conductor Resistance -Sheet Resistance l R= " l / (t ! w) t w l let l / w = 1 = “one square” Rsheet = " / t [ ! / sq. ] A corner is 0.559 squares APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Conductor Thickness “1 oz. copper” is weight for one square foot Thickness and Resistance from Common Conductors APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins DC Power Supply Example Calculate voltage drop and power loss of the output leads for a “cost performance” supply, i.e. 1V, 100A. Consider 3oz. copper conductors. No. of squares for both sides is: Squares = 2(1 + 0.56 + 0.56 + 0.22) = 4.68 sq. For 2oz. copper Rtotal =(0.168 m!/sq) (4.68 sq) =0.786 m! Vleads = (0.786 m!) (100 #) = 78.6mV or 7.86% (8%) Pleads = (0.786 m!) (100 A) 2 = 7.86 W APEC’09, Washington, DC Terminal ~1 0.56 0.56 Cap DCHopkins@Eng.Buffalo.Edu ~.22 0.56 ~1 0.56 Terminal © 2009, D. C. Hopkins Conductor Resistance -Sheet Resistance l R= " l / (t ! w) t w l let l / w = 1 = “one square” Rsheet = " / t [ ! / sq. ] A corner is 0.559 squares APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins DC resistance in interconnects Topology 1 Topology 2 &'(")*$"+,- &'(")*$"+,- Topology 3 Topology 4 &'(")*$"+,- &'(")*$"+,- !"#$% “0.2 mm” “0.5 mm” 0.5 mm dia 1.0 mm 0.2 mm dia 1.0mm 1.0 mm “4 x 0.2 mm” 1.0mm 0.1 mm ct r “2 x 0.2 mm” 0. 4 m m 1.0mm APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Straight-line with spacers &'(")*$"+,- &'(")*$"+,- er ac er sp 0 .5 mm sp mm 0 .3 0 .2 0 .1 mm ac sp mm ac sp er ac er !"#$% APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Corners &'(")*$"+,- Topology 2 Topology 4 &'(")*$"+,- APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Topologies and spacers &'(")*$"+,- &'(")*$"+,- &'(")*$"+,- &'(")*$"+,- Topology 4 Topology 3 Topology 2 Topology 1 !"#$% APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins AC Conductor Resistance Re ( ! / sq ) = 1.3 R$ %r R$ = ( 2 & $ ) -1 %r = ( sinh ' + sin ' ) / (cosh ' - cos ' ) '=t/$ t is the thickness (m) $ = ( ( f µ & ))1/ 2, skin depth & is conductivity in (s/m), f is frequency µ is permeability ( µ0 = 4 ( x 10-7 H/m) This includes worst-case proximity effects, edge effects and conductor thickness nearly equivalent to skin depth. Optimum t at t = ( $ APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins High Frequency Supply Resistance Calculate the per-square resistance of a 1oz, 2oz and 3oz copper lead needing to conduct a 1 MHz signal. For 1oz copper: $ = 66.0 µm ' = t / $ = 0.516 R$ = 0.130 m! / sq %" = 3.8 1oz 0.6559 0.504 23% 80% Re (mOhm/sq) Rdc (mOhms/sq) % Rdc error % R! error 2oz 0.3299 0.252 24% 60% 3oz 0.2255 0.168 25% 42% Re = 1.3 (130µ! / sq) 3.8 = 0.656 m! / sq Rdc = 0.504 m! / sq or 23% less APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Capacitive Effects © 2009, D. C. Hopkins A Capacitance per square area Conductor (Top) C = "0 "r A / d " = 8.84 x 10-15 F/mm d Insulator Conductor (Bottom) Inter-conductor capacitance? …Negligible l Example: l = 25 mm (100mils) t = 24 µm (1.34mils) d = 254 µm (10mils) t C = 0.030 pF d (scope probe is 10pF) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Coupled Capacitance Substrate Coupling Example Conductor #1: 100mils x 1 inch Conductor #2: 400mils x 1 inch Substrate: ceramic loaded polymer, 3 mils thick, *r = 6.4 Find Capacitance: C1 = 47.9 pF, C2 = 192 pF Total C = C1 in series with C2 Then, C = 38.3 pF APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Ground Coupling Example - Switching current coupled into header from FET drain. FET: 400 mils2, tf = 20 ns Vd (+20 mil conductor periphery) (+100 mils2 drain bond pad) (+200 mils x 400 mils drain lead) Substrate: Al2O3 , 25 mils thick, *r = 9.4 Voltage source: 425 Vdc continued APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Ground Coupling (continued) Find Capacitance: Bond Pad 100mils2 A = 0.284 in2 = 183 mm2 d = 25 mils = 0.635 mm 20mils + C = 24 pF (d-s Cap) 400mils2 Find switching current: i = C (dV/dt ) = 24 pF (425/20ns) Drain Lead 100x200mils i = 0.51 A For ceramic loaded polymer C = 136 pF and i = 2.9 A APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Inductive Effects (Conductor Types) Design Aspects for Inverters with IGBT High Power Modules Dr.-Ing. Th. Schütze, eupec GmbH & Co KG, Warstein, Germany APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Inductive Effects Non-Transmission Line Mode Self Inductance of Conductors Minimum is non-coupled in free space Xe ( ! / sq ) = L$ %l L$ = R$ = ( 2 & $ )-1 %l = (sinh ' ) sin ' ) / ( cosh ' ) cos ' ) '=t/$ t is the thickness (m) $ = ( ( f µ & ))1/ 2, skin depth & is conductivity in (s/m) f is frequency µ is permeability ( µ0 = 4 ( x 10-7 H/m) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Inductive Effects Example - High Frequency Lead Inductance Calculate the per-square self-inductance of a 1oz, 2oz and 3oz copper lead needing to conduct a 1MHz signal. For 1oz copper: $ = 66.0 µm, ' = t / $ = 0.516 L$ = 0.130 m! / sq, %l = 0.172 Xe = 22.4 µ! / sq, or Le = 3.57 pF / sq Note: max selfinductance = Self-Inductance, Cu @ 1MHz ( 4( f& / µ ) -1 / 2 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Inductive Loops Non-ferrous headers • • • • Aluminum Copper Si C Al Si C Ferrous headers / substrates • • • • Invar ( 64% iron, 36% nickel ) Kovar ( 54% iron, 29% nickel, 16% cobalt) Ferrite (substrates) Porcelainized steel (substrate) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Inductance of Feedthroughs and Wire bonds - Kovar feedthroughs > 100nH / pin ,Kovar: 53 Fe / 29Ni / 17Co Use Copper cored Pins to reduce inductance - Alloy 52 Feedthroughs APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Wire Bonds Approximately = 1.2 nH / mm, (mm surface length) Usually 99% Al / 1% Si wire Max Current ( length > 40 mils ) Wire Diameter ( mils ) 5 10 15 20 Max Current Max Current (A) 5.4 15 28 42 I = 0.481 d 3 / 2 I [A] d [mils] Round & Ribbon Wire Bonding APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Voltage Isolation Typical Breakdown Voltage Guidelines: Material Package Glass Al2O3 AlN BeO Thick Film Cer-polymer CVD Diamond Cond-Cond APEC’09, Washington, DC V / mil 200 600 600 770 700 1100 8750 50 kV / mm 7.87 23.6 23.6 30.3 27.6 43 344 1.97 Thickness (mils) 10 25 25 25 1 to 2 6 >10 DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Plethora of choices To Name a few…. Molded interconnect devices Laminated bus bar Insulated metal substrate Direct bonded copper Plated copper 3-D Packaging Direct bonded aluminum Aluminum Composite Heavy-metal PWB others… APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Metalized Substrate Attributes Substrate Plated Copper Direct Bond Thick Film IMS PWB Flex APEC’09, Washington, DC Thickness Total R- Resolution (µm) (°C/W) (µm) 25-127 127-508 15-50 34-140 15-100 15-75 0.2-1 0.2-1 0.5-1 3.2 0.2-1.7 - DCHopkins@Eng.Buffalo.Edu 50-100 250-500 125-250 100-500 100-250 50-100 © 2009, D. C. Hopkins Approaches to Module Packaging Thick-Film Ceramic APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins 3-D Module Design Card-mounted power supply with contact cooling along a narrow 20mm (O.8in.) edge The circuit has three boards: transistor drivers, interconnection and power Power board designed to the 20mm edge height for contact cooling Two other boards connect at right angles to the power board Uses posts on power board to accept heavy-wire bonds from orthogonal boards For an aircraft supply application. “Development of a Three Dimensional Power Circuit Package for Aircraft Applications” ISHM ’94 Proceedings APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins 3-D Package APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Approaches to Module Packaging Molded Interconnect Devices APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Molded Interconnect Devices (MID) MID began in mid ‘80s with “molded circuit boards.” today they are defined as injection-molded plastic parts that are selectively plated with metal to form circuit patterns. At present the predominantly used processes are: * two-shot injection molding * hot embossing * insert molding * laser structuring (additive and subtractive) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Molded Interconnect Devices (MID) Method of Processing A high temperature plastic or polymer structure hosting electrical interconnects is fabricated by 1-shot, 2-shot or insert molding. The interconnections are formed by hot-stamping copper foil, imaging and metal plating the polymer, or insert-molding of structured metal. Electronic Design, Sept 2000 MID lends itself to high volume, 3-D, net shape packaging and is extensively overlooked in the power electronics area (excluding automotive). Components can be surface mounted or through hole with moderate to course line resolution. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Approaches to Module Packaging Laminated Bus Bar APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Laminated Bus-Bar A polymer, such as epoxy, glues together thick conductor bars while providing electrical isolation. The bars can be free-floating laminated interconnects or, if sufficiently thick, be the metal carrier. Vias between layers are metal posts or fasteners placed through drilled or stamped holes. These are used in high current systems and can accommodate very large components. APEC’09, Washington, DC ABS brake component 3 conductor, 2 layer bus bar week production DCHopkins@Eng.Buffalo.Edu 5,000 / With permission from Eldre Corporation © 2009, D. C. Hopkins EUPEC Power Module Design Aspects for Inverters with IGBT High Power Modules Dr.-Ing. Th. Schütze, eupec GmbH & Co KG, Warstein, Germany APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Bus Bar - Electric Vehicle Electric Vehicle Bus Bars Coil for an inductive charging system Mylar insulation with glass (FR-4) reinforced Hipot tested under water With permission from Eldre Corporation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Bus Bar - Electric Vehicle 2nd generation inverter design Laminated Construction With permission from Eldre Corporation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Power Module Interconnect Design Aspects for Inverters with IGBT High Power Modules Dr.-Ing. Th. Schütze, eupec GmbH & Co KG, Warstein, Germany APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Bus Bar - Electric Vehicle Electric boost for turbo Open design - no outside insulation Capacitors soldered directly to the bus Designed for high volume production With permission from Eldre Corporation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Bus Bar - Electric Vehicle Electric Vehicle MOSFET motor drive using low inductance PC board mounted bus bars. With permission from Eldre Corporation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Bus Bar - Electric Vehicle MOSFET inverter 28VDC to 3ph AC 1000 Amp peak Designed for 1000/week production With permission from Eldre Corporation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Approaches to Module Packaging Insulated Metal Substrate APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Insulated Metal Substrate (IMS) IMS - polymer on metal (IMS-PM) - A polymer is used to isolate and attach a conductive interconnect to a metal plate which provides mechanical support. Vias can be placed between the interconnect and plate and a layer of polymer and interconnect can be attached to the interconnect layer. IMS - steel corded (IMS-PS) - High temperature glass (~900°C) coats a steel plate and a thick-film conductive cermet interconnect is applied on the glass. The structure is similar to traditional thick-film. Vias are in multilayer thick-film. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins IMS Poly- Apps in Power With permission from The Bergquist Company APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins IMS - Polymer Insulation Surface texture: “ED” foil or Bond treatment 35,70,100,140, 210, 280 & 350 #m (1 oz - 10 oz) 75 - 150 #m (3 mil - 6 mil) Special base metal AL & CU .5mm - 3.2mm (.020 - .125”) “Surface Treatment” • Built-in heat spreader • High performance “PWB” for SMT • Easily drilled and clamped • Multilayer capability • Screen printed polymer resistors With permission from The Bergquist Company APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Insulated Metal Substrate Attributes * 100µm conductor separation * *r = 6.4 or 74 pf/cm2 * " = 1.72µ! cm copper 34µm - 140µm thickness 506µm - 123µ!/sq * R- = 0.29 °C/W/cm2, 1mm Al plate * Utilizes SMT technology * Integrated baseplate * Easier test and rework APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins IMS - Laminated Two Layer Circuit layer pair and Bond Ply Laminated Two Layer Construction Thermal Via’s Circuit Pair: 1 oz - 6 oz “Outer” 1 oz - 2 oz “Inner” Dielectric 6 mil/6 mil Base choice: AL & CU .040 - .125” With permission from The Bergquist Company APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins IMS- FR4 & Bond Ply FR4 and Dielectric Laminate (BOND PLY II) (FR4 typical Tg = 130°C and Bond-Ply II “UL” 140°C) Circuit Pair: 1 oz - 2 oz + 1 oz plating “Outer” 5 mil - 12 mil -- FR4 1 oz - 2 oz + 1 oz plating “Inner” Electrical via’s (Shield-Layer) Thermal via’s improve conduction Dielectric: 5 mil – Bond-Ply II Base choice: Al & Cu, .032 - .062” With permission from The Bergquist Company APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Example IMS - Poly, Circuit With permission from The Bergquist Company APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Example IMS - Poly, Circuit With permission from The Bergquist Company APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Approaches to Module Packaging Glass Epoxy (FR-4) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Glass-Epoxy (PTH and SMT) Glass-Epoxy with plated through holes (FR-4, PTH) - A fiberglass mesh is impregnated with epoxy and metalized with copper. Interconnect patterns are etched into the foil. The patterned copper clad mesh can be laminated and vias formed by drilled and plated holes. Leaded components are attached by soldering leads that have been placed through holes. Glass-Epoxy with surface mount pads (FR-4, SMT) - Same as above except chip components are solder attached. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Approaches to Module Packaging Plated Copper on Ceramic APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Plated Copper - Apps in Power Magnetics & ignition module With permission from CirQon Technologies Corp. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Plated Copper Attributes Chips * 50µm conductor separation * *r = 9.4 or 13 pF/cm2 Solder * " = 1.72µ!-cm Copper 25µm - 127µm thickness 690µ!/sq - 135µ!/swq. * R- = 2°C/W/cm2 (*) * Chip & Wire or SMT * Some thermal interaction * Ceramic based - mixed technology photo-patterned and plated; thick or thick-film * Accommodates highly complex circuits APEC’09, Washington, DC Cu Thick-film Resistor Cu Al2O3 Cu Cu DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Plated Cu - Typical requirements •Ceramic typically 96% Alumina •Preferred panel and substrate sizes: 7” x 5” @ 25mils 4.5” x 4.5” @ 15mils 2” x 2” @ 10mils •Typical copper plating thickness: Minimum .001” +/- .0003” , Maximum .003” +/- .001” Perforations needed in copper patterns > .250” square. Surface finish preparations typically Wirebondable Au with Ni diffusion barrier – requires design review. Immersion Au (3-5 microinches) with Ni diffusion barrier. Entek OSP over bare copper to promote solderability. Immersion Ag (3-5 microinches) to promote solderability APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Plated - Line resolution Trace widths, spaces and tolerances: •for copper thickness of 1mil to 2 mil minimum trace width .003” +/- .0005” minimum space width .003” •for copper thickness of >2mil minimum trace width .004” +/- .0015” minimum space width .004” With permission from CirQon Technologies Corp. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Plated Copper via fill Typical minimum Via size is .008” in 15 to 25mil ceramic. With permission from CirQon Technologies Corp. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Approaches to Module Packaging Direct Bonded Copper APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Direct Bond Copper Attributes * 500µm conductor separation * *r = 6.8 or 9.5 pF/cm2 * " = 1.72µ!-cm Copper 1.27µm - 508µm thickness 135µ!/sq - 34µ!/swq. * R- = 0.22°C/W/cm2 (*) * Chip & Wire or SMT * Minimal thermal interactions * Ceramic based approach using additive techniques * Expensive, difficult re-work APEC’09, Washington, DC Chip solder Cu BeO Kovar DCHopkins@Eng.Buffalo.Edu solder © 2009, D. C. Hopkins DBC Interconnect and Patterns Courtesy of Dynamic Hybrids Incorporated APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Direct Bonded Copper CLICK HERE APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Approaches to Module Packaging Molded Interconnect Devices APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Under Development HDI - High Density Interconnect, uses polyimide patterns overlaid on power chips embedded in cavities. MPIPPS - Metal Post Interconnect Parrallel Plate Structure, combines butt connected posts for interconnect and mechanical support of multiple layers. Ultra Thick-Film - thick film reapplied to fired thickness >508um. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Thermally Conductive Polymers CLICK HERE Courtesy of Cool Shield Inc. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Optimally Selecting Packaging Technologies and Circuit Partitions Based on Cost and Performance Presented: APEC’ 2000 Plenary Session John B. Jacobsen and Douglas C. Hopkins APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Depreciation Production Cost Standard unit cost Wages Materials Cost APEC’09, Washington, DC Packaging materials Comp. packaging (controllable) Other OH Packaging Materials & Production Costs Overhead Full-Cost Model Minimum packaged components DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Production Cost Dependency by Volume 700% Production Cost 600% 500% Other overhead costs 400% 300% Depreciation 200% 100% Wages 0% 10k 32k 100k 320k 1000k Products/Year APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Cost Variation Within a Technology Packaging & Production Costs 110 SMDs 14 leadet FR4 Ch to ang ch ing an te ge ch de no ns lo ity gy Relative Cost TF module & leadframe Packaging Performance: (electrical, thermal, mechanical 1 0.8 0.6 0.4 Functional integration within technology 70 SMDs 7 leadet 0 5 10 15 20 25 0.2 0 30 Surface Density APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Relative Cost of Technologies Packaging & Production Costs Packaging Performance: electrical, thermal, mechanical 1 DBC TF & Plated Cu Performance Relative Cost IMS Circuit cost by change in technology FR4 0.8 0.6 0.4 0.2 Hot Embossing 0 5 10 15 20 25 0 30 Surface Density APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Relative Packaging & Production Cost Relative to 1 in2 of FR4 14 a b 10 8 c 6 4 d Z-strate Cu( 2 layer) IMS (1 layer on Al) FR4 Cu( 4 layer ) FR4 Cu( 2x35um) Hot Embossing 0 DBC( 0,63 Al2O3 ) d a b c d leaded auto/10 comp Substr/in2 Power chip& wire/10 comp SMD/10 comp Integrated res/10 comp TF multilayer 2 TTF Relative Cost 12 Substrate Technology APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Relative Production Cost per Technology 120% Cost/component 100% 80% 60% 40% 20% 0% Leaded-manual Leaded-auto Power chip & wire SMD-auto Assembly Technology APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins X2100S-User Requirements (constraints) Several requirements place specific constraints on packaging the 2.2 kW drive: • Mechanical: Built into stainless steel tube with a diameter of 65mm and as short as possible. • Thermal: Cooling through tube with non-flow of water at 30°C. • Environment: Potting complete electronics inside tube not allowed. • Regulatory: UL, CE • Reliability: 1.000.000 quick start/stop • 30.000 max gradient start/stop • 40.000 h lifetime @ 10°C water APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Electronics Block Characterization-MtrDr EMC Rectifier •1 coil 10W •5 dies •10 X,Y,pulse-caps •3 VDR •1 Resistor 20W VDE/inrush •1 •1 •1 •4 •8 •1 dies 15W shunt 2W IC SMD Resistors VDR PFC •2 •1 •1 •1 •8 •12 •1 dies 23W shunt 2W IC diodes SMD Resistors coil 15W X2100S module •DC link •1 Voltagedevider •2 Capacitors 7W INVERTER •12 dies 102W •1 shunt 2,5W •1 HVIC •13 diodes •13 SMD •23 Resistors L1 EMC L2 Rectifier PFC DC link A B C Inverter VDE inrush Line communication Motor control uP B-EMF Power supply Colur code Blue = leadet Green = SMD/die/TF Red = powerloss >1W APEC’09, Washington, DC Line communication •1 coil 5W •1 IC !W •27 SMD Power suply •1 Transformer !W •4 Capacitors •1 IC 1W •9 SMD DCHopkins@Eng.Buffalo.Edu Motor control-uP •3 IC •12 SMD BEMF •2 IC •3 SMD •36 Resistors © 2009, D. C. Hopkins Motor Drive Packaging Technology Technology characteristics @ typical strongest version for motor drive APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Component Characterization Map Functional Function Comp Qty block Mechanical Delivery form/ Size carrier Electrical Voltage Current V EMC Filter Y-cap Filter X-cap Choke inductor Filter X-cap Transient clamp VDR Rectifier Inrush/ VDE PFC 2 2 leaded leaded 13x5x10 26x10x18 300 ac 300 ac 1 1 leaded leaded ø37x20 17x6x12 300 ac 300 ac 3 leaded ø21x5 300 ac 2 2 1 1 leaded 18x9x15 leaded 12x8x10 leaded ø4x10 leaded 31x18x28 Constraint/remarks A/ comp Thermal Power loss Max temp Rth W/comp degC K/W 10 105 125 low L to earth low L to L1-L2 11 rms low L to earth 1 low L to L1-L2 2 low L to L-Earth low L to earth Filter Y-cap Filter Pulse Bridge Y-cap Resistor MKT Diode 4 die 3,5x2,5 600 11 rms Clamp Switch Diode IGBT 4 1 die die 3,5x2,5 6x4,3 600 1,200 5 <1 11 rms 15 Cur. sense Shunt Controller Support 1 1 4 TF die Transient clamp IC C R VDR Switch Freewheel Cur. sense MOS Diode Shunt Controller Suport IC C R L Choke APEC’09, Washington, DC 300 ac 300 ac low L to earth 300 ac Close to DCP-DCN 2 11 rms <18 SMD TF 0603->B 8 3 1 leaded die ø21x5 7,5x7,5 300 ac 500 1 die 3x4 500 1 1 8 12 1 TF die SMD TF leaded <1 note1 125 16 125 Low L DCN-PGND 26 peak 11 rms 10 m 0603->B 125 125 7 125 2 note1 <1 125 < 70V 500 11 rms DCHopkins@Eng.Buffalo.Edu 15 130 © 2009, D. C. Hopkins Component Characterization Map (con’d) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins X2100S final design Uses: MID DBC Thick film SMT Return to main talk APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Advanced High-Performance Packaging Structures Thermal Impedance and Stress in a Power Package Due to Variations in Layer Thickness Acknowledgments: J. M. Pitarresi and J. A. Karker APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Objective: • Investigate electro–physical design issues – Electrical Performance • Current capacity of interconnects • Capacitive coupling – Physical Performance • Thermal conductance • Thermally induced stress APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Direct Attached Ceramic on AlSiC Ceramic on AlSiC Layer TCE Modulus IGBT Solder attach Cu Ceramic AlSiC Header Thickness Is Variable Al interface AlSiC Cu Density 7.2 226 2.94 17.3 126 8.96 Conventional Package Process: 1. DBC on ceramic 2. During Al impregnation of SiC (-600°C) the ceramic wets and is attached. Cu anneals. 3. IGBT is attached. APEC’09, Washington, DC Cu Header Heat Sink Grease interface DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins AlSiC Replacement Maintain same plate bending rigidity: Thickness: . = tAlSiC / to Weight: / = wAlSiC / wo Thermal Resist.: 0 = R-,AlSiC / R-,o APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Thermal Spreading Temperature Difference (°C) • Previous Work IGBT@70W/cm2 DBC – 635#m (25mils) Ceramic – Vary Cu thickness 24 22 20 18 16 14 12 10 8 6 No Metalization 127!m (0.005in.) 254!m (0.010in.) 508mm (0.020in.) • Results 0 40 80 120 160 200 240 280 – Optimum Cu thickness on Al2O3 (of 285#m). Thermal Conductivity (W/m°C) – Increasing Cu thickness increases thermal conductance on BeO, AlN APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Physical Performance • Module Structure half symmetry Solder attach IGBT Cu Ceramic AlSiC Header APEC’09, Washington, DC • Variables: copper thickness: 75–510#m ceramic thickness: 75–635#m ceramic type: Al2O3, AlN, BeO AlSiC: 1.3–6.4mm Al interface Layer Silicon 63Sn/37Pb Copper Ceramic Al (356) AlSiC Adhesive Baseplate DCHopkins@Eng.Buffalo.Edu Thickness (#m) 350 101 75-510 75-635 51 1. 3-6. 4mm 51 13. 2mm Width/2 (mm) 5. 1 5.59 6. 6 7. 1 17. 1 18. 4 8. 4 10. 9 © 2009, D. C. Hopkins Finite Element Analysis • Dual models: thermal and stress, with 8-node solid elements • Meshed for < 5% error • IGBT with 200W/cm2 • 25°C thermal ground • 125°C max at IGBT • Linear model with no prestress. APEC’09, Washington, DC • Cases Studied Layer Thickness Ceramic Copper varied 203#m Case I varied Case II 76#m Case III 254#m 203#m AlSiC 635#m 635#m varied • Stress bounds: Copper 192 MPa (equivalent stress) Ceramic 264 MPa (tensile principle) Silicon 128 MPa (tensile principle) DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Results - optimum thickness • Special Case Copper 200 varied – Example of thickness extremum that maximizes stress. Similar to optimum thickness for thermal conductance. APEC’09, Washington, DC SPECIAL* – Copper 160 Stress (MPa) Ceramic AlSiC 0.5mm 635#m BeO Cu layer *BeO -0.5mm AlSiC-2.5mm 120 80 BeO layer 40 Si layer 0 0 DCHopkins@Eng.Buffalo.Edu 200 400 Cu Thickness (#m) 600 © 2009, D. C. Hopkins Results - variable ceramic thickness 160 • Case I – Stress Copper 203#m BeO Ceramic is used 160 Cu layer 120 Stress (MPa) 120 Stress (MPa) Ceramic AlSiC varied 635#m Al2O3 Ceramic is used Cu layer Si layer 80 40 0 Al2O3 layer 0 200 400 Al2O3 Thickness (#m) 80 BeO layer 40 0 Si layer 0 200 400 600 BeO Thickness (#m) APEC’09, Washington, DC 600 • Si on BeO has lower stress due to lower $T°. • Thinner ceramic has higher stress for this Cu thickness. DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Results - variable copper thickness • Case II – Stress Ceramic AlSiC 76#m 160 Copper 120 Stress (MPa) varied 635#m BeO Ceramic is used 160 Stress (MPa) 120 Cu layer Si layer 40 0 200 400 Cu Thickness (#m) APEC’09, Washington, DC 600 Cu layer 80 Al2O3 layer Si layer 40 0 BeO layer 80 0 Al2O3 Ceramic is used 0 200 400 Cu Thickness (#m) 600 • Thinner copper relieves the stress in the ceramic and Si. • Thinner Cu has higher stress. DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Results - variable AlSiC thickness Al2O3 Ceramic is used 160 Ceramic AlSiC 254#m varied Cu layer 120 Stress (MPa) 203#m BeO Ceramic is used 160 80 Cu layer 120 80 Si layer 40 Al2O3 layer 0 0 0.5 1 1.5 2 AlSiC Thickness (mm) 2.5 • Extremums in both Si and Al2O3 are observed. BeO layer • The matched TCE of AlSiC and ceramic minimizes the ceramic and Si stress. 0.5 1 1.5 2 2.5 AlSiC Thickness (mm) • Cu reacts to TCE mismatch. Si layer 40 0 Copper Stress (MPa) • Case III – Stress 0 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Summary • Direct–attached–ceramic on AlSiC reduces the number of package layers – reducing the thermal impedance and stress. The TCE of AlSiC is 7.2 and ceramic is 5.8 to 7.4. • FEM analysis used to evaluate thermal conductance and thermally induced stress for various Cu, ceramic and AlSiC layer thicknesses. • Generally, thinner layers provide less stress due to lower thermal gradients. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins End - Advanced High-Performance Packaging Structures Return to Energy Forms Additional information and Updates available at www.DCHopkins.Com or email at APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Aluminum-Based High-Temperature (>200°C) Packaging for SiC Power Converters Dr. D. Hopkins*, D. Kellerman, Dr. C. Basaran*, Dr. J. Gomez* *University at Buffalo State University of New York APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins System Requirements Target Parameters for 60kW, 3ph actuator drives • Electrical: 900VDC, 137A • Ambient >200C • Max junction temperature: 350°C • Year of final design - 2009 Trade-off Analysis for • Power level v. temperature v. device maturity (2005-2009) • IMAX v. temperature • Number of devices per module • (6 modules per three phase bridge) MOOG 6DOF25000E Flight Simulator Platform APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Challenge Higher Density Converters means • Fewer, Smaller and Closer components, • i.e. higher thermal densities Advantages of SiC power devices: • high temperature (>350°C) and wide temperature • high frequency Challenge is in the GRADIENTS • Higher electrical gradients • Higher thermal gradients • Higher stress gradients Design Challenge • Trade-off of materials for electrical/mechanical/thermal performance • Applied to Level-I module design, Level-II (box) frame design • Reliability management of dissimilar materials APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Methodology Minimize interfacial discontinuities Manage CTE mismatch with compliant materials Conclusion – Move towards a mono-material system Best candidate: Aluminum-based system • • • • • Aluminum metalized SiC die Aluminum conductors Aluminum oxide insulators Aluminum nitride substrate Aluminum Silicon Carbide baseplate APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Electrical Design SiC Devices - Selection and Modeling APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Optimum Number of Chips Selected Power JFET with Al metalization • Used the system-level functions for “normally-on” safety Optimization of power level v. temperature v. device maturity Results: 10 chips per module • Dissipation: per chip- (350C) • 25.2 W, module- 252 W, • Inverter – 1.7kW • 2005 design is 40kW, • 2009 is 60kW Inverter efficiency – 97.2% Small electrical penalty for operating at higher temperatures, but with significant gain in density APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Physical System Design Level – I Power Module APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Micro-Packaging Materials Focus: Mono-Material Approach Conformal Coating (1) Aluminum Wirebond – (Al to Al) SiC Chip Die Attach (2) Metal traces (3) Metalized AlN Ceramic (4) AlSiC Heat sink (4) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (1) Conformal Coating Material Cotronics 920 • • • • • • • • • • Alumina Refractory Cement Coating Material Used for wirewound power resistors, heaters Paste, Room Temperature cure Alumina ceramic properties: no outgas, inert, etc. Service Temp: 1634°C CTE: 4.5 ppm/°C Dielectric Strength: 270 V/mil Volume Resistivity: 1011 ohm-cm Flexural Strength 450 psi Compressive strength: 3000 psi • Requires conformation for wire bonding APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (2) SiC Die Attach Au solder based • Au/An 80/20 • Au/Sn 88/12 • Au/Ge 88/12 Pb, Ag solder based • • • • Sn/Ag 96.5/3.5 Pb/In/Ag 95/3.5/1.5 Pb/Sn 95/5 Sn/Ag/Sb 65/25/10 Glass-Thermoplastics • (see next slide) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (2) Attach – Au solder based APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (2) Attach – Pb, Ag solder based APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (2) Attach – Glass-Thermoplastics APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (2) Die Attach - Silver Glass Ag/Glass Henkel/Hysol 3555R, 70/30 440°C, Mil Spec (883 et. al.) qualified replacement for Si/Au Eutectic • • • • Void free Low RGA (outgas) Ionics free Used extensively in Microelectronics industry. PLIABLE OVER TEMP APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (2)Die Attach Testing SiC chip to aluminum and SiC chip to AlSiC Henkel/Hysol 3555R Ag/glass 255 (-55°C +125°C) Temp cycles, continued with full adhesion APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (3) Aluminum Conductors Aluminum, on exposure to high heat, suffers from only a modest decrease in inherent strength as seen in the graph for several alloys (fracture strength plotted as a function of temperature). [1] [1] Handbook of Materials for Product Design, Harper, McGraw Hill, 2.85 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins AlSiC Replacement Maintain same plate bending rigidity: Thickness: . = tAlSiC / to Weight: / = wAlSiC / wo Thermal Resist.: 0 = R-,AlSiC / R-,o Replacing Aluminum Copper APEC’09, Washington, DC 0.69 0.75 0.97 0.80 0.26 1.85 DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Plating Aluminum Skin is easier to plate than AlSiC Matrix Plating & Coating Options similar to Aluminum Courtesy of Former PCC-AFT APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins In-situ Joining Integrate heat sink & baseplate Cast-in components (e.g. Metal stand-offs) Ceramic substrate cast into baseplate Courtesy of Former PCC-AFT APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Capabilities Net Shape Parts Aluminum Skin Ni,Au,Ag,Cd etc. Plating Anodizing, Chemical Film Solderability at as high as 400oC Pressure Infiltration Casting Large Plates as Thin as 0.010” (250 µm) Arc Flatness .0012”(.03 mm) Cast-in Metals Cast-in Ceramics Direct Bond Aluminum Cast-in Circuit Pattern Dimensional Control +/- .003” (50 µm) Courtesy of Former PCC-AFT APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (4) Aluminum Nitride Ceramic APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (4) Module Traces and Devices Aluminum traces cast simultaneously on AlN when casting the AlSiC heat sink • Shown is very thick cast-Aluminum pads (traces) of 0.5mm (20 mils) cast onto AlN captured in AlSiC Proposed pattern on ceramic – • SiC devices sit inside pattern • Source leg in center is surrounded by gate pattern • Separate power and g-s bonds • Low inductance wire bonds: Al-to-Al source and gate gate metal source metal Die sit between g-s APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins (4) Ceramic/Heat Sink AlSiC heat sink is cast with the AlN or Al2O3 capturing substrate and sink together EXTREMELY strong AlSiC / Ceramic bond. • Adhesion test showed separation in the ceramic, not at the interface. Circuit Choice – 1. Insolated Circuit – devices mount on metal traces on ceramic. 2. Hot Sink – devices mount to heat sink through holes in ceramic. Selected Approach –Ceramic has holes when cast –Holes are either cast-filled with aluminum or remain empty –SiC devices mount on/in holes •SiC drain connects directly to the heat sink •MAXIMUM electrical and thermal conduction achieved! APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Module Layout on AlSiC – Test plate by PCC-AFT – UB reliability modeling AlSiC base structure • 9.5 x 4.4 x 2.0 cm • 0.25-0.5 mm (10-20 mils) Al skin • 1.5 x 15 mm fins (10:1 aspect) • (finest geometry) Al conductor loss at 350°C – 1% of chip loss/sq (.25mm thick) Al wire bonding to Al conductors SiC Chip Attach • 3 x 3 mm SiC JFETS • Ag-Glass attach • >80W/mK, <15µ!-cm • UB testing and modeling • Electrical connection to AlSiC Al/Ceramic captured into AlSiC • 0.63 mm AlN (Al2O3) • 0.25-0.5 mm Al on AlSiC/Cer. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Non-Optimized Thermal Modeling Dimensions •0.25 mm Al trace •0.63 mm AlN •1.5 X 15 mm fin •1.5 mm fin spacing •1.5 mm AlSiC w/ 0.125 Al Temperature Profile •150 °C ambient air •400 lfm (800 no difference) Temperature Results (w.c.) •20% estimated error •10 °C inner-to-outer DT; 32 °C downstream DT Tmax =(340°C + 32°C) -20% = 297°C (Design Temp = 350°C) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Thermal Profile 4o/div (24o) Worst-Case-Design with SiC devices on top of AlN (not direct to AlSiC) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Stress Distribution Stress distribution in region of chipset along maximum deflection zone. As expected high stresses (close to 800 MPa) are predicted. The large stress value is due mainly to assumed boundary conditions. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Module & Gate Drive Stack-up Thermal Shield • Cotronics 914 glass ceramic • 0.39 W/mK, 1014 W/cm • Machinable • 3 mm / side larger plate • End notched for Drive-Power interconnect • Expensive (seeking substitute) • Lateral cooling channels not shown in drawings • Expensive (seeking substitute) – One drive ckt / 5 SiC chips – Confirmed, components fit driver board see B.O.M. for parts sizes – Traditional thick film hybrid process with SOI for driver. Dual Gate Drive circuit layer • (Substrate 3 mm/side larger than Thermal Shield) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Stack in Frame Gate Drive Board Thermal Shield Frame Electrical isolation of Module from Frame Power Module with SiC devices mounted and interconnected on heart sink APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Physical System Design Level – II (Box) Frame APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Level-II (Box) Frame Design Modules electrically hot Modules sit in Frame • Sit in thick anodized (Al2O3) pads, or can use inserts Air Inlet • Interconnects feed through module ends for gate drive and upper/lower bridge switches Clam-shell design of two frames Air channels into center core and out sides. • Pressurizes center core to give 400 lfm flow • Outer housing pressurized to cool gate drive and 914 material • Hot air exhaust critical to manage APEC’09, Washington, DC Air Outlet Near Optimum design creates linear tunnel flow –20.3 X 29.3 X 1.44 cm 60kW: 70W/cm3 (1.15kW/in3) SiC chips loss is 1.5kW total Gate drive loss is 25W total (Very low gate power is needed) DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins End Aluminum Based Packaging Return to Main Menu APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins REFERENCE APEC’09, Washington, DC Definitions - micron (µm) is 10-6 meters - mil is 0.001 inches or 25.4 µm - Per Square is length to width ratio of 1 - 1 oz. copper is weight per square foot. Copper thickness per ounce is 35µm (1.34mils). APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Conductor/Metal Properties Metal Resistivity (µ!-cm) k (W/m-°K) TCE (ppm/°C) Aluminum Chronmium Copper Gold Invar Kovar Molybdenum Nickel Silicon Silvar (30Ag) Silver Tin Tungsten 80%Au - 20%Sn 95%Pb - 5%Sn 2.83 20 1.7 2.2 46 50 5.2 6.8 5.6 1.6 11.5 5.5 16 19 240 66 393 297 11 17 146 92 84 130 418 63 200 57 63 23 6.3 17 14.2 1.5 5.3 5 13.3 5.6 19.7 4.5 15.9 29 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Insulator/Substrate Properties Substrate *r k (W/m-°K) TCE (ppm/°C) AlN BeO BN Cu-Invar-Cu Diamond (CVD) Epoxy-Glass (x,y) Polyimide SiC Si3N4 96% Al2O3 8.8 6.8 6.5 3.5 3.6 3.5 42 7 9.4 230 240 600 100 400 0.2 0.2 270 30 26 3.3 6.8 3.7 3.0 2.3 6.0 50.0 3.7 2.3 6.6 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Comparative Thermal Resistances - (°C/kW cm2) Material Silicon (Si) Solder (95Pb-5Sn) Molybdenum (Mo) Alumina (Al2O3) Aluminum Nitride (AlN) Beryllia (BeO) Aluminum Silicon Carbide (AlSiC) Aluminum (Al) Copper (Cu) Polymer Ceramic Glass Epoxy (FR-4) Thermal Grease APEC’09, Washington, DC Thermal Typical Conductivity R-/cm2 (W/m °C) (°C/kW cm2) Thickness (mils) 84 63 146 20-26 170-230 42 16 17 244 37 240-320 170 26 - 25 25 - 5.2 - 240 393 3.2 0.2-1.7 1.1 2.6 476 3000 924 4 (3oz) 6 20 4 0.52 95 600 185 DCHopkins@Eng.Buffalo.Edu 14 4 10 25 DT(°C) IGBT @0.2kW/cm2 8.4 8 3.4 49 - © 2009, D. C. Hopkins EXTENDED TOPICS High Temperature Packaging for SiC Converters AlSiC Composites Thermal Vias Amkor Guidlines X-Y Caps Reference Thermal Trace Profiles CoolShield RJR Process APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Power Wire & Ribbon Bonding Reference to: MODEL 20, May 2004 Excerpt with permission from Orthodyne APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins Bond Definitions Bond Pad: electrical surface on an IC or other surface. Bond Length (BL): the length of wire bond making intimate contact with the bond pad. Total Length (TL): the total length of the bond including the tail and bond shadow. Bond Shadow: bond residue at the front and back of the bond where the wire made initial contact with the bond pad before ultrasonic energy was applied. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Bond Definitions (con’d) Tail: the residual piece of wire left on the bond after the bonder cuts and breaks the wire. Step Back: the distance between the first and second bond. Tail Length: the distance the bond head moves back after completing the second bond. Bond Footprint: the total area of the bond on the bond pad. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Guideline Topics Bond Pad Size Minimum Distance • • • • from 1st Bond to an Obstruction. from 2nd Bond to Obstruction - Standard Wire Shifter (30°). from 2nd Bond to Obstruction - Deep Package Wire Shifter (45°). from 2nd Bond to Obstruction - Extended Offset Wire Shifter (45°). Minimum Parallel Distance from an Obstruction. Single Groove Configuration Bond to Package Orientation Work Holder Clearance Height Clearance Distance from Transducer Horn to Front of Machine Step-down Clearance Distance APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Bond Pad Size The minimum bond pad size for attaching a wire bond. Related to the size of the wire being bonded. Minimum Bond Pad Sizes Pad Width(W) Pad Length(L) Wire Size mil/microns mil/microns mil microns 4 100 10/250 14/350 5 125 12.5/312.5 17.5/437 8 200 20/500 28/700 10 250 25/625 35/875 12 300 30/750 42/1050 14 350 35/875 49/1225 15 375 37.5/937 52.5/1312 16 400 40/1000 56/1400 18 450 45/1125 63/1575 20 500 50/1250 70/1750 25 625 62.5/1562.5 87.5/2187 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Bonding Obstructions Minimum Distance From 1st Bond to an Obstruction. Minimum Distance from 2nd Bond to Obstruction - Standard Wire Shifter (30°). Minimum Distance from 2nd Bond to Obstruction - Deep Package Wire Shifter (45°). Minimum Distance from 2nd Bond to Obstruction - Extended Offset Wire Shifter (45°). APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Optimum Bond-to-Package Position Bond pads size requirements effect die location. The orientation of the die is not important if the bond pads are at least three times the wire diameter in any direction. Changing the wire orientation after the first bond can prevent the second bond from forming. Other problems include stresses at the heel of the bond due to rotation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Ex. TO-220 Bonding Orientation The TO-220 is designed for optimum bonding orientation. In Example “A” the bond pads are positioned parallel with a straight setback between 1st and 2nd bond. Example “B” does not use a straight setback design and is a less desirable strategy. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Work Holder Clearance Height Limits height of magnetics, capacitor cans, connectors, etc. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Step-Down Clearance Distance The maximum step-down distance between first and second bond depends on the Capillary feed angle. For 30° Feed Angle: maximum step-down bond height differential distance is 0.10”. For 45° Feed Angle: maximum step-down bond height differential distance is 0.75” to 0.80”. APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins RIBBON (WIRE) BONDING Courtesy of Orthodyne APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Trends in Power Semiconductor Packaging PowerRibbonTM Bonding Advantages • Lower Material Cost • Higher Throughput • Better Electrical Performance • Able to bond on sensitive die • Automotive reliability Disadvantages Electrical Performance not as as Cu Clip bonding APEC’09, Washington, DC good DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins PowerRibbonTM Introduction Wire ! Ribbon Effect of geometry change Increasing power requirements results in larger wire diameter, making bonding thicker wires increasingly more difficult Limitation of bondable round wire is 20 … 25 mils diameter Seek to de-couple thickness and width, keeping thickness limited (in a first step) APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins PowerRibbonTM Introduction Wire to Ribbon Conversion Table shows number of round wires with equal electrical resistance to ribbon, at equal loop length (example: 1- 60x8mil ribbon replaces 4.2- 12mil wires) Al 20x3 30x3 40x4 60x4 60x6 60x8 80x8 80x10 2 3 19.1 8.5 28.6 12.7 50.9 22.6 76.4 34.0 114.6 50.9 152.8 67.9 203.7 90.5 254.6 113.2 4 4.8 7.2 12.7 19.1 28.6 38.2 50.9 63.7 wire diameter [mils] Au 2 3 20x3 15.0 6.7 30x3 22.5 10.0 40x4 40.0 17.8 60x4 60.0 26.7 60x6 90.0 40.0 5 3.1 4.6 8.1 12.2 18.3 24.4 32.6 40.7 6 2.1 3.2 5.7 8.5 12.7 17.0 22.6 28.3 wire diameter [mils] 8 10 12 1.2 1.8 1.1 3.2 2.0 1.4 4.8 3.1 2.1 7.2 4.6 3.2 9.5 6.1 4.2 12.7 8.1 5.7 15.9 10.2 7.1 14 15 16 20 25 1.0 1.6 2.3 3.1 4.2 5.2 1.4 2.0 2.7 3.6 4.5 1.2 1.8 2.4 3.2 4.0 1.1 1.5 2.0 2.5 1.0 1.3 1.6 Cu 20x3 30x3 40x4 60x4 60x6 2 11.9 17.9 31.8 47.7 71.6 wire diam eter [mils] 3 4 5 5.3 3.0 1.9 8.0 4.5 2.9 14.1 8.0 5.1 21.2 11.9 7.6 31.8 17.9 11.5 6 1.3 2.0 3.5 5.3 8.0 APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Al Cu Au " [µ!)cm] 4.3 1.75 2.2 Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Small Power Packages Design Considerations Small Power Packages Higher die-to-package footprint Lower die-free-package resistance (0.5m$ for standard power SO8) Shorter Loops Thinner package PQFN 3x3 PQFN 5x6 APEC’09, Washington, DC Design And Process Considerations • Works with all different Die Attach methods • Lead Finish (Cu, Ni, NiPd-Au), Ag) • Stitch Bonds • Forced angle bonding DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Package Design and Process Considerations Bonding Capabilities Forced Angles Stitch Bonds APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Performance/Reliability/Cost Mech/Chem Performance (Reliability) Diverse SO-8 applications have passed some or all of the following reliability tests without failures: Temperature Cycling @ -65oC … +150oC: 500 cycles High Temperature Storage @175oC: 1,000hours Pressure Cooker Test @ [Ta = 121oC, RH=100%, 15PSIG]: 168hours Thermal Humidity Test @ [Ta = 85oC, RH=85%]: 168hours MSL 2: [Ta = 85oC, RH=60%,168hours; IR 260oC: 3 cycles] APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Performance/Reliability/Cost Electrical Performance die size range length ! 120mil, width ! 70mil for DS typical die size 9mm2, for example 140mil x 100mil length ! 70mil, width ! 40mil for SS, ! 70mil for DS 4.5mm2, for example 100mil x 70mil layout for typical die size 22x2mil Au: 1.6m" electrical performance 2x40x4mil DS: 0.5m" 14x2.75mil Au: 0.8m" 5mil Cu strap: 0.5m" 1x40x4mil DS: 1.1m" 7x2mil Cu: 4.5m" 1x60x4mil DS: 0.7m" 7x2mil Cu: 0.1 cents 1x60x4mil Al: 0.1 cents 18x3mil Cu: 0.5m" material cost 22x2mil Au: 2.5 cents 2x40x4mil Al: 0.2 cents 14x2.75mil Au: 3.0cents 7x2mil Au: 0.6 cents 18x3mil Cu: 0.3 cents Productivity (estimate) 1,500h-1, per head APEC’09, Washington, DC 1,800h-1, per head DCHopkins@Eng.Buffalo.Edu 3,200h-1, per head 3,200h-1, per head Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Performance/Reliability/Cost Cost Considerations All the different interconnect categories have weakness in at least one cost category: • • • • • Material cost for the actual interconnect Process equipment Process consumables including utilities Top die metallization Process yield APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins Summary Summary / Conclusion • Ribbon is an evolutionary improvement of large Al wire bonding • Ribbon cannot achieve the same electrical performance as an optimally designed Cu strap or wire bond-free design • It is a low cost interconnect, especially suited for smaller power packages such as SO8 and PQFN • In leadless packages Al ribbon offers comparable thermal performance to a Cu strap. • It offers comparable electrical performance to Cu wire at comparable cost • It offers a higher yield v. Cu wire bonding and is well suited for bonding on active surfaces due to its gentle bond process • Monometallic Al-Al system on the die enables reliable operation up to 175°C chip junction temperature APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu Courtesy of Orthodyne, 2007 © 2009, D. C. Hopkins End Wire Bonding Return to Main Presentation APEC’09, Washington, DC DCHopkins@Eng.Buffalo.Edu © 2009, D. C. Hopkins