Lab #1 Resistor Networks - UBC Electrical and Computer Engineering

advertisement

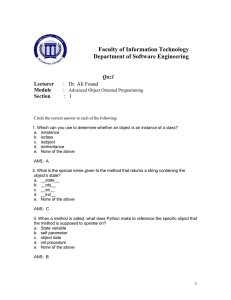

Lab #1 Resistor Networks Due: End of THIS Lab Session Name / SN:____________________________________ TA: __________ Name / SN:____________________________________ TA: __________ A) Pick up the following components from the TA: 1. 2. 3. 4. 5. 1K resistor (1) 2K resistor (1) 3K resistor (1) 3.9K resistor (1) 5.1K resistor (1) B) Build the circuit below with only the voltage source (no current source). TA: ____________________________________ 1. Use a single resistor for each of R1-R5. Measure the actual resistance of each. Indicate the printed, actual, and % error of each resistor. Ans: ____________________________________ R1 Ans: ____________________________________ R2 Ans: ____________________________________ R3 Ans: ____________________________________ R4 Ans: ____________________________________ R5 2. Measure the total resistance seen by the voltage source and compute the % error with respect to the ideal theoretical value. Ans: ____________________________________ ECE 251 - Circuit Analysis I Rtot Department of Electrical & Computer Engineering, UBC 3. With the voltage source enabled, measure the voltages at all nodes and the currents in all branches. Ans: ____________________________________ v1 Ans: ____________________________________ v2 Ans: ____________________________________ i1 Ans: ____________________________________ i2 Ans: ____________________________________ i3 Ans: ____________________________________ i4 4. Show that KVL holds in the outermost loop and that KCL holds at node n2. Ans: ____________________________________ KVL Ans: ____________________________________ KCL C) Remove (S/C = 0V) the voltage source and add the current source to the circuit. TA: ____________________________________ 1. Measure the total effective resistance seen by the current source. Ans: 2. ____________________________________ Rtot Measure the voltages at all nodes and the currents in all branches. Ans: ____________________________________ v1 Ans: ____________________________________ v2 Ans: ____________________________________ i1 Ans: ____________________________________ i2 Ans: ____________________________________ i3 Ans: ____________________________________ i4 ECE 251 - Circuit Analysis I Department of Electrical & Computer Engineering, UBC 3. Show that KVL holds in the outermost loop and that KCL holds at node n2. Ans: ____________________________________ KVL Ans: ____________________________________ KCL D) Reconnect the voltage source to the circuit. TA: ____________________________________ 1. Use superposition to compute the voltages at all nodes and the currents in all branches from the measurements you have already taken. Ans: ____________________________________ v1 Ans: ____________________________________ v2 Ans: ____________________________________ i1 Ans: ____________________________________ i2 Ans: ____________________________________ i3 Ans: ____________________________________ i4 2. Measure the voltages at all nodes, the currents in all branches, and the % error with respect the values computed above. Ans: ____________________________________ v1 Ans: ____________________________________ v2 Ans: ____________________________________ i1 Ans: ____________________________________ i2 Ans: ____________________________________ i3 Ans: ____________________________________ i4 ECE 251 - Circuit Analysis I Department of Electrical & Computer Engineering, UBC i1 n2 n1 i2 i3 i4 ECE 251 - Circuit Analysis I Department of Electrical & Computer Engineering, UBC