View New Course Proposal

New Undergraduate Course Proposal Form

1. Department and Contact Information

Tracking Number

718

Date & Time Submitted

2008-02-08 17:03:57

Department

Computer Science & Engineering

College

Engineering

Budget Account Number

2108-000-00

Contact Person

Ed Kellner

Phone

974-0909

Email

ekellner@cse.usf.edu

2. Course Information

Prefix

CDA

Number

4213L

Full Title

CMOS-VLSI Design Lab

Is the course title variable?

Is a permit required for registration?

Are the credit hours variable?

N

N

N

Credit Hours

1

Section Type

Laboratory

Grading Option

Regular

Total Clock Hours

32

Abbreviated Title (30 characters maximum)

CMOS-VLSI Lab

Prerequisites

CDA3201, CDA-3201L

Corequisites

CDA-4213

Co-Prerequisites

Course Description

Scalable CMOS layout design,circuit extraction,transistor-level and lay-out level simulation,SPICE

parameters/modeling,transistor sizing,standard and macro-cell based layout, static/dynamic

CMOS,combinational/sequential block layout,memory I/O design.

3. Gordon Rule

Does this course meet the writing portion of the Gordon Rule?

N

http://www.ugs.usf.edu/ugc/Proposals/view_new.cfm?ID=718 (1 of 3) [2/19/2008 5:09:49 PM]

View New Course Proposal

If you checked "yes" above, specify how the 6,000 words will be covered (exams, papers).

N/A

Does this course meet the computation portion of the Gordon Rule?

N

4. Justification

A. Indicate how this course will strengthen the Undergraduate Program. Is this course necessary

for accreditation or certification?

This lab is a compliment to CDA-4213. It allows hands-on implimentation of

concepts discussed in lecture. Students learn state-of-the-art design tools, such as

CADENCE and SYNOPSYS. Students will use procedures currently used in industry.

B. What specific area of knowledge is covered by this course which is not covered by courses

currently listed?

This is the labratory portion of an engineering design course. Labratory work is

essential to impliment engineering design. This course also teaches design tools not

used in other courses.

C. What is the need or demand for this course? (Indicate if this course is part of a required

sequence in the major.) What other programs would this course service?

This course becomes a required course in the Fall 2008 catalog. It is required for all

Computer Engineering majors. The current program has a lecture-lab combination,

but that does not allow sufficient labratory experience. The normal demand for this

course as an elective is 25-30 students/year. This course is also applicable to

electrical engineering majors.

D. Has this course been offered as Selected Topics/Experimental Topics course? If yes, what was

the enrollment?

No. It was part of CDA-4213, which has a normal enrollment of 25.

E. How frequently will the course be offered? What is the anticipated enrollment?

Once a year. It will part of a two-course sequence for computer hardware design.

Enrollment will depend on the number of majors, but 25-30/year is anticipated.

F. Do you plan to drop a course if this course is added? If so, what will be the effect on the

program and on the students? (Please forward the nonsubstantive course change form regarding

the course to be deleted to the Council secretary.)

No. This course helps to complete the number of required hours for the major

without hardship on the student.

G. What qualifications for training and/or experience are necessary to teach this course? (List

minimum qualifications for the instructor.)

http://www.ugs.usf.edu/ugc/Proposals/view_new.cfm?ID=718 (2 of 3) [2/19/2008 5:09:49 PM]

View New Course Proposal

Masters degree in Computer Engineering or Electrical Engineering, with experience

in CMOS-VLSI design. Ph.D preferred.

5. Other Course Information

A. Objectives / Outcomes

To train students to utilize state-of-the-art design tools/Students will learn

CADENCE, SPICE, SYNOPSYS, and NONOSIM tools to aid in design (CAD tools). To

learn CMOS-VLSI layout design/Students will understand different layout design

techniques. To understand modular, scalable and bit-sliced VLSI layout/Students will

understand how and when to use each type of layout. To understand proper design

constraints/Students will understand parameters for area, speed and powerconsumption and how to apportion each for best utilization.

B. Major Topics

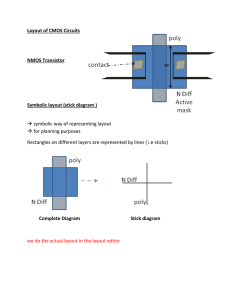

- Basic Layout design and utilization of Layout editior/CMOS transistor, MOS switch

behavior, transistion gates, CMOS invertor -Design Rule Check/Lambda-based

design rules, DRC check, Resistance and Capacitance Extraction. Transistor

extraction - SPICE modeling & Circuit Simulation - Delay analysis and optimimation Power analysis and optimization - Basic CMOS Cell Library Design - Bit-sliced Design

- Static and Dynamic CMOS -Datapath Design & Controller Design

C. Textbooks

CMOS-VLSI Design, with VHDL, Weste/Eshraghian, 2005, Pearson Publishing Modern

VLSI Design, Wolf, 2002, Pearson Publishing

6. Syllabus

Your college will forward an electronic copy of your syllabus to Undergraduate Studies when your

course is approved for submission.

http://www.ugs.usf.edu/ugc/Proposals/view_new.cfm?ID=718 (3 of 3) [2/19/2008 5:09:49 PM]

CDA 4213L: CMOS VLSI Design Lab

Instructor:

Instructor:

Dr. Srinivas Katkoori

Office:

ENB 316

Office Hours: TBA

Phone: 974-5737

Email:

katkoori@cse.usf.edu

Class Room & Timings: ENB 214 MW 11:00am–12:15pm

Course Catalog Description: Scalable CMOS layout design, circuit extraction, transistor-level and

layout-level Simulation, SPICE parameters and modeling, bit sliced design, transistor sizing,

standard cell and macro-cell based layout, static and dynamic CMOS, combinational & sequential

block layout, memory I/O design, basic CMOS cell library design, layout area minimization, power

analysis & optimization, and timing.

Prerequisites (No Exceptions):

Computer Logic Design (CDA 3201)

Computer Logic Design Lab (CDA 3201L)

Co-requisites (No Exceptions):

CMOS VLSI Design (CDA 4213)

This lab supplements the CMOS-VLSI design (CDA 4213) lecture class. The concepts taught in

the lecture class will be practiced in this lab.

Objectives:

1. Practice and learn state-of-the-art VLSI Layout editor

2. Proficient in writing SPICE stimuli and analyzing SPICE output

3. Analyze the trade-offs between area, speed, and power consumption.

4. Experience with integration of a custom IC design with a PAD frame

5. Validate the CMOS transistor behavior learnt in the lecture class

6. Use bit-sliced based design style learnt in lecture class, to implement parameterized

component library

7. Analyze a given IC specification and implement it using standard design flow taught in the

lecture class.

Learning Outcomes:

The students would know the basic concepts in computer chip design and have the experience of

design and verification of small and medium scale VLSI chips and obtain insights into the various

issues of VLSI technology and computer chip design

Course Textbook:

“Principles of CMOS VLSI Design: A Systems Perspective,” N. Weste & D. Harris, Third Edition, Pearson

Addison-Wesley, 2004, ISBN 0-321-14901-7.

1

Grade Distribution:

There will be 6 Lab Assignments (each worth 10%) and one final project (worth 40%). The final

project will be a custom IC design that will be fabricated using MOSIS services.

Grading Policy:

A+:

> 95%

B+:

84-87%

C+:

74-77%

F:

< 65%

A:

90-95%

A-:

B:

80-84%

C:

70-74%

87-90%

B-:

77-80%

C-:

65-70%

Topics:

1. Basic Layout Design and Introduction to Layout Editor

2. Design Rule Check and Circuit Extraction

3. SPICE Modeling and Circuit Simulation

4. Delay Analysis and Optimization

5. Power Analysis and Optimization

6. Basic CMOS Cell Library Design – Bit-sliced design

7. Static and Dynamic CMOS

8. Memory Design

9. Datapath Design & Controller Design

10. PAD Frame Integration

General Policies:

Academic dishonesty will not be tolerated and the student, in question, will be dealt

with in accordance with the University policies.

If you need any special accommodation according to the American Disability Act,

please let me know.

Students who anticipate the necessity of being absent from class due to the observation

of a major religious observance must provide notice of the date(s) in writing by the

second class meeting.

Good Luck!!

2