Document Number: MMG5004N

Rev. 0, 8/2006

Freescale Semiconductor

Technical Data

Heterojunction Bipolar Transistor

Technology (InGaP HBT)

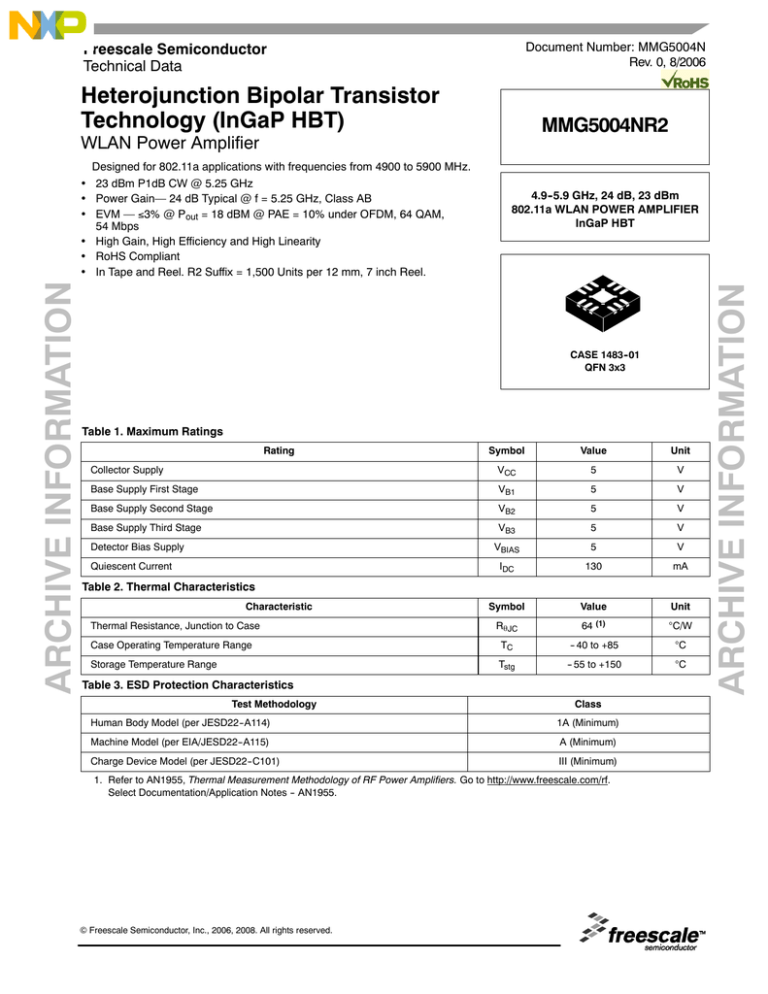

MMG5004NR2

WLAN Power Amplifier

4.9--5.9 GHz, 24 dB, 23 dBm

802.11a WLAN POWER AMPLIFIER

InGaP HBT

CASE 1483--01

QFN 3x3

Table 1. Maximum Ratings

Rating

Symbol

Value

Unit

Collector Supply

VCC

5

V

Base Supply First Stage

VB1

5

V

Base Supply Second Stage

VB2

5

V

Base Supply Third Stage

VB3

5

V

VBIAS

5

V

IDC

130

mA

Symbol

Value

Unit

(1)

°C/W

Detector Bias Supply

Quiescent Current

Table 2. Thermal Characteristics

Characteristic

Thermal Resistance, Junction to Case

RθJC

64

Case Operating Temperature Range

TC

-- 40 to +85

°C

Storage Temperature Range

Tstg

-- 55 to +150

°C

Table 3. ESD Protection Characteristics

Test Methodology

ARCHIVE INFORMATION

ARCHIVE INFORMATION

Designed for 802.11a applications with frequencies from 4900 to 5900 MHz.

• 23 dBm P1dB CW @ 5.25 GHz

• Power Gain— 24 dB Typical @ f = 5.25 GHz, Class AB

• EVM — ≤3% @ Pout = 18 dBM @ PAE = 10% under OFDM, 64 QAM,

54 Mbps

• High Gain, High Efficiency and High Linearity

• RoHS Compliant

• In Tape and Reel. R2 Suffix = 1,500 Units per 12 mm, 7 inch Reel.

Class

Human Body Model (per JESD22--A114)

1A (Minimum)

Machine Model (per EIA/JESD22--A115)

A (Minimum)

Charge Device Model (per JESD22--C101)

III (Minimum)

1. Refer to AN1955, Thermal Measurement Methodology of RF Power Amplifiers. Go to http://www.freescale.com/rf.

Select Documentation/Application Notes -- AN1955.

© Freescale Semiconductor, Inc., 2006, 2008. All rights reserved.

RF Device Data

Freescale Semiconductor

MMG5004NR2

1

Table 4. Moisture Sensitivity Level

Test Methodology

Per JESD 22--A113, IPC/JEDEC J--STD--020

Rating

Package Peak Temperature

Unit

1

260

°C

Table 5. Electrical Characteristics (TA = 25°C unless otherwise noted.) VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc, VBIAS = 3 Vdc,

Symbol

Min

Typ

Max

Unit

P1dB

—

23

—

dBm

Power Gain

(Pout = 18 dBm, OFDM, 64 QAM, 54 Mbps)

Gp

—

24

—

dB

Error Vector Magnitude

(Pout = 18 dBm, OFDM, 64 QAM, 54 Mbps)

EVM

—

3

—

%

Total Current

(Pout = 18 dBm, OFDM, 64 QAM, 54 Mbps)

ICtotal

—

200

—

mA

Quiescent Current

ICQ

—

105

—

mA

Bias Control Reference Current

(ICQ = 105 mA)

Iref

—

7

—

mA

Gain Flatness

(Over 100 MHz)

GF

—

±0.2

—

dB

Gain Variation over Temperature

(--40 to 85°C)

—

—

±1

—

dB

Input Return Loss

IRL

—

--15

—

dB

Reverse Isolation

—

—

--40

—

dB

Second Harmonic

(Pout = 18 dBm, OFDM, 64 QAM, 54 Mbps)

—

—

--50

—

dBc

Third Harmonic

(Pout = 18 dBm, OFDM, 64 QAM, 54 Mbps)

—

—

--50

—

dBc

Ramp--On Time (10--90%)

tON

—

100

—

ns

Characteristic

ARCHIVE INFORMATION

Output Power at 1dB Compression, CW

ARCHIVE INFORMATION

ICQ = 105 mA, f = 5250 MHz

MMG5004NR2

2

RF Device Data

Freescale Semiconductor

Name

Pin

Number

Description

VCC1

1

Power supply for first stage amplifier.

VB1

2

Bias current control voltage for the first stage. The

VB1 pin can be combined with VB2 and VB3 into a

single current control voltage (VBC).

RFIN

3

RF input for the power amplifier. This pin is

DC--shorted to GND and AC--coupled to the

transistor base of the first stage.

VBIAS

5

Detector bias voltage supply.

VREF

6

Detector output voltage reference. Vout -- VREF is

useful for tracking detector performance over

temperature.

VOUT

7

Detector output voltage.

RFOUT

8, 9

RF output for the power amplifier. This pin is

DC--coupled and requires a DC--blocking capacitor.

VCC3

8, 9

Power supply for third stage amplifier.

VB2

10

Bias current control voltage for the second stage.

The VB2 pin can be combined with VB1 and VB3 into

a single current control voltage (VBC).

VCC2

11

Power supply for second stage amplifier.

VB3

12

Bias current control voltage for third stage. The VB3

pin can be combined with VB1 and VB2 into a single

current control voltage (VBC).

GND

Center

Metal

The center metal base of the QFN 3x3 package

provides both DC/RF ground as well as heat sink for

the power amplifier.

VB2 VCC2 VB3

12 11 10

VCC1 1

VB1 2

9

RFOUT, VCC3

8

RFOUT, VCC3

3

7

VOUT

RFIN

4

5

6

NC VBIAS VREF

(Top View)

Figure 1. Pin Connections

ARCHIVE INFORMATION

ARCHIVE INFORMATION

Table 6. Functional Pin Description

MMG5004NR2

RF Device Data

Freescale Semiconductor

3

VB1

VCC1

VB2 VCC2

C1

C2

C3

VB3

VCC3

C4

C5

C6

Z4

RF

INPUT

Z1

Z2

Z3

Z5

RF

OUTPUT

C7

VBIAS

C8

VREF

C9

VOUT

Z1

Z2

Z3

Z4

PCB

0.010″ x 0.556″ Microstrip

0.010″ x 0.405″ Microstrip

0.010″ x 0.106″ Microstrip

0.004″ x 0.330″ Microstrip

Getek ML200M, 0.005″, εr = 3.8

Figure 2. MMG5004NR2 Test Circuit Schematic

Table 7. MM5004NR2 Test Circuit Component Designations and Values

Part

Description

Part Number

Manufacturer

C1, C3, C5

100 pF Chip Capacitors

08055A101FAT2A

AVX

C2, C4, C6

1 μF Chip Capacitors

12065A105JAT2A

AVX

C7, C8, C9

27 pF Chip Capacitors

06035A270FAT2A

AVX

C10

0.7 pF Chip Capacitor

04025J0R788W

AVX

C11

22 pF Chip Capacitor

06035A220FAT2A

AVX

ARCHIVE INFORMATION

ARCHIVE INFORMATION

C11

C10

MMG5004NR2

4

RF Device Data

Freescale Semiconductor

VB1

VCC1

VB2

VCC2

VB3

C6

C4

C1

VCC3

C2

C5

C11

C10

C7

C8

C9

VBIAS

VREF

VOUT

ARCHIVE INFORMATION

ARCHIVE INFORMATION

C3

Freescale has begun the transition of marking Printed Circuit Boards (PCBs) with the Freescale

Semiconductor signature/logo. PCBs may have either Motorola or Freescale markings during the

transition period. These changes will have no impact on form, fit or function of the current product.

Figure 3. MMG5004NR2 Test Circuit Component Layout

MMG5004NR2

RF Device Data

Freescale Semiconductor

5

TYPICAL CHARACTERISTICS

10

24.5

Gp, POWER GAIN (dB)

24

23.5

23

22.5

22

21.5

21

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

f = 5250 MHz, OFDM, 64 QAM, 54 Mbps

20.5

6

2

10

14

18

7

6

5

4

3

2

1

22

2

6

10

14

18

Pout, OUTPUT POWER (dBm)

Pout, OUTPUT POWER (dBm)

Figure 4. Power Gain versus Output Power

Figure 5. Error Vector Magnitude versus

Output Power

22

350

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

f = 5250 MHz, OFDM, 64 QAM, 54 Mbps

18

PAE, POWER ADDED EFFICIENCY (%)

8

0

20

14

12

10

8

6

4

300

275

250

225

200

175

150

2

125

0

100

6

2

10

14

18

22

2

6

10

14

18

Pout, OUTPUT POWER (dBm)

Pout, OUTPUT POWER (dBm)

Figure 6. Power Added Efficiency versus

Output Power

Figure 7. Total Current versus Output Power

10

22

40

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

f = 5250 MHz, OFDM, 64 QAM, 54 Mbps

SMALL SIGNAL GAIN (dB)

30

1

0.1

0.01

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

f = 5250 MHz, OFDM, 64 QAM, 54 Mbps

325

ICC, TOTAL CURRENT (mA)

16

Vout , DETECTOR OUTPUT VOLTAGE (V)

ARCHIVE INFORMATION

20

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

f = 5250 MHz, OFDM, 64 QAM, 54 Mbps

9

20

10

0

--10

--20

--30

--40

--50

2

6

10

14

18

22

ARCHIVE INFORMATION

EVM, ERROR VECTOR MAGNITUDE (%)

25

--60

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

0

2

4

6

8

Pout, OUTPUT POWER (dBm)

f, FREQUENCY (GHz)

Figure 8. Detector Output Voltage versus

Output Power

Figure 9. Small Signal Gain (S21) versus

Frequency

10

MMG5004NR2

6

RF Device Data

Freescale Semiconductor

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

IRL, INPUT RETURN LOSS (dB)

--2

--4

--6

--8

--10

--12

--14

--16

--20

0

2

4

6

8

10

--10

--20

--30

--40

--50

--60

--70

--80

--90

--100

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

0

2

4

6

8

f, FREQUENCY (GHz)

f, FREQUENCY (GHz)

Figure 10. Input Return Loss (S11) versus

Frequency

Figure 11. Reverse Transconductance

Isolation (S12) versus Frequency

0

--2

ORL, OUTPUT RETURN LOSS (dB)

ARCHIVE INFORMATION

--18

0

--4

--6

--8

--10

--12

--14

--16

--18

--20

VCC = 3.3 Vdc, VB1, VB2, VB3 = 2.8 Vdc

0

2

4

6

8

f, FREQUENCY (GHz)

Figure 12. Output Return Loss (S22) versus

Frequency

10

ARCHIVE INFORMATION

0

REVERSE TRANSCONDUCTANCE ISOLATION (dB)

TYPICAL CHARACTERISTICS

10

MMG5004NR2

RF Device Data

Freescale Semiconductor

7

A

4X D

C

b 1

E

E/2

PIN1 ID

N=12

4X D

1

2

3

0.45

1

2

3

B

2

F

F/2

(Ny--1)e

L

0.25 MIN.

SEATING

PLANE

TOP VIEW

SIDE VIEW

e

(Nx--1)e

2

BOTTOM VIEW

NOTES:

1. DIMENSION b APPLIES TO PLATED TERMINAL AND IS

MEASURED BETWEEN 0.20 AND 0.25 MM FROM

TERMINAL TIP.

2. N IS THE NUMBER OF TERMINALS (12).

Nx IS THE NUMBER OF TERMINALS IN X--DIRECTION

AND

Ny IS THE NUMBER OF TERMINALS IN Y--DIRECTION.

3. ALL DIMENSIONS ARE IN MILLIMETERS.

DIM

A

B

C

D

E

F

b

e

Nx

Ny

SYMBOLS

EXPOSED PAD

MIN

1.15

MIN

NOM

MAX

3.00 BSC

3.00 BSC

-0.85

1.00

0.24

0.42

0.60

SEE EXPOSED PAD

SEE EXPOSED PAD

0.18

0.23

0.30

0.50 BSC

3

3

E

NOM

1.30

MAX

1.45

MIN

1.15

STANDARD

DETAIL ”A” -- PIN #1 ID AND TIE BAR MARK OPTION

F

NOM

1.30

MAX

1.45

Figure 13. MMG5004NR2 Specific Mechanical Outline Information

ARCHIVE INFORMATION

ARCHIVE INFORMATION

0.25 MIN.

MMG5004NR2

8

RF Device Data

Freescale Semiconductor

PACKAGE DIMENSIONS

A

3

M

PIN 1 INDEX

AREA

2X

0.1 C

DETAIL G

B

M

2X

0.1 C

1.55

1.25

12

10

EXPOSED DIE

ATTACH PAD

DETAIL M

PIN 1 INDEX

9

1

1.55

1.25

3

7

DETAIL N

6

12X 0.75

0.50

9

4

12X 0.30

0.18

0.10

M

8X 0.5

C A B

VIEW M -- M

CASE 1483--01

ISSUE A

QFN 3x3

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND

TOLERANCES PER ASME Y14.5M, 1994.

3. THE COMPLETE JEDEC DESIGNATOR FOR

THIS PACKAGE IS: HF--PQFP--N.

4. FOR ANVIL SINGULATED QFN PACKAGES,

MAXIMUM DRAFT ANGLED IS 12 _.

5. PACKAGE WARPAGE MAX 0.05 MM.

6. CORNER CHAMFER MAY NOT BE PRESENT.

DIMENSIONS OF OPTIONAL FEATURES ARE

FOR REFERENCE ONLY.

7. CORNER LEADS CAN BE USED FOR

THERMAL OR GROUND AND ARE TIED TO

THE DIE ATTACH PAD. THESE LEADS ARE

NOT INCLUDED IN THE LEAD COUNT.

8. COPLANARITY APPLIES TO LEAD, CORNER

LEADS, AND DIE ATTACH PAD.

9. THIS DIMENSION APPLIES TO PLATED

TERMINAL AND IS MEASURED BETWEEN

0.20 MM AND 0.25 MM FROM TERMINAL TIP.

ARCHIVE INFORMATION

ARCHIVE INFORMATION

3

(continued)

MMG5004NR2

RF Device Data

Freescale Semiconductor

9

0.60

0.24

(45_)

(0.25)

0.60

0.24

DETAIL N

CORNER CONFIGURATION

6

6

ARCHIVE INFORMATION

DETAIL N

PREFERRED CORNER CONFIGURATION

0.1 C

1.0

0.8

1.00

0.75

0.05 C

0.05

0.00

C

DETAIL G

VIEW ROTATED 90_ CW

8

SEATING

PLANE

ARCHIVE INFORMATION

(0.25)

CASE 1483--01

ISSUE A

QFN 3x3

(continued)

MMG5004NR2

10

RF Device Data

Freescale Semiconductor

0.217

0.137

DETAIL S

(0.25)

0.217

0.137

(0.1)

DETAIL S

BACKSIDE PIN 1 INDEX

DETAIL M

PREFERRED BACKSIDE PIN 1 INDEX

7

TIE BAR MARK OPTION

PIN 1 ID

4X 0.23

0.13

(45_ )

4X 0.65

0.30

(0.45)

(0.35)

R0.2

PIN 1 ID

DETAIL M

DETAIL M

BACKSIDE PIN 1 INDEX OPTION

BACKSIDE PIN 1 INDEX OPTION

ARCHIVE INFORMATION

ARCHIVE INFORMATION

(0.25)

CASE 1483--01

ISSUE A

QFN 3x3

MMG5004NR2

RF Device Data

Freescale Semiconductor

11

Home Page:

www.freescale.com

E--mail:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

+1--800--521--6274 or +1--480--768--2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1--8--1, Shimo--Meguro, Meguro--ku,

Tokyo 153--0064

Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1--800--441--2447 or 303--675--2140

Fax: 303--675--2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software

implementers to use Freescale Semiconductor products. There are no express or

implied copyright licenses granted hereunder to design or fabricate any integrated

circuits or integrated circuits based on the information in this document.

ARCHIVE INFORMATION

ARCHIVE INFORMATION

How to Reach Us:

Freescale Semiconductor reserves the right to make changes without further notice to

any products herein. Freescale Semiconductor makes no warranty, representation or

guarantee regarding the suitability of its products for any particular purpose, nor does

Freescale Semiconductor assume any liability arising out of the application or use of

any product or circuit, and specifically disclaims any and all liability, including without

limitation consequential or incidental damages. “Typical” parameters that may be

provided in Freescale Semiconductor data sheets and/or specifications can and do

vary in different applications and actual performance may vary over time. All operating

parameters, including “Typicals”, must be validated for each customer application by

customer’s technical experts. Freescale Semiconductor does not convey any license

under its patent rights nor the rights of others. Freescale Semiconductor products are

not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other application in which the failure of the Freescale Semiconductor product

could create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended or

unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all

claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Freescale

Semiconductor was negligent regarding the design or manufacture of the part.

Freescalet and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006, 2008. All rights reserved.

MMG5004NR2

Document Number: MMG5004N

Rev. 0, 8/2006

12

RF Device Data

Freescale Semiconductor