WEA14S - weasic

WEA14S

Microwave Fractional-N Synthesizer

PRODUCT DESCRIPTION

The weasic WEA14S is a complete 24 bits

Fractional-N microwave synthesizer able to synthesize frequencies from 13GHz to 15

GHz with the integrated VCO or from 8 GHz to 16 GHz with an external VCO. It consists of a low noise phase detector with lock detect indication, a programmable charge pump, a programmable bandwidth loop filter, a multi modulus prescaler, and a 64 band VCO with auto-calibration circuitry.

Implemented in a 45nm CMOS SOI

GlobalFoundries process, the WEA14S occupies a silicon area of 3.4 mm 2 .

It exhibits high performance, high integration and flexibility targeting cutting edge applications operating in multi-GHz frequencies.

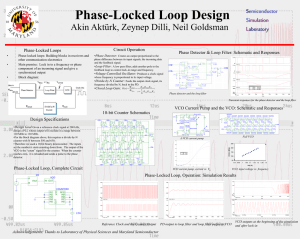

FUNCTIONAL BLOCK DIAGRAM

KEY FEATURES

Low Phase Noise PLL core

Reference input up to 250MHz

Low pin count, Zero external components, Self-calibrated

Programmable order MASH

Programmable Loop Filter

Optional external VCO

APPLICATIONS

High speed optical networks

Satellite communications

60GHz applications

Wireless LANs

5G Mobile

Figure 1. Synthesizer Architecture

Rev. B. The information contained in this document is preliminary and it is based on simulations. The information will be updated after the characterization phase. weasic microelectronics S.A., Monumental Plaza Complex,

Building C, 44 Kifisias ave. 15125 Maroussi, Greece info@weasic.com

, Tel: +30 211 800 0386-7

WEA14S

PIN CONFIGURATION AND FUNCTION DESCRIPTION

www.weasic.com

3

Figure 2. Chip top view

Table 1. Pin Function Descriptions

Pin No. Mnemonic Description

1

2

RFOUT

VDDMASH MASH/Prescaler Positive Supply

REFIN

VCO buffered output (50Ohm, -3dBm)

Clock Reference input. Standard CMOS input with nominal threshold VDD/2, max signal 1.5V, AC coupled

8

9

10

11

4

5

6

7

VDDPFD

TBO

CPOUT

VDDCP

VDDSPI

SI

EN

Phase Frequency detector Positive Supply

Test Bus output

Charge pump output. Optional output in case of external filter.

Charge Pump Positive Supply

VDDBGR Charge Pump Bandgap Reference Positive Supply

Serial Programming Interface Positive Supply

SPI Serial Input

SPI Enable

12

13

14

15

16

17 1

1 GND Paddle

CLK SPI CLK

VTUNE External tuning voltage. Optional input in case of external filter.

VCO bias capacitor. Optional decoupling capacitor for low

VCOCAP frequency VCO phase noise improvement.

VDDVCO VCO Positive Power Supply

RFIN

VSS

External VCO input. Optional input in case of an external VCO.

VCO power > -6 dBm for good phase noise performance

Global Negative Supply

Rev. B. (Preliminary Data) - Page 2 | 21

WEA14S

OPERATING CONDITIONS

Table 2.

Parameter

Supply Voltage

Total Current consumption (max)

Temperature

Power down current

TYPICAL PERFORMANCE

Table 3.

Metrics

VCO Center Frequency

VCO Tuning Range

VCO tuning sensitivity (Kv)

VCO pushing

VCO temperature sensitivity

VCO number of Bands

VCO Band separation

Tuning Range per band

Input reference

Loop Bandwidth

MASH order

Prescaler division

Normalized PLL Phase Noise @ 200KHz

Charge Pump Programmable Current

Typ

1

55

-40 - 125

TBD

Typ

14

2.3

200-400

20

500

64

35

300

20 - 250

50 - 2000

(1-1, 1-1-1)

32 - 639

-220

0.1 / 6.4

MHz

MHz

KHz dBc/Hz mA

Units

GHz

GHz

MHz/V

MHz/V

KHz/ o C

MHz www.weasic.com

Units

V mA o C uA

Rev. B. (Preliminary Data) - Page 3 | 21

WEA14S www.weasic.com

Figure 3. Typical phase noise graph @14 GHz, 80MHz Ref, 220 KHz LPBW, 1.2mA CP

DETAILED DESCRIPTION

VCO

The VCO is a transformer cross-coupled PFET pair integrated together with a constant current servo-loop to ensure startup and optimum phase noise performance. The tank consists of a capacitor and MOS varactor array designed to maintain the same tuning slope and the same frequency separation over the entire 64 bands. Frequency band separation together with the temperature dependent auto-calibration circuit ensures the “in-the-sameband” VCO operation over a temperature range from -40 o C to 120 o C allowing a continuous and uninterrupted synthesizer operation for critical systems under large temperature variations.

Prescaler

The Multi-modulus Prescaler consists of cascaded 2/3 and 3/4 cells and it is capable of 32-

639 division. The Prescaler comprises retiming scheme for jitter removal. The prescaler is

capable to handle signals from 8 GHz to 16 GHz. In Table 4 the bits configuration required for

the various division modes is shown.

Rev. B. (Preliminary Data) - Page 4 | 21

WEA14S www.weasic.com

Table 4. Prescaler control bits

PresDiv23Sel34<3:0> PresStgSel<3:0> PresByPass<3:0> Minimum

Division

Maximum

Division

0 0 0 0 1 1 1 0 0 0 0 1

0 0 0 1 1 1 1 0 0 0 0 1

0 0 0 0 1 1 0 0 0 0 1 0

32

48

64

63

79

127

0 0 1 0 1 1 0 0 0 0 1 0

0 0 0 0 1 0 0 0 0 1 0 0

0 1 0 0 1 0 0 0 0 1 0 0

0 0 0 0 0 0 0 0 1 0 0 0

1 0 0 0 0 0 0 0 1 0 0 0

96

128

192

256

384

159

255

319

511

639

MASH Delta-Sigma Modulator

Figure 4 depicts the programmable length (16-24 bit), programmable order (2nd/3rd-

order) MASH. MashInPart<7:0> is the integer part (N) and MashFracPart<23:0> is the numerator of the fractional part (K) of the division ratio. The fractional part of the division ratio is determined as the ratio K/2 m , where m is the number of the accumulator bits. The division ratio is given by: Minimum_Division * +N+K/2 m . The accumulators are implemented by ripple carry adders. The Accumulators have programmable length by masking the most significant bits.

* See Table 4.

Figure 4. Mash Architecture

Rev. B. (Preliminary Data) - Page 5 | 21

WEA14S

Table 5. MASH Enable and clock polarity selection control bits

MashClkPol

X

0

1

MashEn

0

1

1

Operation

Invalid clkb clk www.weasic.com

Table 6. Integer/Fractional output control bit

MashSelFrac Operation

0

1

Integer Mode

Fractional Mode

Table 7. Order of MASH control bits

Mash23Sel

0

1

Operation

2 nd order MASH

3 rd order MASH

Table 8. MASH length control bits

MashSelSum<7:0> MashSelCarry<8:0>

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 1 0

0 0 0 0 0 0 1 1

0 0 0 0 0 1 1 1

0 0 0 0 1 1 1 1

0 0 0 1 1 1 1 1

0 0 0 0 0 0 1 0 0

0 0 0 0 0 1 0 0 0

0 0 0 0 1 0 0 0 0

0 0 0 1 0 0 0 0 0

0 0 1 1 1 1 1 1

0 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1

0 0 1 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0

MASH bit length

16

17

18

19

20

21

22

23

24

Phase Frequency Detector

The PFD takes input from the clock reference input (REFIN) and the output of the Prescaler and produces an output proportional to the phase difference between them. The PFD has a

3-bit delay control block producing a delay in the output pulse width. In addition, the PFD utilizes an Edge Polarity and Pin swap function for loop polarity control.

Charge Pump and Offset DAC

The Charge pump is programmable and capable of delivering 100uA up to 6.4mA with 100u step. The Offset DAC pulls the PFD / Charge Pump operating point into a linear region. In order to improve noise in fractional operation.

Rev. B. (Preliminary Data) - Page 6 | 21

WEA14S

011110

011111

100000

100001

100010

100011

100100

100101

100110

100111

101000

101001

101010

001010

001011

001100

001101

001110

001111

010000

010001

010010

010011

010100

010101

010110

010111

011000

011001

011010

011011

011100

011101

Table 9. Charge Pump Current Programming control bits

CPCurSel<5:0>

000000

CP Current (uA)

100

000001

000010

000011

000100

200

300

400

500

000101

000110

000111

001000

001001

600

700

800

900

1000

1100

1200

1300

1400

1500

1600

1700

1800

1900

2000

2100

2200

2300

2400

2500

2600

2700

2800

2900

3000

3100

3200

3300

3400

3500

3600

3700

3800

3900

4000

4100

4200

4300 www.weasic.com

Rev. B. (Preliminary Data) - Page 7 | 21

WEA14S

001

010

011

100

101

110

111

101011

101100

101101

101110

101111

110000

110001

110010

110011

110100

4400

4500

4600

4700

4800

4900

5000

5100

5200

5300

110101

110110

110111

111000

5400

5500

5600

5700

111001

111010

111011

111100

111101

5800

5900

6000

6100

6200

111110

111111

6300

Table 10. Offset DAC Unit Current control bit

OffDacSet<2:0>

000

6400

Current (uA)

12.50

6.25

4.17

3.13

2.50

2.08

1.79

1.56 www.weasic.com

Table 11. Offset DAC Unit Current Multiplier control bit

OffDacSel<2:0> Current (uA)

000

001

OffDacSet_Current x 1

OffDacSet_Current x 2

010

011

100

101

110

111

OffDacSet_Current x 3

OffDacSet_Current x 4

OffDacSet_Current x 5

OffDacSet_Current x 6

OffDacSet_Current x 7

OffDacSet_Current x 8

Rev. B. (Preliminary Data) - Page 8 | 21

WEA14S

Loop Filter

www.weasic.com

The WEA14S loop filter that enables 3 different modes of operation depending on the wanted

Loop Bandwith (LB) of the PLL system: i) all filter components are external ( LB < 20KHz), ii) all filter components are internal forming a passive 3 rd order PLL system ( 100KHz < LB <

1MHz ), and iii) all filter components are internal used together with an operational amplifier that allows for lower LB ( 20KHz < LB < 250KHz) while keeping charge pump’s output near the reference level. All the resistive (Rz, Rf) and capacitive (Cp, Cz, Cf) components are programmable.

Figure 5. Loop filter topologies

0111

1000

1001

1010

1011

1100

1101

1110

1111

Table 12. Output reference voltage control bits

PllRefProgLvl<3:0> Voltage (V)

0000

0001

0.10

0.15

0010

0011

0100

0101

0110

0.20

0.25

0.30

0.35

0.40

0.45

0.50

0.55

0.60

0.65

0.70

0.75

0.80

0.85

Rev. B. (Preliminary Data) - Page 9 | 21

WEA14S www.weasic.com

Table 13. Loop Filter components Cp and Cz control bits

PllCpSel<3:0> Cp (pF)

0000

1.5

PllCzSel<3:0>

0000

Cz (pf)

30

0001

0010

0011

0100

3.0

4.5

6.0

7.5

0001

0010

0011

0100

60

90

120

150

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

9.0

10.5

12.0

13.5

15.0

16.5

18.0

19.5

21.0

22.5

24.0

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

180

210

240

270

300

330

360

390

420

450

480

Table 14. Loop Filter components Cf and Rf control bits

PllCfSel<4:0> Cf (pF) PllRfSel<4:0> Rf (KOhm)

00000

00001

0.5

1.0

00000

00001

40.00

20.00

00010

00011

00100

00101

00110

1.5

2.0

2.5

3.0

3.5

00010

00011

00100

00101

00110

13.33

10.00

8.00

6.67

5.71

00111

01000

01001

01010

01011

01100

01101

01110

01111

10000

10001

10010

10011

10100

10101

10110

4.0

4.5

5.0

5.5

6.0

6.5

7.0

7.5

8.0

8.5

9.0

9.5

10.0

10.5

11.0

11.5

00111

01000

01001

01010

01011

01100

01101

01110

01111

10000

10001

10010

10011

10100

10101

10110

5.00

4.44

4.00

3.64

3.33

3.08

2.86

2.67

2.50

2.35

2.22

2.11

2.00

1.90

1.82

1.74

Rev. B. (Preliminary Data) - Page 10 | 21

WEA14S

010100

010101

010110

010111

011000

011001

011010

011011

011100

011101

011110

011111

100000

000000

000001

000010

000011

000100

000101

000110

000111

001000

001001

001010

001011

001100

001101

001110

001111

010000

010001

010010

010011

10111

11000

11001

12.0

12.5

13.0

10111

11000

11001

11010

11011

11100

11101

13.5

14.0

14.5

11010

11011

11100

11101

150

11110

11111

15.5

16.0

11110

11111

Table 15. Loop Filter component Rz control bits

PllRzSel<5:0> Rz (KOhm)

3.81

3.64

3.48

3.33

3.20

3.08

2.96

2.86

2.76

2.67

2.58

2.50

2.42

5.71

5.33

5.00

4.71

4.44

4.21

4.00

80.00

40.00

26.67

20.00

16.00

13.33

11.43

10.00

8.89

8.00

7.27

6.67

6.15

1.67

1.60

1.54

1.48

1.43

1.38

1.33

1.29

1.25 www.weasic.com

Rev. B. (Preliminary Data) - Page 11 | 21

WEA14S

110010

110011

110100

110101

110110

110111

111000

111001

111010

111011

111100

111101

111110

111111

100001

100010

100011

100100

100101

100110

100111

101000

101001

101010

101011

101100

101101

101110

101111

110000

110001

1.38

1.36

1.33

1.31

1.29

1.27

1.25

1.57

1.54

1.51

1.48

1.45

1.43

1.40

1.82

1.78

1.74

1.70

1.67

1.63

1.60

2.35

2.29

2.22

2.16

2.11

2.05

2.00

1.95

1.90

1.86 www.weasic.com

Rev. B. (Preliminary Data) - Page 12 | 21

WEA14S

Adaptive Frequency Calibration (AFC) block

www.weasic.com

A very simple and efficient auto-calibration method is implemented to continuously maintain the optimum VCO sub-band and the VCO control voltage. The auto-calibration circuit is based on monitoring the VCO tuning voltage Vtune to find if it goes out of a predefined range between a high (vmidp) and a low (vmidn) threshold. Those thresholds are temperature dependent to track the effect of temperature on VCO sub-bands, thus making the algorithm adaptive on Temperature variations as well.

The VCO frequency selection method is based on a binary search algorithm using a 6bit SAR logic. The algorithm starts with the falling edge of the external Enable signal (pin EN) and if the control bit stAutoCal=’1’. At first cycle, SAR logic is initiated at the mid code (code

31). After 6 cycles (in the worst case), the algorithm will stop on the optimum code where the synthesizer settles into the lock state with the frequency of VCO approaching the target frequency. The clock applied to the AFC block is the reference clock divided by a programmable divider.

Table 16. Clk applied to auto-calibration block control bits

AutoCalRefDiv<2:0> REF CLK division

0

1

512

1024

2

3

4

2048

4096

8192

5

6

7

16384

32768

65536

Table 17. Search algorithm direction control bit

AutoCalPoll Search algorithm direction

0

1 ascending @ vtune>vmidp, descending @ vtune<vmidn ascending @ vtune<vmidp, descending @ vtune>vmidn

Comments

Depends on Kv sign and varactor band indexing

Rev. B. (Preliminary Data) - Page 13 | 21

WEA14S www.weasic.com

SPI

The SPI is a simple chain of 16 16-bit registers. All the bits are entered sequentially as described in the following figure.

Register Map

Table 18. Register 1

Bit No. Field

D255

D254

PRESVCOBUFPD

PRESCPD

D253

D252

D251

D250

VCOPD

Not Used

RFBUFOUTPD

RFBUFINPD<0>

D249

D248

D247

D246

D245

D244

D243

D242

RFBUFINPD<1>

PLLREFPD

OFFDACPD

CHPUMPPD

PFDPD

REFBUFPD

PLLOPPD

BGRPD

Figure 6. Serial Port Write Diagram

Description

Prescaler's Buffer Power-Down.

Prescaler Power-Down.

Internal VCO Power-Down.

Not Used.

RF-Out Driver Power-Down.

RF-In Buffer 1 Power Down.

RF-In Buffer 2 Power Down.

Charge Pump Voltage Reference Power-Down.

Offset DAC Power-Down.

Charge Pump Power-Down.

Phase Detector Power-Down.

Reference Buffer Power-Down.

Active Loop Filter OPAMP Power-Down.

Bandgap Reference Power-Down.

Rev. B. (Preliminary Data) - Page 14 | 21

WEA14S

D241

D240

VCOREFPD

Not Used

D232

D231

D230

D229

D228

D227

D226

D225

D224

Table 19. Register 2

Bit No. Field

D239

D238

PfdEdgePol2

TestSel<0>

D237

D236

D235

D234

D233

TestSel<1>

TestSel<2>

CPCurSel<0>

CPCurSel<1>

CPCurSel<2>

CPCurSel<3>

CPCurSel<4>

CPCurSel<5>

LockDelaySel<0>

LockDelaySel<1>

LockDelaySel<2>

PfdDeadZoneSel<0>

PfdDeadZoneSel<1>

PfdDeadZoneSel<1>

Table 20. Register 3

Bit No. Field

D223

D222

D221

D220

PfdLoopPolSw

OffDacPol

OffDacSet<0>

OffDacSet<1>

D219

D218

D217

D216

D215

D214

D213

OffDacSet<2>

PfdEdgePol1

PllRzSel<0>

PllRzSel<1>

PllRzSel<2>

PllRzSel<3>

PllRzSel<4>

D212

D211

D210

D209

D208

PllRzSel<5>

PllRefProgLvl<0>

PllRefProgLvl<1>

PllRefProgLvl<2>

PllRefProgLvl<3> www.weasic.com

Auto Tune Voltage Reference Power-Down.

Not Used.

Description

Phase Detector 2nd Input Edge Polarity selector.

Test Signal Out selector.

Signals: (VCO divided signal, MASH outputs, Lock

Detect, auto-tune comparators).

Charge Pump Current selector.

(Refer to the Charge Pump and Offset DAC Section).

Lock Detect Delay Line selector: (30ps, 78ps, 127ps,

226ps, 350ps, 620ps, 910ps, 1200ps).

PFD Dead Zone Delay Line selector: (30ps, 78ps,

127ps, 226ps, 350ps, 620ps, 910ps, 1200ps).

Description

Phase Detector inputs (Normal: 0/Swapped: 1).

(Sink:0/Source:1) Offset DAC current.

OffSet DAC current selector.

(Refer to the Charge Pump and Offset DAC Section).

Phase Detector 1st input Edge Polarity selector.

Loop Filter Rz Value selector.

(Refer to the Loop Filter Section).

Charge Pump Voltage Reference selector.

(Refer to the Loop Filter Section).

Rev. B. (Preliminary Data) - Page 15 | 21

WEA14S

Table 21. Register 4

Bit No. Field

D207 PllTopo<0>

D206

D205

PllTopo<1>

PllTopo<2>

D204

D203

D202

D201

D200

D199

D198

PllRfSel<0>

PllRfSel<1>

PllRfSel<2>

PllRfSel<3>

PllRfSel<4>

PllCfSel<0>

PllCfSel<1>

D197

D196

D195

D194

D193

D192

PllCfSel<2>

PllCfSel<3>

PllCfSel<4>

OffDacSel<0>

OffDacSel<1>

OffDacSel<2>

Table 22. Register 5

Bit No. Field

D191

D190

PllCzSel<0>

PllCzSel<1>

D189

D188

D187

D186

D185

D184

D183

D182

D181

PllCzSel<2>

PllCzSel<3>

PllCpSel<0>

PllCpSel<1>

PllCpSel<2>

PllCpSel<3>

PresStgSel<0>

PresStgSel<1>

PresStgSel<2>

D180

D179

D178

D177

D176

PresStgSel<3>

PresDiv23Sel34<0>

PresDiv23Sel34<1>

PresDiv23Sel34<2>

PresDiv23Sel34<3>

Table 23. Register 6

Bit No. Field

D175 PresRetimed

Description

External Loop Filter selector.

Internal Passive Loop Filter selector.

Internal Active Loop Filter selector.

Loop Filter Rf value selector.

(Refer to the Loop Filter Section).

Loop Filter Cf value selector.

(Refer to the Loop Filter Section).

Offset DAC current multiplication selector.

(Refer to the Charge Pump and Offset DAC Section).

Description

Loop Filter Cz value selector.

(Refer to the Loop Filter Section).

Loop Filter CP component value selector.

(Refer to the Loop Filter Section).

Prescaler stage selector.

(Refer to the Prescaler Section).

Prescaler stage division selector.

(Refer to the Prescaler Section). www.weasic.com

Description

Prescaler VCO Retiming Circuit enable.

Rev. B. (Preliminary Data) - Page 16 | 21

WEA14S

D174

D173

D172

D171

D170

D169

D168

D167

D166

D165

D164

D163

D162

D161

D160

Not Used

MashClkPol

MashEn

MashSelSum<0>

MashSelSum<1>

MashSelSum<2>

MashSelSum<3>

MashSelSum<4>

MashSelSum<5>

MashSelSum<6>

MashSelSum<7>

PresByPass<0>

PresByPass<1>

PresByPass<2>

PresByPass<3>

Table 24. Register 7

Bit No. Field

D159

D158

MashSelFrac

Mash23Sel

D157

D156

D155

D154

D153

D152

D151

D150

D149

MashSelCarry<0>

MashSelCarry<1>

MashSelCarry<2>

MashSelCarry<3>

MashSelCarry<4>

MashSelCarry<5>

MashSelCarry<6>

MashSelCarry<7>

MashSelCarry<8>

D148

D147

D146

D145

D144

MashClkDelay<0>

MashClkDelay<1>

MashClkDelay<2>

AutoCalPol spiTherVarSel

Table 25. Register 8

Bit No. Field

D143

D142

D141

D140

MashIntPart<0>

MashIntPart<1>

MashIntPart<2>

MashIntPart<3>

D139

D138

MashIntPart<4>

MashIntPart<5>

Not Used.

MASH Clock polarity selector.

MASH Power-Down. www.weasic.com

MASH 16-24 bit selector.

(Refer to the MASH Delta-Sigma Modulator Section)

Prescaler Stage selector.

(Refer to the Prescaler Section).

Description

Integer/Fractional Operation selector.

2nd/3rd Order MASH mode selector.

MASH 16-24 bit selector.

(Refer to the MASH Delta-Sigma Modulator Section).

MASH Input Clock Delay Line selector (30ps, 78ps,

127ps, 226ps, 350ps, 620ps, 910ps, 1200ps).

Automatic Varactor Polarity selector.

VCO's Varactor selector (manual/auto).

Description

Prescaler/MASH Integer Part value.

(Refer to the MASH Delta-Sigma Modulator

Section).

Rev. B. (Preliminary Data) - Page 17 | 21

WEA14S

D137

D136

D135

D134

D133

D132

D131

D130

D129

D128

MashIntPart<6>

MashIntPart<7>

MashFracPart<0>

MashFracPart<1>

MashFracPart<2>

MashFracPart<3>

MashFracPart<4>

MashFracPart<5>

MashFracPart<6>

MashFracPart<7>

Table 26. Register 9

Bit No. Field

D127 MashFracPart<8>

D126

D125

D124

D123

MashFracPart<9>

MashFracPart<10>

MashFracPart<11>

MashFracPart<12>

D108

D107

D106

D105

D104

D103

D102

D101

D100

D99

D122

D121

D120

D119

D118

D117

D116

MashFracPart<13>

MashFracPart<14>

MashFracPart<15>

MashFracPart<16>

MashFracPart<17>

MashFracPart<18>

MashFracPart<19>

D115

D114

D113

D112

MashFracPart<20>

MashFracPart<21>

MashFracPart<22>

MashFracPart<23>

Table 27. Register 10

Bit No. Field

D111 LockDetCnt<0>

D110

D109

LockDetCnt<1>

LockDetCnt<2>

AutoCalRefDiv<0>

AutoCalRefDiv<1>

AutoCalRefDiv<2>

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Description www.weasic.com

Prescaler/MASH Fractional Part value.

(Refer to the MASH Delta-Sigma Modulator Section)

Prescaler/MASH Fractional Part value.

(Refer to the MASH Delta-Sigma Modulator Section)

Description

Lock Detect Counter.

VCO Auto Calibration Clock. Division selector.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Rev. B. (Preliminary Data) - Page 18 | 21

WEA14S

D98

D97

D96

Not Used

Not Used

Not Used

D89

D88

D87

D86

D85

D84

D83

D82

D81

D80

Table 28. Register 11

Bit No. Field

D95

D94 spiVarTher<0> spiVarTher<1>

D93

D92

D91

D90 spiVarTher<2> spiVarTher<3> spiVarTher<4> spiVarTher<5> spiVarTher<6> spiVarTher<7> spiVarTher<8> spiVarTher<9> spiVarTher<10> spiVarTher<11> spiVarTher<12> spiVarTher<13> spiVarTher<14> spiVarTher<15>

Table 29. Register 12

Bit No. Field

D79

D78

D77 spiVarTher<16> spiVarTher<17> spiVarTher<18>

D76

D75

D74

D73

D72

D71

D70

D69

D68

D67

D66

D65

D64 spiVarTher<19> spiVarTher<20> spiVarTher<21> spiVarTher<22> spiVarTher<23> spiVarTher<24> spiVarTher<25> spiVarTher<26> spiVarTher<27> spiVarTher<28> spiVarTher<29> spiVarTher<30> spiVarTher<31>

Not Used.

Not Used.

Not Used.

Description www.weasic.com

VCO Varactor value. (Manual mode).

(Refer to the Adaptive Frequency Calibration block

Section).

Description

VCO Varactor value. (Manual mode).

(Refer to the Adaptive Frequency Calibration block

Section).

Rev. B. (Preliminary Data) - Page 19 | 21

WEA14S

Table 30. Register 13

Bit No. Field

D63 spiVarTher<32>

D62

D61 spiVarTher<33> spiVarTher<34>

D60

D59

D58

D57

D56

D55

D54 spiVarTher<35> spiVarTher<36> spiVarTher<37> spiVarTher<38> spiVarTher<39> spiVarTher<40> spiVarTher<41>

D53

D52

D51

D50

D49

D48 spiVarTher<42> spiVarTher<43> spiVarTher<44> spiVarTher<45> spiVarTher<46> spiVarTher<47>

Table 31. Register 14

Bit No. Field

D47

D46 spiVarTher<48> spiVarTher<49>

D45

D44

D43

D42

D41

D40

D39

D38

D37 spiVarTher<50> spiVarTher<51> spiVarTher<52> spiVarTher<53> spiVarTher<54> spiVarTher<55> spiVarTher<56> spiVarTher<57> spiVarTher<58>

D36

D35

D34

D33

D32 spiVarTher<59> spiVarTher<60> spiVarTher<61> spiVarTher<62> spiVarTher<63>

Table 32. Register 15

Bit No. Field

D31

D30

D29

Not Used

Not Used

Not Used

Description

Description www.weasic.com

VCO Varactor value. (Manual mode).

(Refer to the Adaptive Frequency Calibration block

Section).

VCO Varactor value. (Manual mode).

(Refer to the Adaptive Frequency Calibration block

Section).

Description

Not Used.

Not Used.

Not Used.

Rev. B. (Preliminary Data) - Page 20 | 21

WEA14S

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

D6

D5

D4

D3

D2

D1

D0

Table 33. Register 16

Bit No. Field

D15

D14

Not Used

Not Used

D13

D12

D11

D10

D9

D8

D7

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used stAutoCal www.weasic.com

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Description

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Not Used.

Start VCO Varactor Auto Calibration Sequence.

Rev. B. (Preliminary Data) - Page 21 | 21