Title Placeholder

advertisement

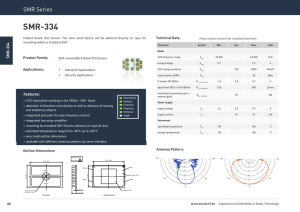

A Wide-Range VCO with Optimum Temperature Adaptive Tuning Behzad Saeidi1, Joshua Cho2, Georgi Taskov2, and Aaron Paff2 1 Marvell Semiconductor, Aliso Viejo, CA 92656; 2 Skyworks Solutions, Inc., Irvine, CA 92617 is a function of temperature which resembles the inverse function of VCO fine-tune characteristic. This guarantees that, regardless of coarse-tune temperature, PLL can remain locked despite as high VCO temperature frequency drift as VCO fine-tune range. Since this is the maximum frequency range VCO can cover without coarse-tune recalibration, the proposed approach is the optimum tuning scheme to deal with VCO temperature frequency drift. It paves the way to design a wide-range VCO with a small gain, making VCO robust to PLL tune voltage noise and spurs. The proposed scheme is implemented in the RX VCO of [1]. This note is organized as follows. The tuning process of a wide-range VCO is briefly reviewed in Section II. The proposed optimum temperature adaptive tuning, the main contribution of this paper, is presented in Section III. Design, circuit implementation and Lab measurement results are described in Section IV. The conclusions are summarized in Section V. Abstract — This paper presents an integrated wide-range VCO with a modified tuning scheme to deal with VCO frequency drift over temperature. In this approach, during the coarse-tune operation, VCO tune voltage is a function of temperature such that it resembles the inverse function of VCO fine-tune characteristic. Without degrading VCO performance, the proposed temperature adaptive tuning optimizes the maximum tolerable VCO temperature frequency drift over which PLL remains locked. As a result, VCO gain can be reduced significantly, making VCO less sensitive to PLL tune voltage noise. Integrated in a multistandard multi-band transceiver with a small VCO gain of 50MHz/V at 3.90GHz, PLL remains locked despite 45MHz frequency drift of VCO over [-30ºC, 85ºC]. Using an on-chip inductor, VCO covers from 3.15GHz to 4.60GHz, achieving -138.0dBc/Hz phase noise at 3.0MHz at 3.90GHz by drawing just 8.5mA from 1.60V supply in 0.13u CMOS process. Index Terms — Wide-range VCO, VCO temperature frequency drift, VCO fine-tune , on-chip inductor, PLL I. INTRODUCTION With the industry trend towards single chip implementation of multi-standard multi-band transceiver [1], there is a growing demand for wide-range VCO design which satisfies very stringent requirements over frequency and temperature. II. WIDE-RANGE VCO FREQUENCY TUNING To support a wide frequency range, VCO frequency range is first covered in discrete steps by digitally switchable coarse-tune capacitor arrays. Then, VCO fine-tune varactor(s) continuously covers each sub-range by analog tune voltage [4]. To guarantee the coverage, the fine-tune range should be no smaller than the coarse-tune resolution. Figure 1 illustrates block diagram of VCO frequency tuning circuit which involves two loops: DFC (Digital Frequency Converter)/VCO loop in coarse-tune and PLL/VCO loop in fine-tune. Figure 2 provides the details of the frequency tuning process of a VCO with a single PN-Junction varactor. It depicts the corresponding fine-tune curves of two consecutive coarse-tune codes: n and n-1, which the target frequency lies in between. For the illustration purpose, a very large coarse-tune resolution is chosen. As illustrated, VCO frequency tuning is a two-step procedure: coarse-tune and fine-tune. Based on an M-bit target frequency word, ftarget, VCO frequency is first coarse-tuned to the closest discrete frequency available by the coarse-tune capacitor arrays, coarse-tune curve number ‘n’. The N-bit digital coarse-tune code, ‘n’, is calculated by the DFC/VCO closed-loop, using the successive approximation method and a reference clock, fref. During coarse-tune calibration, VCO tune voltage, dfc_vtune, has In wide-range VCO design, besides low Q of on-chip inductor, loss of switchable capacitor arrays further degrades tank loaded-Q which consequently results in higher frequency drift over temperature [2]. For many applications such as full duplex systems, once the tuning is finished and the coarse-tune word is selected, PLL must remain locked over the entire temperature range without coarse-tune recalibration [3]–[5]. To guarantee the locked condition, several solutions have been proposed which can be categorized into two main approaches: (I) Extending VCO fine-tune frequency range by increasing VCO gain [3] and/or PLL tune voltage range [4]; (II) Reducing VCO temperature frequency drift by adding redundancy to VCO circuit [5]. High VCO gain causes high sensitivity to PLL tune voltage noise which increases the spur level and degrades the phase noise. Moreover, as power supply and size shrink, PLL tune voltage range decreases too. On the other hand, the proposed circuitries to reduce VCO temperature frequency drift degrade phase noise and make VCO prone to power supply noise and pushing. This paper presents a modified temperature adaptive tuning scheme. Here, during coarse-tune, VCO tune voltage PREPRESS PROOF FILE 1 CAUSAL PRODUCTIONS DFC f target dfc_vtune n vco_vtune f coarse_tune 3950 N coarse_tune VCO vco_out f vco 3940 3930 3920 ∆f ftarget 3910 3900 fcoarse_tune 3890 ∆V 3880 pll_vtune reference_clock PLL f target 3870 0.15 0.25 0.35 0.45 0.55 0.65 0.75 0.85 pll_vtune M dfc_vtune 3960 f ref Frequency (MHz) reference_clock target_frequency 0.95 1.05 1.15 1.25 1.35 Tune Voltage (V) f ref coarse_tune = n coarse_tune = (n-1) Fig. 1. Block diagram of frequency tuning circuit of a widerange VCO Fig. 2. VCO frequency tuning, two consecutive fine-tune curves which the target frequency lies in between been so far kept constant [2]-[5]. Once VCO is coarsetuned, there exists a difference between the target frequency and the coarse-tuned VCO frequency, which is called coarse-tune frequency error, ∆f. Now VCO tune voltage is connected to PLL to close the PLL/VCO loop. Once locked, PLL corrects the tune voltage so that VCO frequency equals the target frequency, removing the coarse-tune error, ∆f. The amount of the tune voltage correction by PLL, ∆V, is a function of both the coarsetune frequency error, ∆f, and VCO fine-tune characteristic. frequency drift as VCO fine-tune frequency range. On the other hand, if PLL/VCO is locked at famb at Tamb (ambient temperature), VCO frequency can drop/rise by (famb - fhot)/ (fcold - famb) at hot/cold. Figure 4 illustrates VCO temperature frequency drift, optimum DFC tune voltage and VCO finetune characteristic at Tamb. Temperature frequency drift of VCO is assumed to be as big as VCO fine-tune frequency range. As shown, the VCO fine-tune characteristic of Fig. 4 suggests that at Tamb, there is an optimum VCO tune voltage, Vamb, at which if VCO is coarse-tuned, PLL can compensate for VCO frequency drop/rise of (famb-fhot)/ (fcold-famb) by increasing/decreasing tune voltage by (Vhot– Vamb)/(Vamb–Vcold). As depicted in Fig. 4, the optimum DFC tune voltage is a function of temperature so that it resembles the inverse function of VCO fine-tune characteristic. III. OPTIMUM TEMPERATURE ADAPTIVE TUNING In many applications such as 3G transceivers, once the tuning is finished and the coarse-tune word is selected, PLL must remain locked over the entire temperature range. Figure 3 shows the drift of VCO fine-tune curve over temperature which, for the illustration purpose, is equal to the fine-tune frequency range. After the completion of the tuning at fnom, if it gets hot (cold), VCO frequency drifts down (up) linearly over temperature [5]. To maintain the same target frequency of fnom, PLL has to increase (decrease) the tune voltage to make up for VCO frequency drift. The required tune voltage adjustment is a function of both VCO frequency drift over temperature and VCO fine-tune characteristic. The maximum tolerable VCO temperature frequency drift is set by DFC tune voltage. As illustrated in Fig. 3, if it is a fixed voltage [2]-[5], then to guarantee PLL locked condition, VCO temperature frequency drift has to be smaller than half the VCO fine-tune frequency range. Note that, if VCO is tuned at fcold (fhot), it becomes out of lock once temperature rises (drops) to nominal. Optimally PLL/VCO can remain locked in the presence of as big VCO temperature frequency drift as VCO finetune frequency range if DFC tune voltage is set properly. Contemplating on Fig. 3, if DFC tune voltage, ‘dfc_vtune’, is a function of temperature such that it changes from the minimum PLL tune voltage at cold to the maximum PLL tune voltage at hot, then once PLL/VCO is locked at hot/cold, it remains locked despite as high VCO temperature IV. DESIGN AND CIRCUIT IMPLEMENTATION dfc_vtune Optimum DFC tune voltage would be a linear function of temperature only and only if VCO fine-tune characteristic is linear. Linear VCO fine-tune characteristic results in a constant VCO gain (KVCO) over entire tune voltage range, making PLL bandwidth independent of tune voltage. Moreover, in circuit level, a linear DFC tune voltage can be implemented more accurately. These motivated us to design a fairly linear VCO fine-tune characteristic using identical MOS varacors biased at different voltages [6]. 3960 3950 Frequency (MHz) 3940 3930 fcold 3920 fnom 3910 3900 3890 fhot 3880 3870 3860 3850 3840 0.15 0.25 0.35 0.45 0.55 0.65 0.75 0.85 0.95 1.05 1.15 1.25 1.35 Tune Voltage (V) Nominal Fig. 3. 2 Cold Hot Drift of VCO fine-tune curve over temperature 3950 1.2 3940 3930 fcold fcold- famb 0.9 0.75 famb Vamb 0.6 0.45 Tamb 0.3 -20 -10 0 10 20 30 40 50 60 70 Temperature (ºC) VCO Frequency Drift Optimum DFC Tune Voltage Fig. 4. 3910 fcold- famb 3900 Vcold 3880 fhot 0.15 -30 3920 3890 fhot- famb Vhot fhot- famb Vamb 1.05 Frequency (MHz) DFC Tune Voltage (V) 1.35 Vhot - Vamb Vamb - Vcold 3870 80 0.15 0.25 0.35 0.45 0.55 0.65 0.75 0.85 0.95 1.05 1.15 1.25 1.35 Tune Voltage (V) VCO Fine-Tune VCO temperature frequency drift, VCO fine-tune curve at ambient temperature, Tamb , and the optimum DFC tune voltage The idea is implemented in the RX VCO of [1]. With an 8-bit coarse-tune capacitor array, VCO covers from 3.15GHz to 4.60GHz to guarantee the required frequency coverage of 3.45GHz to 4.35GHz over PVT. Using linear DFC tune voltage vs. temperature, VCO remains locked despite temperature frequency drift of about VCO gain. For instance, while exhibiting gain of 50MHz/V at 3.90GHz, VCO remains locked despite 45MHz frequency drift over [-30ºC, 85ºC]. In Section III, for illustration purpose, we neglected the coarse-tune resolution and the uncertainty of the DFC tune voltage which both call for a smaller tolerable temperature frequency drift than VCO fine-tune frequency range. The tune voltage equivalent of the coarse-tune resolution of the design is about ±100mV across the frequency range. On the other hand, due to mainly mismatch, though linear with temperature, the DFC tune voltage would fall within a ±100mV (±3σ) wide channel, further reducing effective PLL tune voltage range. Both VCO and PLL operate at 1.60V supply voltage, enabling 1.3V (0.15V to 1.45V) PLL tune voltage range. However, the effective PLL tune voltage range would be shrunk to 0.9V (0.35V to 1.25V) by the explained non-idealities. Therefore the design should be targeted to construct a DFC tune voltage which linearly varies from 0.35V to 1.25V over [-30ºC, 85ºC]. If PLL is locked at -30ºC (85ºC), due to the coarse-tune resolution of ±100mV and the DFC tune voltage uncertainty of ±100mV, the PLL tune voltage can be as low as 0.15V (1.05V) and as high as 0.55V (1.45V), leaving 0.9V (45MHz at 3.90GHz) for the VCO temperature frequency shift. B. Design Considerations and Measurement Results Percentage wise, the uncertainty of the PTAT current is very small. However the excessive offset of the PTAT current which is canceled out by constant current, would elevate the absolute uncertainty of the DFC tune voltage considerably. The uncertainty of the constant current would contribute to that as well. For the designed circuit, although 3σ of PTAT current is only 3%, that of the DFC tune voltage is less than 100mV (smaller in lower voltage). The tune voltage equivalent of the coarse-tune resolution has to be relatively small over the entire frequency and temperature ranges. Figure 6 shows the PLL tune voltage at -30ºC, 27ºC and 85ºC when the target frequency sweeps the entire frequency range in 2MHz steps. As illustrated, the measured coarse-tune error is limited to ±100mV. Figure 6 also confirms the linearity and the correct coverage of the DFC tune voltage over temperature. Figure 7 depicts the PLL tune voltage deviation due to temperature after VCO is tuned at 3.90GHz, first tuned at -30ºC and then at 85ºC. To Maintain the locked condition over [-30ºC, 85ºC], PLL adjusts the tune voltage to make up for the VCO temperature frequency drift. Note that at both -30ºC and 85ºC, VCO is coarse-tuned to the same coarsetune curve (code) but at two different DFC tune voltage values which is the indicative of VCO fine-tune characteristic being compensated by DFC tune voltage. Figure 7 also resembles the inverse function of a fairly linear A. DFC Tune Voltage Circuit Figure 5 shows the proposed circuit to construct such a linear DFC tune voltage. The proportional to absolute temperature (PTAT) current, Iptat, of the already existing BandGap voltage generator, provides the linearity vs. temperature component. However, since the PTAT current is proportional to absolute temperature, a constant current, Iconst, should be subtracted to compensate for the excessive positive offset of the PTAT current. Fig. 5. 3 The proposed circuit to construct DFC tune voltage [5] T. Tanzawa et al., “A temperature-compensated CMOS LCVCO enabling the direct modulation architecture in 2.4GHz GFSK transmitter,” IEEE CICC Dig., pp. 273-276, Oct. 2004 [6] J. Mira et al., “Distributed MOS varactor biasing for VCO gain equalization in 0.13 µm CMOS technology,” IEEE RFIC Symp. Dig., pp. 131-134, June 2004 VCO fine-tune characteristic at 3.90GHz. Figure 8 shows VCO phase noise, at 3.9GHz, after passing through a driver. Covering from 3.15GHz to 4.16GHz, VCO draws 8.5mA from 1.60V supply to achieve phase noise of -138dBc/Hz at 3.0MHz at 3.90GHz. The RX VCO location in chip photograph is shown in Fig. 9. Table 1, summarizes the VCO measurement results. Utilizing an on-chip inductor of 0.13u CMOS process, it comfortably meets the receiver path requirements of the backward compatible 3G SAW-less transceiver [1]. V. CONCLUSION A modified tuning scheme for wide-range VCO is presented. It optimizes the maximum tolerable VCO temperature frequency drift by allowing it to be as big as VCO fine-tune frequency range. It facilitates the design of a wide-range VCO with a small gain which reduces VCO sensitivity to noise of PLL tune voltage and supply. The method is implemented in the RX wide-range VCO of a multi-band multi-standard transceiver. Fig. 7. PLL tune voltage adjustment due to temperature, after VCO is tuned at 3.90GHz first at -30ºC and then at 85ºC ACKNOWLEDGEMENT The authors gratefully acknowledge the support of the entire Skyworks Solutions, Inc, Mobile Transceiver team. REFERENCES [1] T. Sowlati et al.,“Single-chip multi-band WCDMA/HSDPA /HSUPA/EGPRS transceiver with diversity receiver and 3G DigRF interface without SAW filter in transmitter/3G receiver paths,” IEEE ISSCC Dig. Tech. Papers, pp. 116117, 117a, February 2009 [2] L. S. L. Loke et al., “A versatile 90-nm CMOS chargepump PLL for SerDes transmitter clocking,” IEEE J. SolidState Circuits, vol. 41, no. 8, pp. 1894-1907, August 2006 [3] L. Daniel et al., “A single-chip tri-band (2100, 1900, 850/800 MHz) WCDMA/HSDPA cellular transceiver,” IEEE J. Solid-State Circuits, vol. 41, no. 5, pp. 1122-1132, May 2006 [4] Kun-Seok Lee et al., “A 0.13-µm CMOS Σ-∆ frequency synthesizer with an area optimizing LPF, fast AFC time, and a wideband VCO for WCDMA/GSM/GPRS/EDGE applications,” IEEE RFIC Symp. Dig., pp. 299-302, June 2008 Fig. 8. VCO phase noise after passing through a driver Fig. 9. RX VCO in chip photograph Table 1. VCO Measurement Summary Fig. 6. PLL tune voltage across frequency and temperature 4 Power Supply / Current 1.60V / 8.5mA Frequency Range 3.15GHz ~ 4.60GHz VCO Gain (tune voltage: [0.15V, 1.35V]) 50MHz/V ± 15% @ 3.9GHz Frequency Drift over [-30ºC,85ºC] 45MHz @ 3.90GHz Phase Noise -138dBc/Hz @ 3.9GHz @ 3 MHz Power Supply Pushing (no LDO) 3MH/V @ 3.9GHz @ DC