File - Pishtoy Engineering

advertisement

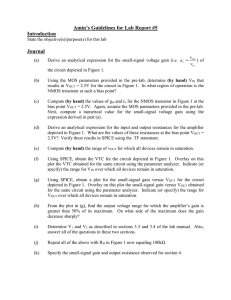

Bogdan Pishtoy Lab Partner: Roman Vermenchuk EEE 108L – Section 04 Lab Dates: 03/18/15 & 04/08/15 Due Date: 04/15/2015 Laboratory Experiment 5: Diode Circuits By: Bogdan Pishtoy 1 Procedures: In this lab, we will experiment with diode characteristics and the ideal diode equations we learned from lecture. This is our first semiconductor device which we will be experimenting with. The diodes used in this experiment were Zener diodes. Figure 1: Diode Circuit Preliminary Calculations: For detailed theoretical analysis and calculations, please see the Appendix A: Engineering Notebook attachment. The calculations include majority carrier concentration, the built in potential, MATLAB data calculating rd, the small-signal resistance, with various diode voltages, expressions for the diode current, and a small-signal gain expression. Note: The engineering notebook attachment also includes Conclusion Items 1 and 2. SPICE simulations: Step 4: Next, we entered the circuit from Figure 2 below into SPICE. We entered the following parameters for our circuit elements and enabled a bias point analysis. Table 1: Simulation circuit element parameters VS (V) VBIAS (V) R (Ω) 0.00 6.00 238.8 2 Figure 2: Bias point analysis of the diode circuit Comparing the simulated diode bias current to the value from the relationship in Step 2, we used the relationship in Step 2: 𝐼𝐷 = 𝑉𝐵𝐼𝐴𝑆 − 0.7 6.0 − 0.7 = = 561.274 𝜇𝐴 2 ∗ 𝑅𝐵𝐼𝐴𝑆 + 𝑅 2 ∗ 4.602 ∗ 103 + 238.8 … 𝐸𝑞𝑢𝑎𝑡𝑖𝑜𝑛 (1) We averaged the two currents ID1 and ID2 from our simulated results, since they weren’t exactly identical. Thus our results were: Table 2: Theoretical and simulated bias currents Theoretical (μA) Simulated (μA) Percent Error (%) 561.274 546.95 2.55 Next, we performed a transient analysis now with Vs = 50 mVpp, RS = 50 Ω, VBIAS = 6V. To get a reasonably good looking waveform, we set our final time to 4 x 10-4 seconds with a step ceiling of 2 x 10-6 seconds. We will need to find the gain from our waveforms in Figure 3. VOUT = 43.562 Vpp VIN = 74.380 Vpp Figure 3: Transient analysis of VOUT and VIN Step 5: Gain of a waveform, according to Appendix 3.1 [1]: 3 𝐴𝑣 ≡ 𝑉𝑜𝑢𝑡 𝑝𝑝 43.562 = = 0.5857 𝑉𝑖𝑛 𝑝𝑝 74.380 … 𝐸𝑞𝑢𝑎𝑡𝑖𝑜𝑛 (2) a) Value of rd that equals the calculated gain. From the equation in Step 3 and equation 2: 𝑉𝑂𝑈𝑇 𝑅 = = 0.5857 … 𝐸𝑞𝑢𝑎𝑡𝑖𝑜𝑛 (3) 𝑉𝐼𝑁 2 ∗ 𝑟𝑑 + 𝑅 With R = 238.8 Ω, and solving for rd: 1 𝑅 238.8 𝑟𝑑 = ( − 𝑅) = 0.5 ∗ ( − 238.8) = 84.4586 Ω … 𝐸𝑞𝑢𝑎𝑡𝑖𝑜𝑛 (4) 𝑉 2 𝑂𝑈𝑇 0.5857 𝑉𝐼𝑁 b) Value of n, 1 ≤ n ≤ 2, for our value of rd: 𝑛𝑉𝑇 𝑟𝑑 = … 𝐸𝑞𝑢𝑎𝑡𝑖𝑜𝑛 (5) 𝐼𝐷 And from equation 1, 𝑉𝐵𝐼𝐴𝑆 − 0.7 6.0 − 0.7 𝐼𝐷 = = = 561.274 𝜇𝐴 2 ∗ 𝑅𝐵𝐼𝐴𝑆 + 𝑅 2 ∗ 4.602 ∗ 103 + 238.8 With VT ≈ 25.85 mV and solving for n: 𝑟𝑑 ∗ 𝐼𝐷 84.4586 ∗ 561.274 ∗ 10−6 𝑛= = = 1.834 𝑉𝑇 25.85 ∗ 10−3 “The ideality factor n is a measure of how much of the diodes current is due to electron-hole recombination in its depletion region” [2]. Firstly this value of n seems reasonable since our value of n is 1 ≤ n ≤ 2. And secondly, the SPICE model for the 1N4148 uses n = 1.836, so we are spot on. Step 6: Trying different values of VBIAS, we measured the gain, and tabulated our data. Again, the gain was measured using the peak to peak voltages. Table 3: VBIAS and gain data Vbias (V) 10.0 9.0 8.0 7.0 6.0 5.0 4.0 3.0 2.0 1.0 Gain (mV/mV) 0.7153 0.6911 0.6624 0.6279 0.5857 0.5326 0.4638 0.3702 0.2317 0.0471 The relationship between VBIAS and the gain is directly proportional. Meaning, as VBIAS increases, the gain also increases. The small signal gain changes because as the bias voltage is increased, the small-signal resistance decreases, allowing for more current to flow. And since we 4 are in small-signal analysis, we are assuming the input voltage V IN does not change much. Thus with an increasing VOUT and a fairly constant VIN, the gain increases. Next, we will move on to the actual hands on lab experiment. Part I: Circuit Construction and Small-Signal Behavior Next for Step 7, we constructed the circuit of Figure 1. Using two Zener 1N4148 diodes, two resistors R measured at 238.8 Ω, RBIAS measured at 4.602 kΩ, and VBIAS set to 6.0 V, we constructed the circuit. With no AC signal applied from the function generator, we verified that VIN and VOUT were with ±5 mV of each other. The way to do this, we kept trying to find two diodes that had a similar built in voltage. Measuring in DC, our results were from the Digital Multimeter were: 𝑉𝐷1 = 0.1351 𝑉 𝑎𝑛𝑑 𝑉𝐷2 = 0.1385 𝑉 Thus, our diodes were 3.40 mV from each other. For Step 8, we adjusted the function generator so that VIN is a triangle waveform measured at 160 mVpp at 10 kHz. As we varied VBIAS, we noticed that VIN slightly changed, but VOUT had more noticeable changes. In AC coupling mode, VIN seemed to increase slightly as we varied VBIAS. VOUT decreased in amplitude as VBIAS decreased. As seen in Figure 4 below, VIN is of larger magnitude and would stay fair constant as VBIAS was varied. In DC coupling mode, VIN shifted down and left indicating that a DC offset is present. VOUT seemed to have the same results as in AC coupling mode. As VBIAS was decreased, VOUT decreased in amplitude as well. VIN slightly increased as VBIAS was increased. After a quick measure with the cursors, we noted that VIN changed from 155 mVpp to 167 mVpp. VIN = 160 mVpp at 10 kHz VOUT = 100 mVpp at 10 kHz Figure 4: VIN and VOUT in AC coupling mode 5 The relationship found in Step 6 was that VBIAS and the gain are proportional to each other. This relationship still holds true for both AC and DC coupling modes. Again, this relationship holds because VIN varies slightly while VOUT changes more drastically. Next for Step 9, we repeated Step 5 and calculated the gain, rd, and the ideality factor n, but this time with our measured values. Using the equation 2 and referring to Figure 4: 𝐴𝑣 ≡ 𝑉𝑜𝑢𝑡 𝑝𝑝 100.0 = = 0.625 𝑉𝑖𝑛 𝑝𝑝 160.0 And now calculating rd: 1 𝑅 238.8 ( − 𝑅) = 0.5 ∗ ( − 238.8) = 71.64 Ω 𝑉 2 𝑂𝑈𝑇 0.625 𝑉𝐼𝑁 𝑟𝑑 = To get ID to calculate our ideality factor n, we used our equation from Step 2. But this time, we measured the voltage drop VD across the diode. 𝐼𝐷 = 𝑉𝐵𝐼𝐴𝑆 − 𝑉𝐷 6.0 − 0.583 = = 573.665 𝜇𝐴 2 ∗ 𝑅𝐵𝐼𝐴𝑆 + 𝑅 2 ∗ 4.602 ∗ 103 + 238.8 𝑛= 𝑟𝑑 ∗ 𝐼𝐷 71.64 ∗ 573.665 ∗ 10−6 = = 1.590 𝑉𝑇 25.85 ∗ 10−3 And now for Step 10 to observe only the effects of VBIAS on the AC signal, both channels were AC coupled. Varying VBIAS, we recorded our values of VOUT and VIN and tabulted them below. Table 4: VOUT and VIN in response to VBIAS Vbias 0.0 0.2 0.4 0.6 0.8 1.0 2.0 3.0 4.0 5.0 6.0 7.0 8.0 9.0 10.0 Amp for Vin (mV) 30.0 30.0 29.2 29.0 28.8 30.0 28.0 28.0 28.0 27.7 26.6 26.6 26.6 26.6 26.6 Amp for Vout (mV) 19.0 20.0 22.0 24.0 28.0 34.0 63.0 86.0 104.0 114.0 122.0 132.0 136.0 142.0 144.0 Vout/Vin 0.6333 0.6667 0.7534 0.8276 0.9722 1.1333 2.2500 3.0714 3.7143 4.1155 4.5865 4.9624 5.1128 5.3383 5.4135 6 Notice that we took more data points between zero and unity gain which were the two extremes disovered from Step 3 calculations. For a better understanding, we’ve plotted the data points. As seen in Figure 5 below, the relationship between the biased voltage and gain is almost linear, and from our data points would probably be best represented by an exponential or polynomial of a higher order. But roughly speaking, the relationship is linear or proportional. 1.2000 VBIAS vs Gain 1.0000 y = 0.4987x + 0.5817 Gain 0.8000 0.6000 0.4000 0.2000 0.0000 0.0 0.2 0.4 0.6 0.8 1.0 VBIAS (V) Figure 5: Plot of VBIAS vs Gain After acquiring the small-signal resistance and behavior of our gain at small signals, we’ll now take a look at the bigger picture of what happens in our diode circuit. Part II: Large-Signal Behavior Step 11: Firstly, we made sure that the oscilloscope is in DC coupling. Then with VBIAS set to 4 V, we increased the input signal VIN until VOUT showed clipping at the top and bottom peaks. It is worth mentioning that we observed that the waveform had symmetrical clipping at both peaks. Also, we observed that at lower values of VBIAS, the clipping of peaks at VOUT would occur more noticeably. At higher values of VBIAS, the clipping would happen at greater amplitudes of the input signal meaning it would take a larger input signal to observe distinct clipping. We recorded down several clipping levels at certain biased voltages and tabulated our data. From Table 5 and Figure 6 below, we noticed that the clipping levels are also somewhat proportional to the biased voltage. The clipping would clip the peak voltages of VOUT as seen below. 7 Table 5: VBIAS and clipping levels Vbias (V) 6.00 5.00 4.00 3.00 2.00 1.00 ( + ) clip level 450.00 400.00 330.00 280.00 240.00 190.00 ( - ) clip level 450.00 400.00 330.00 280.00 240.00 190.00 Figure 6: Clipping of VOUT as VBIAS changes Conclusion Item 3: Assuming the constant voltage drop model of VD to be 0.7 V, the short circuit current at or above this voltage, and the open circuit current below VD the data in Table 5 is easy to explain. The clippings occur due to one of the diodes being in reverse bias, and therefore “off” according to our model with no current flow. In fact, VOUT would clip as soon as the gain would go above 1. Conclusion Item 4: The large signal model cannot be used to calculate the small-signal gain because the small-signal gain assumes very small changes in VIN as VOUT is changing. In the large-signal model, one would have to record both VIN and VOUT when calculating the gain because VIN would have a wider range of values. To calculate the small-signal gain, the small-signal resistance would have to be known, according to equation 3 from Step 5. The concept of large-signal would not work for this equation because the large signal isn’t linear and clips at both peaks. Conclusion Item 5: The small-signal model can however be used to calculate output clipping levels by looking at the small-signal resistance rd or the gain. If rd has become negative, this indicates that the output is in saturation and has clipped. This happens when the gain is greater than 1, in accordance with equation 4. Also, if the gain is nearing 0, this also indicates that we have reached the negative clipping level of the output. In equation 4, a gain of 0 would mean infinite resistance making the diodes act like open circuits. Step 12: With the oscilloscope still in DC coupling mode, we turned on the X-Y graphing mode. The shape of the resulting graph can be seen in Figure 7 below. VIN and VOUT have a linear region of operation as well as a non-linear region where clipping (saturation) occurs. Varying VBIAS, we noticed that the gain is proportional to the gain in the linear region. This is ∆𝑉 because the slope of the sketch in Figure 7 is the gain, ∆𝑉𝑂𝑈𝑇 . 𝐼𝑁 8 ( + ) clipping level at 330 mVpp VOUT (V) Linear region of operation from -165 mV to 165 mV with VBIAS at 4 V. ( - ) clipping level at 330 mVpp VIN (V) Figure 7: Sketch of X-Y plot with VOUT and VIN Step 13: With VIN set to a triangle wave at 1 Vpp, we found the value of VBIAS that made the output voltage look like a sinusoid. VBIAS was 6.0 V which made VOUT become a distinct sine wave. VIN at 1 Vpp VOUT at 0.375 Vpp Figure 8: Triangle to sine wave converter Conclusion Item 6: 𝑉 The large signal model 𝐼𝐷 = 𝐼𝑠 ∗ exp (𝑛𝑉𝐷 ) was not used to calculate the diode bias currents. It 𝑇 can be used for this purpose, but it is hard to measure the reverse bias current IS and a voltage drop would have to be assumed for VD. Including the ideality factor, this leads to too many unknowns. The small-signal analysis seems to be the easiest way to calculate the bias current, and we know that the current in small-signal analysis remains a fairly good assumption in largesignal analysis. 9 References [1] R. Tatro, “Appendix 3: Amplifier Gain and Frequency Response Measurement,” Sacramento State University, Sacramento, CA, 2015. [2] R. Tatro, “Lab 5 – Diode Circuits,” Sacramento State University, Sacramento, CA, 2015. 10