Analog Dialogue- Ask The Applications Engineer 24

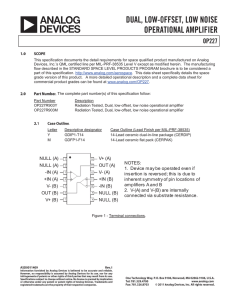

advertisement