WiRElESS iCs

volume 6, issue 6

Y o u R

F E at u R E d a Rt i C l E S

New Family of Pin-Compatible Modulators delivers Best

Performance and value from 250 MHz to 4000 MHz

DC to GHz Multiplier Delivers

Gain and Modulation Control . . . . . . Predrivers Minimize Need for

External Components . . . . . . . . . . . . . . . Clock ICs for RF . . . . . . . . . . . . . . . . . . . . . . LF to 4 GHz Y-Mixer Enables Low

Power Portable Applications . . . . . . . 4

Ultrafast Hopping PLL Facilitates

Frequency Agility . . . . . . . . . . . . . . . . . . . . . 4

Dual-Channel DDS for Ultraprecise

I/Q Data Generation . . . . . . . . . . . . . . . . . 5

Complete ADI Signal Chain Solutions

for Wireless Infrastructure . . . . . . . . . 6

Ultralow Distortion Differential Amp

Reduces System Cost . . . . . . . . . . . . . . 8

16-Bit, High Speed ADCs

Offer Low Power and Higher

Sampling Rates . . . . . . . . . . . . . . . . . . . . . . 9

Power Accurate RF Measurement

and Control in a Small Package . . 10

RF Detectors Satisfy Range,

Frequency, and Size

Requirements . . . . . . . . . . . . . . . . . . . . . . . . 10

Quad Band Radio Transceiver

for EDGE, GSM, and GPRS . . . . . . . 11

S E M i C o N d u C t o R

S o l u t i o N S

R E S o u R C E

S

electing a single broadband direct conversion modulator to handle the

multitude of frequency bands used in wireless and broadband communications networks results in many trade-offs and performance degradation

at the extreme ends of the device operating frequency. These performance

trade-offs are further compromised by part to part and temperature variations.

FREE

oFFE

See R

insid

e

for

detai

ls

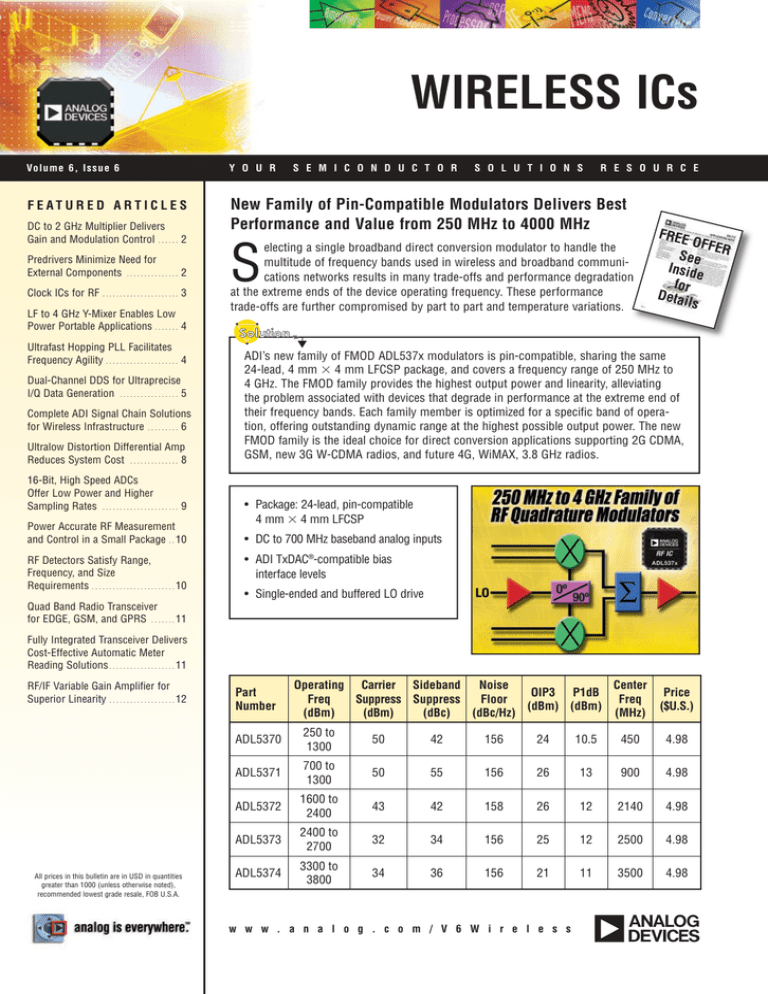

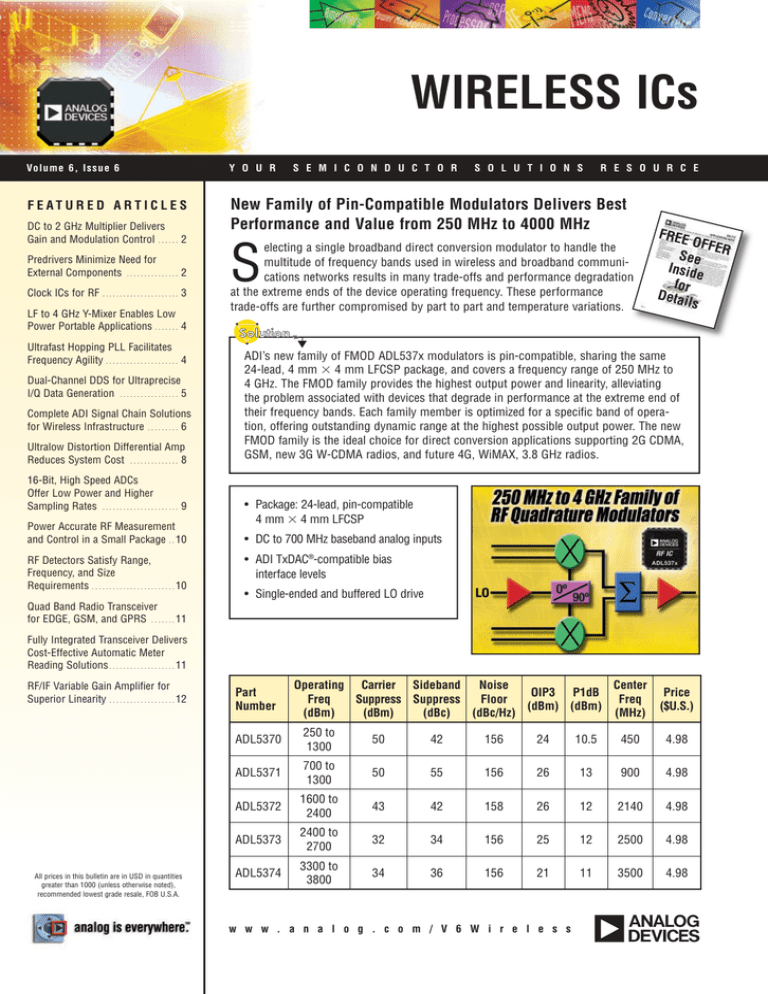

ADI’s new family of FMOD ADL57x modulators is pin-compatible, sharing the same

4-lead, 4 mm 4 mm LFCSP package, and covers a frequency range of 50 MHz to

4 GHz. The FMOD family provides the highest output power and linearity, alleviating

the problem associated with devices that degrade in performance at the extreme end of

their frequency bands. Each family member is optimized for a specific band of operation, offering outstanding dynamic range at the highest possible output power. The new

FMOD family is the ideal choice for direct conversion applications supporting G CDMA,

GSM, new G W-CDMA radios, and future 4G, WiMAX, .8 GHz radios.

• Package: 4-lead, pin-compatible

4 mm 4 mm LFCSP

• DC to 700 MHz baseband analog inputs

• ADI TxDAC®-compatible bias

interface levels

• Single-ended and buffered LO drive

Fully Integrated Transceiver Delivers

Cost-Effective Automatic Meter

Reading Solutions . . . . . . . . . . . . . . . . . . . 11

RF/IF Variable Gain Amplifier for

Superior Linearity . . . . . . . . . . . . . . . . . . . 1

All prices in this bulletin are in USD in quantities

greater than 1000 (unless otherwise noted),

recommended lowest grade resale, FOB U.S.A.

Part

Number

operating Carrier Sideband Noise

Center

oiP3 P1dB

Freq

Suppress Suppress

Floor

Freq

(dBm) (dBm)

(dBm)

(dBm)

(dBc)

(dBc/Hz)

(MHz)

Price

($u.S.)

ADL570

50 to

100

50

4

156

4

10.5

450

4.98

ADL571

700 to

100

50

55

156

6

1

900

4.98

ADL57

1600 to

400

4

4

158

6

1

140

4.98

ADL57

400 to

700

4

156

5

1

500

4.98

ADL574

00 to

800

4

6

156

1

11

500

4.98

w w w . a n a l o g . c o m / v 6 W i r e l e s s

DC to 2 GHz Analog Multiplier Delivers Gain and Modulation Control Within

Wideband Communications Applications

R

equirements to multiply high frequency analog signals for gain and modulation control within wideband communications applications such as adaptive antenna systems and power amplifier correction circuits have been made practical

with the ADL5391. The ADL5391 allows fully symmetrical linear control of the three input interfaces: X, Y, and Z.

The Z input allows an offset signal to be added directly to the

output, which could be used to cancel a carrier or apply a

static offset voltage.

The ADL5391 is a very versatile analog circuit that is

represented by the following equation: W = aXY/1V + Z.

The gain scaling “a” is adjustable through the GADJ control

input. Multiple ADL5391 devices can be connected together

to form polynomial multiplication and synthesis.

• Operation from dc to 2 GHz

• Identical X and Y amplitude/timing responses

• Adjustable gain scaling and control

• Power: single 5 V supply

• Package: small, 3 mm 3 mm LFCSP

ADL5391

$4.89

Matched RF Predrivers Minimize Need for External Components

O

n the final stage of the transmitter, the driver amplifier needs to be very linear. Furthermore, the gain and output

power of the amplifier should hold within a respectable tolerance so that the drift over temperature and supply

voltage does not need to be adjusted by the RF attenuators.

ADL5322/ADL5323

• Gain stable vs. temperature: 0.5 dB

The new ADL5322 and ADL5323 are tuned RF amplifiers that integrate

on-chip the input and output matching networks to minimize the needs

of external components.

• Frequency 0.25 dB in-band

• OIP3: 42 dBm

• OP1dB: 28 dBm

These 1/2 watt predrivers are tuned for cellular bands of operation: the

ADL5322 for the 700 MHz to 1000 MHz bands and the ADL5323 for the

higher bands of 1700 MHz to 2400 MHz. Both amplifiers are pincompatible and provide nominal gain of 20 dB.

• Noise figure: 4 dB

• Price: $3.48 (ADL5322)

$3.48 (ADL5323)

Comparison vs. Alternative Traditional Products

Old Way

New Way

VC

Alternative products based on

4-lead SOT-89 utilize significantly

more board area and many external

discrete matching components

RFIN

C5

L1

3 GND

GND 7

2 VCC

ADL5322

1 VCC

The ADL5322 and ADL5323

need only external

coupling capacitors

C6

Y o u r

4 RFOUT

3mm

C7

Z-50 � EL3

BIAS CONTROL

GND 6

RFIN 8

C3

2.5mm

Z-50 � EL1

3mm

C2

4.5mm

C4

VCC 5

C1

S e m i c o n d u c t o r

S o l u t i o n s

R e s o u r c e

ADI Clock ICs for RF Applications

A

nalog Devices offers ultralow jitter clock distribution and clock generation products for wireless infrastructure,

instrumentation, broadband, ATE, and other applications demanding subpicosecond jitter performance. ADI clock

products support output frequencies up to 1.6 GHz and deliver low jitter, low phase noise, and low spurs, making

them ideal for clocking high performance analog-to-digital converters (ADCs) and digital-to-analog converters (DACs).

Integrated PLL cores, dividers, phase offset, skew adjust, and clock drivers in small chip scale packages, reduced BOM

(bill of materials), and board space savings can be realized.

For more information, please visit www.analog.com/clocks.

Part

Number

Output Clocks

(MHz)

Number

Outputs and

Logic Family

View our on demand technical seminar,

“Performance Clocks: Demystifying Jitter”

at www.analog.com/onlineseminars.

Wideband

Random Jitter

(rms fs)

Description

Package

Price

($U.S.)

Clock Distribution—programmable dividers (1 to 32), phase offset, adjustable delay blocks

AD9510

1200/800/250

4 LVPECL

4 LVDS/CMOS

225 additive

1.6 GHz PLL core, 8-output

clock distribution

64-lead

LFCSP

11.95

AD9511

1200/800/250

3 LVPECL

2 LVDS/CMOS

225 additive

1.6 GHz PLL core, 5-output

clock distribution

48-lead

LFCSP

9.95

AD9512

1200/800/250

3 LVPECL

2 LVDS/CMOS

225 additive

5-output clock distribution

48-lead

LFCSP

8.95

AD9513

800/250

3 LVDS/

CMOS

300 additive

Pin-programmable, 3-output

clock distribution

32-lead

LFCSP

5.95

AD9514

1600/800/250

2 LVPECL

1 LVDS/CMOS

225 additive

Pin-programmable, 3-output

clock distribution

32-lead

LFCSP

5.95

AD9515

1600/800/250

1 LVPECL

1 LVDS/CMOS

225 additive

Pin-programmable, 2-output

clock distribution

32-lead

LFCSP

4.75

655 MHz, low jitter clock

generator

48-lead

LFCSP

9.95

Clock Generation—programmable clock rates and edge delay

AD9540

1 CML, PECLcompliant

655

700 total

ADI now enables clock and timing engineers

to rapidly develop, evaluate, and optimize

designs using the new ADIsimCLK™ tool,

for use with ADI’s family of ultralow jitter

clock distribution products. By using

the tool’s tutorials, design wizards, and

user-friendly data entry screens, designers

can now create complete, robust timing

solutions in minutes.

Available for free download at

www.analog.com/ADIsimCLK.

w

w

w

.

a

n

a

l

o

g

.

c

o

m

/

V

6

W

i

r

e

l

e

s

s

High Linearity LF to 4 GHz Y-Mixer Enables Low Power Portable Applications

F

inding a high linearity mixer for power sensitive portable applications has been a constant challenge. There are many

low power passive and active mixers on the market. However, providing high sensitivity and blocker immunity requires

high linearity, which then places the burden on providing a high LO drive into the mixer.

The new ADL5350 provides high linearity (26 dBm input IP3) and draws just 10 mA of supply current on 3 V supply.

These specifications have been made possible by integrating an on-chip LO drive amplifier that requires just 4 dBm

LO drive compared to 17 dBm drive for equivalent linearity mixers. The ADL5350 is a passive FET-based mixer with an

active LO driver that can be used for both down- and upconversion over a broad input frequency range, making the part

ideally suited for use in congested spectrum applications.

• Broadband RF, IF, and LO ports

GND

RF

INPUT OR

OUTPUT

• Conversion loss: 6 dB

• Noise figure: 6 dB

IF

RF

• High input IP3: 26 dBm

IF

OUTPUT OR

INPUT

ADL5350

GC

• High input P1dB: 17 dBm

3V

• Low LO drive level

GND

VPOS

• Single-ended design: no need for baluns

• Single-supply operation: 3 V @ 10 mA

LO

LO

INPUT

ADL5350

$2.36

Ultrafast Hopping PLL Where Frequency Agility Is Critical

F

ast hopping systems require ultra-agile PLLs that can settle to the desired phase and frequency in microseconds.

For example, GSM/EDGE base stations require synthesizers that can frequency hop over the full 75 MHz Tx or Rx

band in 10 s with very low phase noise and spurious. To date, these

conflicting requirements can only be accomplished using a costly “pingSSB PHASE NoISE

pong” architecture, where one synthesizer is locking to the next desired

frequency while the other is active as the LO. ADI’s ADF4193 fast switching

synthesizer can meet all these same requirements with a single PLL.

This decreases cost, complexity, PCB area, shielding, and characterization

costs compared to ping-pong GSM PLL architectures. The ADF4193 can

reduce the bill of material for these systems by up to 50%.

At right and below are some measured results for ADF4193 in a GSM

application. The phase settles to the final value in less than 20 s, and the

overall phase noise profiles shows less than 0.5 degree rms integrated

phase error at 2 GHz RF output frequency.

FREQUENCY SETTLING

PHASE SETTLING

To download the

ADIsimPLL—the

industry’s leading PLL

design and evaluation

software—go to

www.analog.com/PLL.

ADF4193

$10.00

Y o u r

S e m i c o n d u c t o r

S o l u t i o n s

R e s o u r c e

Dual-Channel DDS for Ultraprecise I/Q Data Generation

A

frustrating problem for designers seeking perfect quadrature in their communications systems can occur with

mismatching between the I and Q data streams. Even by confirming that the oscillator signals are exactly 90° out

of phase when they hit the modulator does not guarantee that the mixed I/Q data will reflect perfect quadrature.

This is due to internal mismatching that may occur within the analog modulator.

However, as long as the mismatch is consistent, a simple solution now exists. The new AD9958 dual-channel DDS (direct

digital synthesizer) provides independent frequency, phase, and amplitude control on each channel. This flexibility can be

used to correct the imbalances between quadrature signals due to analog processing like filtering, amplification, or PCBlayout-related mismatches. Both channels are controlled by the same system clock, so they are inherently synchronous.

The AD9958 boasts excellent channel-to-channel isolation (>72 dB). Each channel has dedicated 14-bit phase and 10-bit

amplitude programmability, which makes it easy to program the channels to perfect quadrature with precisely matched

amplitude. Slight changes to that exact 90° relationship and exact amplitude matching are also possible. With 14 bits of

programming resolution, the worst-case variation from perfect quadrature will be 90 0.01°.

By integrating two DDS channels on a single

chip, the AD9958 saves the designer board

space and helps reduce BOM costs. The fact

that the DDS channels are inherently synchronized translates into a simpler and less

time consuming design process. The single

chip solution also eliminates temperature

concerns that normally exist among multiple

chips. A 4-channel DDS, the AD9959, is

also available.

Using 2-Channel Synchronized DDS to

Achieve Near Perfect Quadrature

•2 synchronized DDS channels

@ 500 MSPS

Applications

•2 integrated 10-bit DACs

• Quadrature communications

AD9958

• >53 dBc wideband SFDR

• Agile local oscillator

• Consume <165 mW per channel

• Phased array radar/sonar

•32-bit frequency tuning resolution

• Synchronized clocking

• Instrumentation

• RF source for AOTF

• Package: 56-lead LFCSP

• Single-sideband suppressed carrier

For more information, please visit

www.analog.com/dds.

w

w

w

.

a

n

a

l

o

g

.

c

o

m

/

V

6

W

i

r

e

l

e

s

s

$20.14

Complete Signal Chain Solution for

A

nalog is everywhere for your cellular base station, broadband wireless, and WiMAX 802.16 design.

With the release of its new FMOD family of modulators and supporting predrivers, Analog Devices

offers high performance ICs for the entire wireless signal chain.

Now you can go from bits to RF at any frequency with a wireless signal chain made from high performance

Analog Devices components.

Predrivers

Power

Detectors

ADCs

FMODs

PLL

DDS

Synthesizers Synthesizers

ADL5322

AD8361

AD7457

ADL5370

ADF4106

AD9850

ADL5323

AD8362

AD7452

ADL5371

ADF4153

AD9851

ADL5501

AD7453

ADL5372

ADF4360

AD9911

AD8319

AD7910

ADL5373

ADF4108

AD9951

AD8318

AD7467

ADL5374

ADF4156

AD9958

AD8317

AD7911

ADF4193

AD9959

AD7921

AD7922

Y o u r

S e m i c o n d u c t o r

S o l u t i o n s

R e s o u r c e

Wireless Infrastructure from Analog Devices

TxDAC

Clocks

DUC/

QDUC

Signal Processing

and Control

AD9779

AD9510

AD6623

TigerSHARC® 20

AD9778

AD9511

AD6633

AD9776

AD9512

AD9857

AD9513

AD9957

AD9514

AD9515

AD9540

w

w

w

.

a

n

a

l

o

g

.

c

o

m

/

V

6

W

i

r

e

l

e

s

s

Ultralow Distortion Differential Amplifier Reduces System Cost

I

n today’s demanding wireless applications, lowering the distortion level of the ADC driver is critical to improving system

performance at higher frequencies, as this helps maintain the quality of the spurious-free dynamic range (SFDR) and

signal-to-noise ratio (SNR) of the ADC.

Newer and higher resolution ADCs can sample higher IF frequencies such as 140 MHz to 240 MHz with sufficient SFDR.

Although existing differential amplifiers can provide excellent distortion performance at lower IFs, when used in single-stage

high IF receiver architectures, the performance rolls off typically beyond 100 MHz. The AD8352, an ultralow distortion differential amplifier, is designed to drive 12-bit to 16-bit ADCs at the highest practical intermediate frequencies (IF) used

within next generation 3G and 4G cellular and broadband WiMAX wireless infrastructure equipment. In fact, the AD8352 is

capable of maintaining exceptional performance when driving high speed ADCs up to 380 MHz, far exceeding the 100 MHz

achieved by previously released differential amplifiers. Pairing the ultralow distortion AD8352 with 12-bit and 14-bit ADCs

such as ADI’s AD9445, AD9246, and AD9233, which all feature outstanding SFDR and SNR performance, means that base

station designers suffer no degradation in signal processing performance. The ultralow distortion of the AD8352 at

higher operating frequencies (82 dBc HD3 at 180 MHz, as

shown in the bottom left chart) is achieved by a proprietary

internal cancellation scheme, and the use of XFCB-3™, ADI’s

specialized silicon germanium (SiGe), silicon on insulator

(SOI) process technology.

The AD8352 delivers high linearity (41 dBm OIP3 as shown

in the bottom right chart), draws only 37 mA of quiescent

current, and is packaged in a space-saving 3 mm 3 mm

LFCSP. Additionally, the AD8352 saves considerable design

time and adds flexibility by isolating the gain, allowing the

user to select the desired gain with one external resistor.

The gain isolation permits the user to change the gain independent of noise and input matching requirements.

AD8352

$3.49

Online seminar available on demand: “Driving

Precision Converters: How to Select the Best Voltage

Reference and Amplifier for Your ADC Application”

at www.analog.com/onlineseminars.

50

45

–60

40

–70

IP3 (dBm)

HARMONIC DISTORTION (dBc)

–50

–80

–90

AV = 10dB

AV = 15dB

35

30

AV = 6dB

25

20

–100

–110

15

0

50

100

150

200

250

300

350

10

400

0

50

100

FREQUENCY (MHz)

200

250

300

350 400

450

500

FREQUENCY (MHz)

Harmonic distortion vs. frequency

for 2V p-p into RL = 1k, AV = 10dB, 5V supply,

RG = 180, RD = 6.8k, CD = 0.1pF

Y o u r

150

OIP3 vs. frequency in dB, 2V p-p composite,

RL = 200 AV = 15dB, 10dB, and 6dB

S e m i c o n d u c t o r

S o l u t i o n s

R e s o u r c e

Extended 16-Bit High Speed ADC Family Offers Lower Power and Higher Sampling Rates

for IF-Sampling and Other Wideband, High Performance Applications

S

oftware-defined radio architectures, high performance communication instrumentation, base station infrastructure,

military radar, and imaging systems require wideband ADCs with superior SNR, exceptional linearity, and low enough

power to be used in multichannel high-PC-board density applications. With the increasing need for wider bandwidth

and faster data processing and higher resolution imaging, higher resolution converters with faster sampling rates, that deliver uncompromised dynamic performance, are required.

ADI is expanding its family of high performance 16-bit ADCs to offer higher sampling rates and lower power, with

true 16-bit accuracy, for single and multichannel radar, instrumentation, and imaging receivers. As with the previously

released converter family members, the AD9445 (14-bit, 105 MSPS/125 MSPS) and the AD9446 (16-bit, 80 MSPS/

100 MSPS) ADCs, the new 16-bit ADCs include an internal input buffer which greatly simplifies driving requirements

and isolates the ADC input.

The AD9460 (16-bit, 80 MSPS/105 MSPS) and AD9461 (16-bit, 130 MSPS) ADCs are pin-compatible to the AD9446

(100-bit TQFP package) and have 2 dB to 3 dB better SNR performance, and up to 10 dB better SFDR performance, as

compared to other 16-bit ADCs. A flexible, 2 V p-p to 4 V p-p input range allows users to optimize for SNR and SFDR in

both baseband and IF-sampling applications.

The AD9446 remains the leader in 16-bit SNR, achieving 84 dB SNR with a 4 V p-p input. The power dissipation of the

AD9446 is 1.6 W @ 80 MSPS, the AD9461 is 1.4 W @ 80 MSPS and 1.6 W @ 105 MSPS, and the AD9461 is 1.9 W @

130 MSPS.

The data outputs of the AD9460 and AD9461 are available in CMOS or LVDS formats with 800 MHz input bandwidth.

The 50 fs jitter is 30% better, and the 85 dB FS (@ 4 V p-p) noise floor is >7 dB better than other 16-bit ADCs, while

maintaining signal-to-noise ratios of 79 dB.

AD9460: SFDR and SNR Performance vs. Input Frequency

For more information on the AD9460,

visit www.analog.com/AD9460.

99

94

89

84

79

74

10

70

170

250

INPUT FREQUENCY (MHz)

AD9460-125 (3.8V p-p)

AD9460-125 (3.2V p-p)

AD9460-125 (2.25V p-p)

AD9460 (3.8V p-p) SNR

AD9460 (3.2V p-p) SNR

Applications

• Software-defined radio

AD9460-105

AD9460-80

AD9461-130

• Dynamic signal analyzers

• Spectrum analyzers

• Digitizers

• Military radar

• Medical imaging receivers

w

w

w

.

a

n

a

l

o

g

.

c

o

m

/

V

6

W

i

r

e

l

e

s

s

$56.67

$48.33

$65.00

Power Accurate RF Measurement and Control in a Small Package

T

he ADL5500 offers unrivaled temperature stability and accuracy while measuring the rms/TruPwr™ level of complex

waveforms used in 3G+ communication systems. The small size and high level of integration are additional features

that make the ADL5500 ideal for cellular handsets where size and power consumption are very critical. Not all customers are comfortable handling and manufacADL5501 25°C Ref vs. Input Level

turing their end products with such a small

1900MHz at –40°C, +85°C

device. To meet their requirements, ADI

85 °C Drift (dB)

has developed the ADL5501, which imple–40 °C Drift (dB)

3

ments these performance features of the

ADL5500 in a small 6-lead SC70 package

2

with a footprint of less than 2 mm 2 mm.

The ADL5501 offers increased flexibility by

1

including one pin for an optional external fil0

ter capacitor and another for an enable pin.

–1

• Temperature stability and accurate

measurement of rms power levels

–2

• Small 2 mm 2 mm footprint

–3

–20

Region with Zero

Drift Over Temperature

–15

–10

–5

0

5

10

15

RFIN (dBm)

• Highly integrated design with option

to add external filtering capacitance

Applications

•3G and 3G+ handsets

ADL5500

ADL5501

$0.90

$0.90

• WiMAX terminals

• Cellular base stations

RF Detectors that Satisfy Every Design Need Including Range, Frequency, and Size

A

OUTPUT (V)

ERROR IN dB

ccurate and temperature stable RF power detection and control is a common requirement across a wide variety of

applications. Some applications need wider dynamic range than others, some need higher frequencies of operation

and others need smaller sizes. The AD8318 was the first RF power detector to allow operation from 1 MHz to

8 GHz and provide 60 dB of dynamic range.

Industry acceptance of this part has been

45dB dynamic range 1db dynamic

exceptional, and it was determined there was

range over temperature

a further need for similar performance with

2

2

lower power consumption, smaller size, and

reduced cost. As a result, ADI produced the

1.5

1.75

AD8317 with 50 dB of dynamic range. The

1.5

1

latest in this series is the AD8319, which

0.5

1.25

provides greater than 40 dB of dynamic

range and is packaged in a 2 mm 3 mm

0

1

LFCSP package. The AD8319 operates from

–0.5

0.75

1 MHz to 10 GHz and only consumes

±1dB OF DYNAMIC

RANGE OVER

–1

0.50

22 mA of current. The customer is now able

TEMPERATURE 45dB

–1.5

to select the right product for the application,

0.25

trading dynamic range for size and price,

0

0

–65

–55

–45

–35

–25

–15

–5

5

15

while benefitting from industry-leading

accuracy, temperature stability, and

PIN (dBn)

frequency of operation.

Average VOUT vs. input power AD8319 @ 800MHz lot; slope and

intercept calculated (–40 to –10); temperature (25°C, –40°C, 85°C);

CLPF = 1000pf; TADJ = 500VPOS = 3V

AD8317

AD8318

AD8319

Y o u r

$3.93

$4.99

$2.99

S e m i c o n d u c t o r

10

S o l u t i o n s

R e s o u r c e

Highly Integrated Othello-E™ Quad-Band Radio Transceiver for EDGE, GSM,

and GPRS standards

T

he AD6546 Othello-E transceiver sets new standards for integration and total solution size in EDGE, GSM, and GPRS

radio design. A direct-conversion receiver architecture, closed-loop polar modulation transmitter, and integration of all

critical functions and components reduces layout size and BOM cost while providing state-of-the-art performance with

substantial margin for manufacturing. Othello-E is part of the industry-leading Analog Devices SoftFone® EDGE platform

family, including digital baseband, analog baseband, power management, and

RF blocks.

Othello-E operates in the 850 MHz, 900 MHz, 1800 MHz, and 1900 MHz frequency bands. It includes independent programmable-gain LNAs, separate

high band and low band transmitter outputs, and a fast-locking fractionalN PLL synthesizer with integrated loop filters, Tx and Rx VCOs, and tank

circuits for transmit and receive band local oscillator (LO) generation. The

AD6548 also includes an on-chip crystal oscillator and calibration system,

eliminating a costly external VCTCXO. The closed-loop transmitter architecture simplifies the choice of power amplifier (PA) and improves efficiency

compared to direct-modulation designs requiring linear amplifiers. In addition, the closed-loop system tolerates variations in the PA characteristics

from band to band, and across temperature and manufacturing lots.

AD6546

Contact ADI for details

Fully Integrated Transceiver Delivers Cost-Effective Automatic Meter Reading (AMR) Solution

W

ireless technology offers the prospect of a quantum leap in efficiency for utility companies in the collection of

energy, gas, and water consumption data. Automatic meter reading is a system that will replace manual reading

with networked metering systems. This has reduced labor costs and also enabled some other services that the

utility company can conveniently provide, such as real-time price signalling and remote deactivation of service. A major challenge for this application will be to ensure reliable radio communication in the presence of radiation from an ever increasing

number of wireless devices in other industrial and consumer applications. ADI offers RF transmitter and transceiver ICs and

communication protocol software aimed at meeting these requirements. In addition, the closed-loop system tolerates variations in the PA characteristics from band to band, and across temperature and manufacturing lots.

The ADF7020 transceiver is designed to operate primarily in

the popular ISM (industrial, scientific, and medical) bands at

915 MHz, 868 MHz, and 433 MHz. It supports binary and

Gaussian-filtered frequency shift keying (FSK) and amplitude

shift keying (ASK) modulation schemes at data rates up to

200 kbps. As the functional block diagram at the right shows,

the ADF7020 integrates all of the main RF transmitter and

receiver building blocks into a single chip. This includes a

phase-locked loop (PLL), power amplifier (PA), low noise

amplifier (LNA), channel filter, and a switch to select between

transmit and receive modes of operation. This high level of

integration saves the system designer the extra cost of numerous individual components and simplifies design. For further

information, please visit www.analog.com/transceivers.

RLNA

RFIN

RFINB

RSET

CREG (1:4)

POLARIZATION

LDO (1:4)

ADCIN

MUXOUT

OFFSET

CORRECTION

TEMP

SENSOR

RSSI

MUX

TEST MUX

LNA

IF FILTER

7-BIT

ADC

FSK/ASK

DEMODLATOR

DATA

SYNCHRONIZER

GAIN

OFFSET

CORRECTION

FSK MOD

CONTROL

DIVIDERS/

MUXING

RFOUT

AGC

CONTROL

GAUSSIAN

FILTER

�-�

MODULATOR

TxRx

CONTROL

AFC

CONTROL

INT/LOCK

N/N+1

DIV P

SERIAL

PORT

VCO

CP

PFD

DIV R

VCOIN CPOUT

RING OSC

OSC1 OSC2

CE

DATA CLK

DATA I/O

CLK

DIV

SLE

SDATA

SREAD

SCLK

CLKOUT

Part

Number

Tx/TRx

Frequency Range

(MHz)

Channel Spacing

(kHz)

Receiver Sensitivity

@ 1 kbps (dBm)

Price

($U.S.)

ADF7012

Tx

75 to 1000

N/A

N/A

1.50

ADF7020

TRx

431 to 478, 862 to 956

100

–119

2.20

ADF7020-1

TRx

160 to 600

100

–119

2.20

ADF7021

TRx

431 to 478, 862 to 956

12.5

–127

Contact ADI sales

w

w

w

.

a

n

a

l

o

g

.

c

o

m

/

V

6

11

W

i

r

e

l

e

s

s

High Performance RF/IF Variable Gain Amplifier for Superior Linearity

I

n the design of wireless infrastructure circuits such as those for cellular base stations, designers need

one or more automatic gain control (AGC) loops to optimize the base station dynamic range or need

to add additional gain for optimal signal dynamic range and sensitivity. This is crucial for base station

performance to ensure both weak and strong incoming call signals are effectively handled and maintained.

Maintaining high linearity at higher intermediate frequencies is the main challenge in the design of a variable

gain amplifier (VGA) to employ such AGC loops or to add additional gain in the signal path.

Utilizing ADI’s X-AMP™ architecture, an innovative technique for implementing high performance,

continuous, 34 dB, linear-in-dB, variable gain control, the AD8368 steps up to this challenge by offering exceptional linearity over a broad frequency range for wireless infrastructure applications, such as

the cellular base station radio transceivers. The AD8368 is capable of sustaining high linearity (OIP3

of 34 dBm at 70 MHz), allowing it to be used in all wireless standards, including 2G and 3G, as well as

emerging broadband wireless standards such as 802.16 (WiMAX). With a 3 dB bandwidth of 800 MHz

independent of gain setting, a single-ended input and output drive, and exceptional linearity over the full

operating range, the AD8368 is ideally suited for use in cellular and broadband wireless infrastructure

equipment. Additionally, the AD8368 simplifies and reduces the number of external components required

by integrating an accurate root-mean-square (rms) power detector on-chip, which enables a complete

automatic gain control (AGC) loop within a small 4 mm 4 mm IC package.

OIP3 and NF vs. Frequency

40

Analog Devices, Inc.

Worldwide Headquarters

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

U.S.A.

Tel: 781.329.4700

(800.262.5643,

U.S.A. only)

Fax: 781.461.3113

Analog Devices, Inc.

Europe Headquarters

Wilhelm-Wagenfeld-Str.6

80807 Munich

Germany

Tel: 49.89.76903.0

Fax: 49.89.76903.157

Analog Devices, Inc.

Japan Headquarters

Analog Devices, KK

New Pier Takeshiba

South Tower Building

1-16-1 Kaigan, Minato-ku,

Tokyo, 105-6891

Japan

Tel: 813.5402.8200

Fax: 813.5402.1064

OIP3, NOISE FIGURE (dBm, dB)

35

Analog Devices, Inc.

Southeast Asia

Headquarters

Analog Devices

22/F One Corporate Avenue

222 Hu Bin Road

Shanghai, 200021

China

Tel: 86.21.5150.3000

Fax: 86.21.5150.3222

30

25

20

15

10

5

0

0

100

200

300

400

500

600

700

800

FREQUENCY (MHz)

Purchase of licensed I2C components of Analog Devices or one of its

sublicensed Associated Companies conveys a license for the purchaser

under the Philips I2C Patent Rights to use these components in an I2C

system, provided that the system conforms to the I2C Standard Specification

as defined by Philips.

©2006 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

Inventory Code: WIRELESS-V6-IS6-06

Printed in the U.S.A.

SB06104-XX-6/06

a

Analog Devices, Inc.

600 North Bedford Street

East Bridgewater, MA 02333-1122

Return Service Requested

AD8368

$4.55

w w w . a n a l o g . c o m