The Junction Field Effect Transistor (JFET)

advertisement

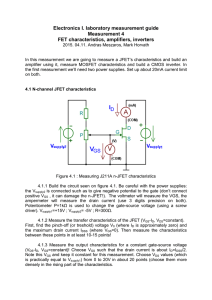

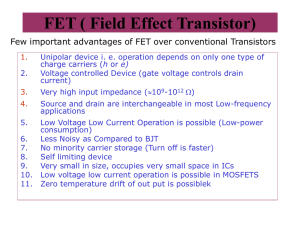

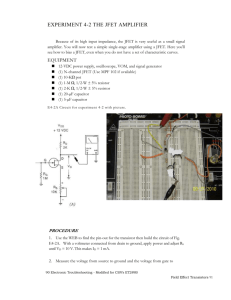

The Junction Field Effect Transistor (JFET) FET ( The Field Effect Transistor) Few important advantages of FET over conventional Transistors 1. Unipolar device i. e. operation depends on only one type of charge carriers (h or e) 2. Voltage controlled Device (gate voltage controls drain current) 3. Very high input impedance (109-1012 ) 4. Source and drain are interchangeable in most Low-frequency applications 5. Low Voltage Low Current Operation is possible (Low-power consumption) 6. Less Noisy as Compared to BJT 7. No minority carrier storage (Turn off is faster) 8. Self limiting device 9. Very small in size, occupies very small space in ICs 10. Low voltage low current operation is possible in MOSFETS 11. Zero temperature drift of out put is possiblek Types of Field Effect Transistors (The Classification) • FET JFET MOSFET (IGFET) Enhancement MOSFET n-Channel EMOSFET p-Channel EMOSFET n-Channel JFET p-Channel JFET Depletion MOSFET n-Channel DMOSFET p-Channel DMOSFET The Junction Field Effect Transistor (JFET) Figure: n-Channel JFET. SYMBOLS Gate Gate Gate Source n-channel JFET Drain Drain Drain Source n-channel JFET Offset-gate symbol Source p-channel JFET Biasing the JFET Figure: n-Channel JFET and Biasing Circuit. Operation of JFET at Various Gate Bias Potentials Figure: The nonconductive depletion region becomes broader with increased reverse bias. (Note: The two gate regions of each FET are connected to each other.) Output or Drain (VD-ID) Characteristics of n-JFET Figure: Circuit for drain characteristics of the n-channel JFET and its Drain characteristics. Non-saturation (Ohmic) Region: The drain current is given by V I DS 2I DSS V 2 P Saturation (or Pinchoff) Region: I DS I DSS V 2 P V GS V P DS and V P V 2 V V V DS GS P DS 2 V 2 V GS DS V V GS P V 1 GS I I DS DSS V P 2 Where, IDSS is the short circuit drain current, VP is the pinch off voltage Simple Operation and Break down of n-Channel JFET Figure: n-Channel FET for vGS = 0. N-Channel JFET Characteristics and Breakdown Break Down Region Figure: If vDG exceeds the breakdown voltage VB, drain current increases rapidly. VD-ID Characteristics of FET Locus of pts where V DS Saturation or Pinch off Reg. Figure: Typical drain characteristics of an n-channel JFET. V GS V P The Transfer (Mutual) Characteristics of n-Channel JFET V I I 1 GS DS DSS V P 2 IDSS VGS (off)=VP Figure: Transfer (or Mutual) Characteristics of n-Channel JFET The JFET Transfer Curve This graph shows the value of ID for a given value of VGS Biasing Circuits used for JFET • Fixed bias circuit • Self bias circuit • Potential Divider bias circuit JFET (n-channel) Biasing Circuits For Fixed Bias Circuit Applying KVL to gate circuit we get V 1 GS I I DS DSS V P 2 VGG I G RG VGS VGS Fixed , I G 0 and 2 V I DS I DSS 1 GS VP and VDS VDD I DS RD Where, Vp=VGS-off & IDSS is Short ckt. IDS For Self Bias Circuit VGS I DS RS 0 I DS VGS RS JFET Biasing Circuits Cont. or Fixed Bias Ckt. JFET Self (or Source) Bias Circuit and I DS I DSS V I 1 GS DSS V P 2 V 1 GS V P V GS R S 2 V V GS I 12 GS DSS V V P P 2 V GS R 0 S This quadratic equation can be solved for V GS & IDS The Potential (Voltage) Divider Bias V I 1 GS DSS V P 2 V G V R GS 0 S Solving this quadratic equation gives V GS and I DS A Simple CS Amplifier and Variation in IDS with Vgs FET Mid-frequency Analysis: VDD A common source (CS) amplifier is shown to the right. RD R1 io The mid-frequency circuit is drawn as follows: • the coupling capacitors (Ci and Co) and the bypass capacitor (CSS) are short circuits • short the DC supply voltage (superposition) • replace the FET with the hybrid-pmodel The resulting mid-frequency circuit is shown below. is ii + vs D ii Rs + vs RTh Ci vi io + gmv rd RD RL vo _ _ mid-frequency CE amplifier circuit s Analysis of the C S m id-frequency circuit above yields: A vi = vo = -g m R 'L , w here R 'L = rd R D R L vi A vs = Zi = vi = R T h , w here R T h = R 1 R 2 ii AI = Zo = vo io AP = = rd R D seen by R L vo = A vi vs io = A vi ii S Zi R s + Zi Zi RL po = A vi A I pi vo R2 RSS _ d vi = v s + + _ g Co G RL + _ VDD CSS _ FET Mid-frequency Analysis: VDD A common source (CS) amplifier is shown to the right. RD R1 io D ii The mid-frequency circuit is drawn as follows: • the coupling capacitors (Ci and Co) and the bypass capacitor (CSS) are short circuits • short the DC supply voltage (superposition) • replace the FET with the hybrid-pmodel The resulting mid-frequency circuit is shown below. is ii + vs RTh vi _ rd io RD RL vo _ _ s mid-frequency CE amplifier circuit Analysis of the CS mid-frequency circuit above yields: A vi = vo = -g m R 'L , where R 'L = rd R D R L vi A vs = Zi vo = A vi vs R s + Zi Zi = vi = R Th , where R Th = R1 R 2 ii AI = Z io = A vi i ii RL Zo = vo io AP = po = A vi A I pi = rd R D seen by R L S vo R2 RSS + gmv Ci RL _ d vi = v s + vs g Co G + Rs + + _ VDD CSS _ Procedure: Analysis of an FET amplifier at mid-frequency: 1) Find the DC Q-point. This will insure that the FET is operating in the saturation region and these values are needed for the next step. 2) Find gm. If gm is not specified, calculate it using the DC values of VGS as follows: gm = 2I I D = DSS VGS - VP VGS VP2 gm = I D = K VGS - VT VGS (for JFET's and DM MOSFET's) (for EM MOSFET's) (Note: Uses DC value of VGS ) 3) Calculate the required values (typically Avi, Avs, AI, AP, Zi, and Zo. Use the formulas for the appropriate amplifier configuration (CS, CG, CD, etc).