RTC-4574SA

advertisement

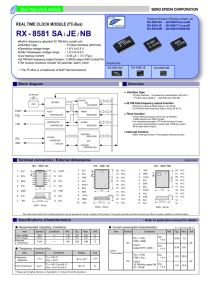

Real time clock module SERIAL REAL TIME CLOCK MODULE RTC-4574SA/JE/NB Product number (please refer to page 2) Q414 5745x000200 Q414 5749xxxxx00 • • • • • • • • • Q4145747x000100 Built-in crystal unit allows adjustment-free efficient operation. Serial interface which can be controlled by three signal lines. Alarm interrupt function for day of week, day, hour, and minute. Timer interrupt function which can be set up between 1/4096 second and 255 minutes . Dedicated interrupt output of the two systems (alarm and regular cycle) which allows software masking. Ability to detect stopping of oscillation and time update. Automatic adjustment for leap year. Wide range of interface voltage and clock voltage between 1.6 V and 5.5 V. Low power consumption at 0.5 µA/3 V. (Typ.) RTC-4574SA RTC-4574JE RTC-4574NB Actual size The details are mentioned in the application manual. http://www.epsondevice.com VIN Input Pin ____ ____ VOUT1 TIRQ,AIRQ Storage temperature VOUT2 FOUT,DATA TSTG Stored as bare product after unpacking Item Symbol Condition Power voltage VDD — Clock voltage VCLK — Operating temperature VOPR No condensation Item Symbol Frequency tolerance ∆f/fo Oscillation start up time Frequency temperature characteristics tSTA Frequency voltage characteristics VDD+0.3 GND-0.3 VDD+0.3 Max. Unit 1.6 5.5 V -40 +85 °C Condition Range Unit Ta=+25 °C, VDD=3 V x 10-6 Ta=+25 °C,VDD=1.6 V 5±23∗ 3 Max. Top Ta=-10 °C to +70 °C, Reference at +25 °C -120 f/V Ta=+25 °C,VDD=1.6 to 5.5 V ±2 x 10-6/ V Ta=+25 °C, VDD=3 V ±5 x 10-6/year Min. Standby current 1 IDD1 Standby current 2 IDD2 VIH VDD=5 V CE0,CE1=GND VDD=3 V DATA , AIRQ, TIRQ VDD — 0.8VDD VIL CE0,CE1,CLK, DATA,FCON pins ILK VIN=GND or VDD -0.5 CE1, CLK FCON pins 1.0 2.0 0.5 1.0 — 0.2VDD 0.5 VDD=3 V 150 300 600 VDD=5 V IOH=-1 mA 4.5 VOH2 DATA,FOUT pins 2.0 VOH3 VDD=3 V IOH=-100 µA DATA,FOUT pins 2.9 VOL1 VDD=5 V RDWN2 VOH1 VDD=3 V VOL3 IOZ IOL=1 mA #%&'% )*+%, #1 #10 7.0±0.3 IOL=100 µA DATA,FOUT pins GND Pin terminal FCON CE1 DATA CLK TIRQ AIRQ CE0 No. 1 2 3 4 5 6 7 8 9 10 No. 20 19 18 17 16 15 14 13 12 11 Pin terminal N.C N.C N.C N.C N.C N.C N.C N.C N.C N.C No. 22 21 20 19 18 17 16 15 14 (13) (12) Pin terminal N.C N.C N.C N.C N.C N.C N.C N.C N.C - 0.15 Pin terminal VDD FOUT CE0 AIRQ TIRQ CLK DATA CE1 FCON GND 0.22 0 Min. 0.65 (0.75) (0.75) V µA #"$%&'%-,(SON 22-pin) kΩ 6.3 Max. #14 #%&'% 3.0 )*+% V #1 GND+0.8 0.5 GND+0.1 GND+0.25 IOL=1 mA AIRQ, TIRQ pins VDD=3 V VDD=5 V VOUT=GND or VDD, DATA , AIRQ, TIRQ pins µA #22 GND+0.5 No. 14 13 12 11 10 9 8 6.2 Max. 5.0 — DATA,FOUT pins VOL2 VOL5 #11 VDD+0.3 300 Pulldown R2 Output leakage current #20 0.05 Min. 0.6 Max. Unit 150 VDD=5 V 1.2 1.27 Pin terminal GND FOUT N.C N.C N.C N.C VDD 0° to 10° #"$%&'%((VSOJ 20-pin) x 10-6 75 RDWN1 VOL4 0.35 s CE0 pins VIN=VDD Pulldown R1 Output voltage 2 GND-0.3 Typ. #7 10.1±0.2 (GND=0 V, VDD=1.6 V to 5.5 V,Ta=-40 °C to +85 °C) Condition Output voltage 1 81 +10 Symbol Input leakage current #1 Min. Aging fa ∗ Please ask tighter tolerance. Input voltage °C +125 -55 Item #%&'% )*+ % V +8.0 No. 1 2 3 4 5 6 7 1.3 1.5 Max. Output voltage +7.0 5.0 Input voltage -0.3 (Unit: mm) (SOP 14-pin) #8 7.4±0.2 VDD to GND #14 3.1 3.2±0.1 VDD #"$%&'% Unit Max. 5.4 Supply voltage Min. 4.8 Condition 5.0±0.2 Symbol #11 0.2 1.3 ±0.1 Item !" No. 1 2 3 4 5 6 7 8 9 10 11 Pin terminal GND FCON N.C CE1 DATA CLK TIRQ AIRQ CE0 FOUT VDD GND+0.4 -0.5 0.5 µA Metal may be exposed on the top or bottom of this product. This won't affect any quality, reliability or electrical spec. Real time clock module Register table Register symbol bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 0 Sec fos S40 S20 S10 S8 S4 S2 S1 1 Min fr Min40 Min20 Min10 Min8 Min4 Min2 Min1 2 Hour fr 0 Hour20 Hour10 Hour8 Hour4 Hour2 Hour1 3 Day of Week fr W6 W5 W4 W3 W2 W1 W0 4 Day fr 0 Day20 Day10 Day8 Day4 Day2 Day1 5 Month fr 0 0 Month10 Month8 Month4 Month2 Month1 6 Year Year80 Year40 Year20 Year10 Year8 Year4 Year2 Year1 A-Min1 Address A-Min10 A-Min8 A-Min4 A-Min2 A-Hr20 A-Hr10 A-Hr8 A-Hr4 A-Hr2 A-Hr1 A-W6 A-W5 A-W4 A-W3 A-W2 A-W1 A-W0 AE ∗ A-Day20 A-Day10 A-Day8 A-Day4 A-Day2 A-Day1 FOUT control FE ∗ FD4 FD3 ∗ FD2 FD1 FD0 C Timer interrupt control TE ∗ TD1 TD0 ∗ ∗ ∗ ∗ D Count Down Timer Timer128 Timer64 Timer32 Timer16 Timer8 Timer4 Timer2 Timer1 E Control 1 0 0 0 TI/TP AF TF AIE TIE F Control 2 0 TEST STOP RESET HOLD 0 0 0 7 Minutes Alarm AE A-Min40 8 Hours Alarm AE ∗ 9 Week Alarm AE A Day Alarm B A-Min20 0 : Always set this bit to“0”. AC characteristics Item Symbol Control CLK clock cycle tCLK CLK H Pulse Width tWH CLK L Pulse Width tWL CE setup time tCS (GND=0 V,Ta=-40 °C to +85 °C) VDD=3.0 V±10 % VDD=5.0 V±10 % Min. 400 — tCH CE recovery time tCR 600 Write data setup time tDS 100 Write data hold time tDH 80 Write data disable delay time tWZ Read data delay time tRD Rise and fall time tRF FOUT duty ratio (32.768 kHz output) Duty Max. Unit 350 — 50 % RL=10 kΩ 175 35 Data Write DATA 120 — 65 DATA 50 40 50 % tDS tDH D0 10 % tCLK D1 D6 D7 D0 D6 D7 (Write data) tWZ tRZ tRD D0 D1 D6 D7 (Setup code, setup address) D0 D6 D7 90 % 10 % (Read data) From here the DATA pin turns into the output mode. % 60 tCR 90 % Data Read 100 tCH tRF tRF (Setup code, setup address) 0 100 — ns 50 200 tWH tWL — 300 — tCS CLK 300 0 CL=50 pF CL=50 pF tRZ Min. CE CE hold time Output disable time Max. 800 Timing chart Block diagram 32.768 kHz OSC FOUT FCON TIRQ AIRQ Control line Divider Clock and Calendar Output controller Timer register Interrupts controller Alarm register DATA Control register CLK CE1 CE0 Bus interface circuit Shift register 82